DDS的觸發抖動引起IQ相位突跳的研究

(海軍裝備部駐上海地區軍事代表局,上海 200083)

0 引言

隨著雷達技術的發展,線性調頻信號已經廣泛應用于高分辨率雷達領域。直接數字頻率合成(Direct Digital Synthesizer,DDS)是現代雷達特別是合成孔徑雷達(Synthetic Aperture Radar,SAR)獲得線性調頻信號的主要方法[1-2]。DDS技術的優點在于相對帶寬寬、轉換時間短、頻率分辨率高、輸出相位可連續等方面。而隨著DDS系統時鐘的不斷提高,DDS 觸發信號的微小抖動都會導致發射信號的相位突跳,它破壞了相參雷達的相參性,相當于對發射信號添加了一種隨機的二相調制,導致接收的IQ 解調信號相位突跳,影響雷達動目標的檢測和SAR成像[3-4]。本文將對此問題作深入的分析,并給出相應的解決方法。

1 DDS技術和雷達基帶信號產生的基本原理

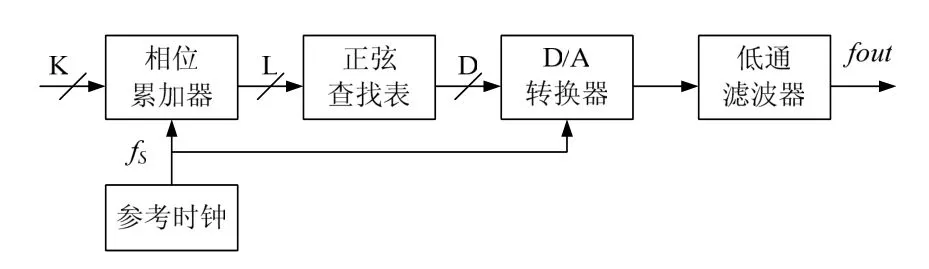

直接數字頻率合成(DDS)的基本原理是利用采樣定理,通過查表法產生波形。DDS 主要由相位累加器、正弦查詢表、D/A轉換器、低通濾波器和參考時鐘5個部分組成,如圖1所示。

圖1 DDS 原理框圖

相位累加器在每一個時鐘沿與頻率控制字K 累加一次,當累加器大于2N時,相位累加器相當于做一次求模取余運算。正弦查找表ROM 在每一個時鐘周期內,根據送給ROM的地址取出ROM 中已存儲的相對應的正弦幅值(二進制碼);然后將該數值送給D/A轉換器變換為模擬量;最后經過低通濾波器濾去高頻分量,得到較純凈的正弦波。目前,DDS的實現方法有兩種:一種利用專用的DDS 芯片來實現,典型的DDS 集成芯片如美國AD 公司生產的AD985x系列產品,參考時鐘從幾十MHz 到1 GHz;一種利用通用的FPGA 器件進行專門設計[5]。在雷達設備中通常采用第一種方法。

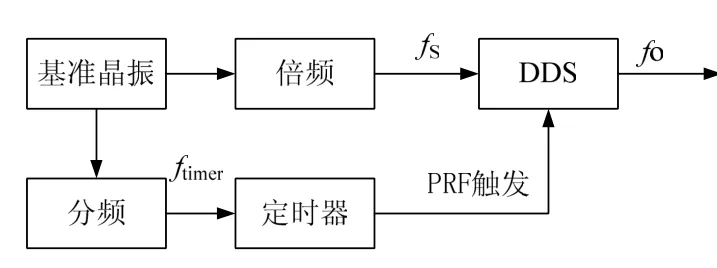

應用DDS技術來產生雷達基帶信號的原理如圖2所示。

圖2 雷達基帶信號產生原理

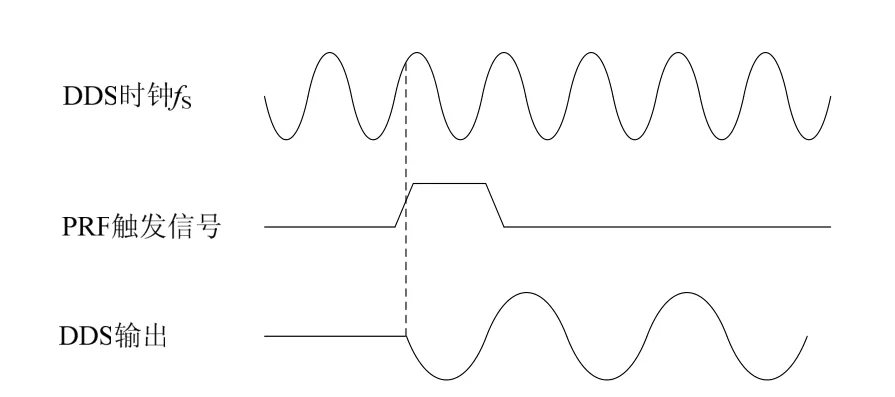

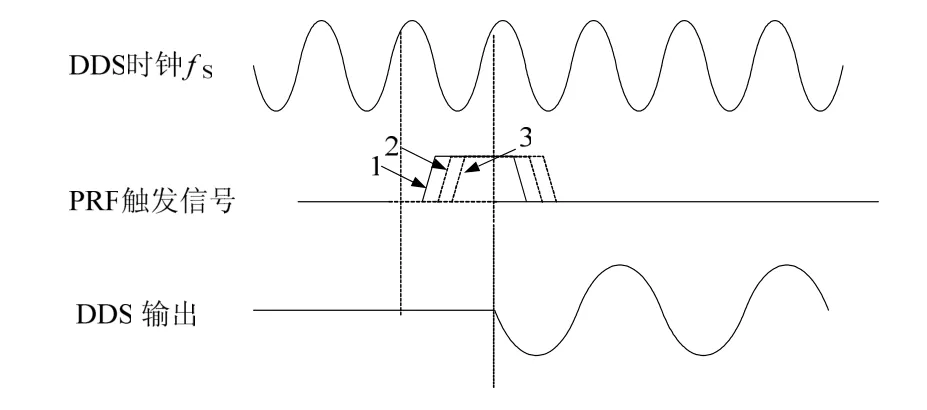

由圖2可以看出,雷達的相參基準源是一高穩定度的晶振,它的一路輸出倍頻后作DDS的系統時鐘fS;一路輸出分頻后送定時器作基準時鐘ftimer,由定時器輸出PRF 觸發信號去觸發DDS 電路產生相應的雷達波形。DDS 工作的時序如圖3所示,圖3中,在觸發之后可以立即輸出波形。實際上,大多數DDS 器件在觸發信號和輸出之間存在一定的延遲[5-6]。但是這個延遲時間是固定的,因此這里不予考慮。

圖3 DDS 工作時序圖

如果DDS的系統時鐘fS和定時器的基準時鐘ftimer是整數倍的關系,則因為是來自同一個基準源,所以fS的上升沿和PRF 觸發脈沖的前沿通常是對齊的。

2 PRF 觸發信號抖動引起DDS 輸出的相位突跳

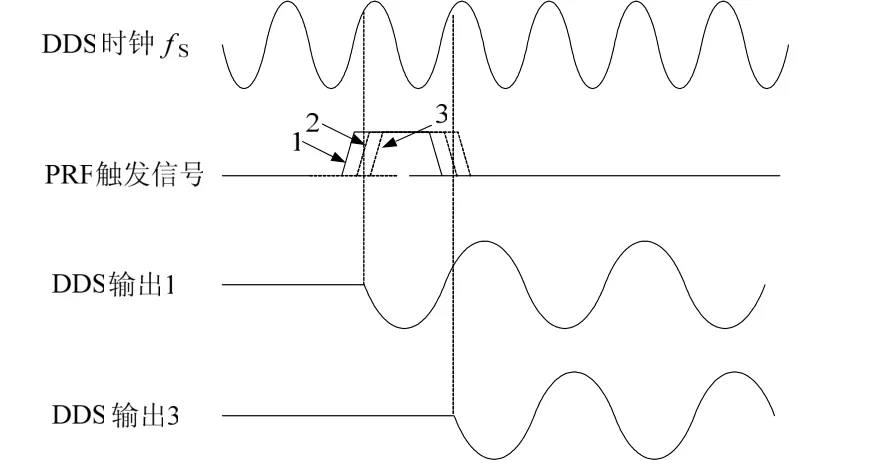

在實際電路中,PRF 觸發信號在分頻整形和長線傳輸后前沿的抖動是難以避免的,即使這種抖動較小,但只要滿足特定條件,也會引起DDS 輸出信號的相位突跳,如圖4所示。

圖4 PRF 觸發信號抖動引起兩個DDS 輸出

DDS 芯片在每個系統時鐘讀取觸發信號的狀態,當判斷觸發信號出現上升沿后,在DDS系統時鐘的下一個上升沿開始按照新裝訂的參數產生輸出信號。如圖4所示,當PRF 觸發信號的上升沿超前DDS系統時鐘fS的上升沿一定時間時,輸出波形為DDS 輸出1,當PRF 觸發信號的上升沿落后DDS系統時鐘fS的上升沿一定時間時,輸出波形為DDS輸出3。由于抖動的影響,PRF信號的上升沿在1和3 之間隨機變化,因而DDS的輸出波形也在隨機跳變。

對于DDS 輸出為點頻的情況,DDS 輸出1 和DDS 輸出3 之間的相位突跳?θ可以由公式求出:

?θ=2πfO/fS。

根據奈奎斯特定理,DDS的輸出頻率不會超過1/2系統時鐘,故DDS的觸發抖動造成的相位突跳小于180°。

隨著DDS的系統時鐘頻率不斷提高,觸發脈沖抖動的影響越來越大。目前集成的DDS 芯片的工作時鐘已經到了1 GHz 以上,這種現象出現的幾率大大增加。

在雷達系統中,DDS 輸出的基帶信號,經過上變頻、倍頻等中間過程后,變換到發射信號,再經發射機放大后通過天線輻射出去,基帶信號的相位突跳必然帶來發射信號的相位突跳;回波信號送到接收機,因為發射和接收為同一個基準參考源,所以接收是相參的,回波信號經過下變頻和IQ 解調后的視頻信號的相位也是突跳的。

這種現象對發射信號添加了一種隨機的二相調制,這樣就破壞了相參雷達嚴格的相參性要求,并且會對雷達的相參積累和目標檢測產生影響[4]。不僅如此,這種現象還使得來自同一個目標的雷達回波相對于PRF的延遲時間出現抖動,從而會影響對目標距離的精確測量。雷達的距離分辨率和測量精度越高,這種抖動的影響越大。因此,對于距離分辨率很高的SAR 而言,解決好抖動問題,關系重大。

3 相位突跳的實驗研究

通過上面的討論,基本清楚了DDS的觸發信號的抖動是如何導致基帶信號的相位突跳,并最終引起接收的IQ 檢波信號的相位突跳的。然而實際工作中,IQ信號出現相位突跳呈現無規律性。為了進一步證實就是DDS 觸發信號的抖動造成的IQ相位突跳,必須結合上述理論分析進行實驗驗證。

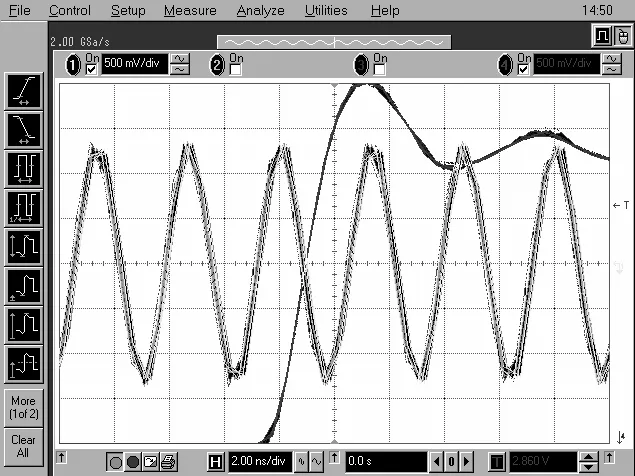

在實驗中,用示波器監測觸發脈沖、DDS時鐘、IQ 輸出,通過調整觸發脈沖的輸出延時,使得脈沖前沿的抖動處于或者不處于DDS時鐘信號的上升沿,如圖5和圖6所示。正如前面所分析的那樣,IQ 輸出相位突跳有時頻繁出現,有時完全消失。

圖5 有IQ相位突跳時

通過上述實驗基本肯定了:IQ相位的突跳正是由于DDS 觸發脈沖的抖動與DDS時鐘時序引起的。

上述實驗也提供了解決問題的線索。由圖5和圖6顯然可以看出,DDS 觸發脈沖的前沿抖動相對于DDS時鐘周期是很小的,只要將DDS 觸發脈沖和DDS時鐘的相對延時作合適的調整就可以了,延時哪一個信號都是可行的。為此選擇將定時器送來的DDS 觸發脈沖在進入DDS 芯片之前作適當的延時。

但是,實際操作中存在以下問題:即實際的DDS 觸發脈沖和DDS時鐘的相對延時關系和用電纜、探頭測試時在示波器上顯示的并不一致,尤其在DDS時鐘頻率很高的時候會相對偏差更大。從上面所做實驗中保存下來的兩幅圖就很明顯的看出,示波器顯示的似乎和理論分析的情況剛好相反。這當然只是一種巧合,因此要避開這個問題。

繼續上面的實驗:通過調整脈沖延時,找到相位抖動最嚴重的時序圖后,以它為參考,在同樣的條件下(即使用同樣的電纜和探頭,監測同樣的測試點),觸發脈沖更換為定時器提供,將其前沿調整到時序圖中的相對位置再延時1/2個DDS時鐘周期。(要注意的是:示波器上顯示的時序關系可能和實際的剛好相反,如圖5和圖6所示,這也是找參考時序圖的原因)。

經過調整DDS 觸發脈沖的延時后,分機在多次實驗都未出現IQ相位突跳的問題。

4 實驗結果分析

實驗結果表明,如果PRF 觸發信號與DDS時鐘的時序關系不合適,則會引起發射的LFM信號和接收機輸出的IQ信號的相位突跳。而通過調整PRF 觸發信號相對于DDS系統時鐘的延遲,完全可以避免此現象的出現。

理論上,使PRF 觸發脈沖的上升沿處于DDS系統時鐘兩個相鄰上升沿的中間位置(相位相差180°),允許的PRF 抖動范圍最大,如圖7所示。在這種情況下,只要PRF 抖動小于1/2個DDS系統時鐘,就完全可避免相位突跳的產生,得到穩定的輸出信號。這也意味著,在電路設計上,必須避免PRF 脈沖由于阻抗匹配不好而失真過大,并且盡量減少疊加在PRF 和DDS時鐘信號上的隨機噪聲。

圖7 PRF 觸發信號與DDS時鐘的最佳相位關系

首先,這種正確的時序關系需要依靠DDS 控制電路的設計來解決;其次,在DDS時鐘頻率高達GHz級下,PCB 走線的長度影響很大,因此對PCB設計也提出越來越高的要求;另外,系統裝配、連線的離散性、芯片延遲時間的不確定性、噪聲和工作溫度都可能影響觸發信號上升沿的波形和延遲時間,從而對時序關系產生影響。這些不確定性因素不能僅依靠設計解決,而必須通過試驗來精確測量。

進行試驗測量時,線纜的長度、測量點位置的選擇都會引起信號的延遲。因此,示波器上顯示的信號相位關系可能與DDS 芯片內部的信號相位關系不同有關。首先,找到相位跳變最嚴重時的延遲時間T0,這相當于圖4中的相位關系;然后,調整PRF 脈沖的延遲時間與T0相差1/2個DDS系統時鐘周期,超前或落后均可,得到相當于圖7的相位關系,從而有效地避免PRF 脈沖前沿抖動的影響。

5 結論

隨著DDS系統時鐘頻率的不斷提高,如果DDS觸發信號的抖動超出了DDS 工作時鐘的上升沿,就可能出現發射信號在脈沖之間存在相位突跳,最終導致接收的IQ相位突跳。解決的辦法是將DDS系統時鐘信號或者觸發脈沖做適當的延時,使得觸發脈沖信號的前沿落在DDS系統時鐘的兩個上升沿中間,只要保證觸發脈沖前沿的抖動不超過DDS系統時鐘的一個周期,就可以避免突跳。因為DDS觸發脈沖和DDS時鐘的傳輸延時受到多種因素的影響,無法準確預測,所以在具體的電路設計中,可以在這兩個信號的通路上預先加入延時電路,以便在生產階段將時序調整到最穩定的狀態;另外,在滿足設計要求的情況下應該盡量降低DDS時鐘的工作頻率。

[1]MERRILL I SKOLNIK.雷達系統導論[M].3 版.北京:電子工業出版社,2006:549-562.

[2]WU Y,LI J.The design of digital radar receives[J].Proc.IEEE National Radar Conf.1997,34(2):207-210.

[3]DAVIDSON W,WONG F H,CUMMING I G.The effect of pulse phase errors on the chirp scaling SAR processing algorithm[J].IEEE Trans.on Geosciences and Remote Sensing,1996,34(2):471-478.

[4]周健.雷達頻率源中DDS的觸發抖動對目標檢測的影響[J].電子工程師,2004,30(4):4-6.

[5]張冬梅,楊建宇,熊金濤.基于FPGA 實現DDS技術的雷達波形產生器的設計[J].現代電子技術,2005,195(4):103-105.