基于FT245BM的數據采集系統設計與實現*

石波涌 應文威 蔣宇中

(92665部隊1) 常德 415000)(海軍工程大學2) 武漢 430033)

1 引言

如今,隨著信息技術的迅速發展,數據采集和處理技術廣泛應用于雷達、通信、遙測、遙感等領域。在早期計算機通常采用串口或并口傳輸大量的數據,占用了非常客觀的系統資源,同時數據的傳輸速度也受到了極大的制約。傳統的接口通常采用PCI總線或者是RS-232總線。PCI總線有較高的傳輸速率,可達132Mbit/s,也可以即插即用,但是它們的擴充槽有限且插拔不方便:RS2232串行總線連接比較方便,但是傳輸速率過低,不易用于高速傳送數據和傳送大量數據。USB在這一背景下應運而生。USB具有終端用戶的易用性、應用廣泛性、同步傳輸帶寬、靈活性、健壯性、與PC產業的一致性和成本低廉等特點,使其迅速在市場中流行[1]。

FT245BM是FTDI(Future Technology Devices IntlLtd)公司的多種快速USB通信接口解決方案之一。不同于市面上的其他一些產品,如Cypress公司的EZ-USB系列芯片,FT245BM的開發難度較低,大幅縮短了開發周期,且價格低廉。它無需編寫片內固件程序,上層PC機則使用FTDI公司提供的官方驅動程序。FT245BM芯片的主要功能是在內部硬件邏輯的作用下實現USB串行數據格式與并行數據格式的雙向轉換。PC機通過USB接口與FT245BM進行數據交換,F T245BM則通過并行方式與下位微控制器通信。因此FT245BM有很大的優越性。同時為了提高數據的采集性能,考慮到FPGA所具有的速度優勢,因此采用高速FPGA控制AD采集外部數據,并通過與FT245BM的交互將數據上傳。

2 系統設計

2.1 整體設計

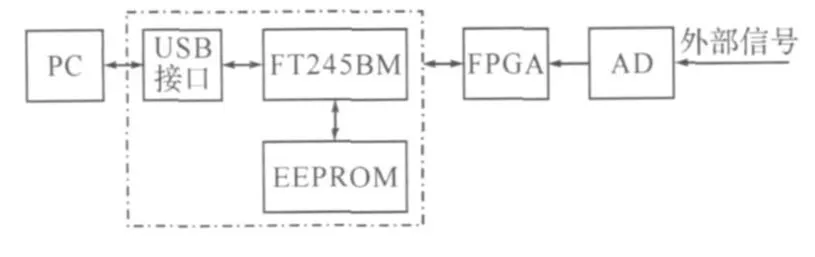

如圖1所示,為本文設計系統的整體框圖。上層的PC機通過FT245BM與FPGA進行通訊,接收AD采樣的外部信號。整個設計包括PC機的設計模塊,FT245BM設計模塊和FPGA的設計模塊。PC機的設計模塊主要實現一個人機交互軟件,其功能包括界面的顯示,對FT245BM的開關和讀寫控制,以及對數據流的控制等功能。FT245BM設計模塊實現FPGA與PC機的連接。一方面通過USB接口直接與PC機相連,與PC機進行交互:另一方面直接與FPGA相連,通過控制引腳控制數據的傳輸。FT245BM附接一片EEPROM,用于存儲FT245BM 設備參數信息。FPGA設計模塊通過設定的采樣速率,將AD采樣得到的數據向上傳輸,到達PC機。

鑒于精度與價格的權衡,AD采用TLC5510A芯片。T LC5510A使用 semiflash工藝,是一款CMOS,8位,20MSPS模擬數字轉換器(ADCs)。T LC5510A使用單 5V電源供電,通常只有130mW的功耗。包括內部采樣保持電路,并行輸出高阻抗模式和內部參考電阻。semiflash工藝降低了功耗,與閃存轉換器相比體積更小。

圖1 系統整體框圖

2.2 FT245BM設計模塊

FT245BM內部主要由USB收發器、串行接口引擎(SIE)、USB協議引擎和先進先出(FIFO)控制器等構成[2]。USB收發器提供 USB1.1/2.0的全速物理接口到USB總線,支持UHCI/OHCI主控制器;串行接口引擎主要用于完成USB數據的串/并雙向轉換,并按照USB1.1規范來完成USB數據流的位填充/位反填充,以及循環冗余校驗碼(CRC5/CRC16)的產生和檢錯:USB協議引擎管理來自USB設備控制端口的數據流:FIFO控制器處理外部接口和收發緩沖區間的數據轉換。FIFO控制器與微控制器(如DSP等)的接口主要通過8根數據線D0~D7及讀寫控制線(WR和RD#)來完成。FT245BM內含一個128字節的接收緩沖區和一個384字節的發送緩沖區,均用于USB數據與并行I/O口數據的交換。

FT245BM與EEPROM相連,EEPROM的主要用途是定制USB設備的VID,PID,Serial Number,Product Description String等。但即使沒有 EEPROM FT245BM也能正常工作,只不過自動將設備描述符等設置為默認。其中FT公司默認的VID是0x0403,這個VID也是給開發者調試所用。EEPROM通過FTDI公司的應用軟件可以進行擦寫。

設計的F T245BM硬件電路采用總線供電模式,同時采用上電復位的方式,不設置從機的復位方式。時鐘電路采用一個 6MHz的晶體及兩個56pF電容組成。電源端增加了去耦和旁路電容以提高電路的抗干擾性能。在PCB板的設計中,數據的走線短并且長度大致相等。D0~D7為雙向數據端口,RD#、WR、TXE#、RXF#為控制數據讀寫的邏輯管腳,這兩組管腳均與FPGA相連。USBDP與USBDM與USB接口電路中的D-,D+相連,以實現同 USB接口的正常通信。EECS,EESK,EEDATA與EEPROM相連。其中EECS選通EEPROM的工作與否,EESK是EEPROM的時鐘信號接口,EEDATA是傳輸數據接口。

FT245BM的設計中最重要的是對控制時序的掌握,對時序的控制好壞直接影響了數據傳輸的性能。FT245BM讀時序為,當RXF#為低,表示當前FIFO接收緩沖區內有數據,可以執行讀操作讀取接收緩沖區數據。在RD#電平由高變低,FIFO控制器將接收緩沖區中的數據輸出到8位數據端口上,微控制器此時只需讀取I/O口就可以將數據取到內部數據總線上來,再將RD#信號拉高完成1個字節數據的讀取。當將FIFO接收緩沖區中的數據全部取出后,RXF#被拉高表示數據為空。在RXF#為高時,禁止從FIFO接收緩沖區讀取數據。

FT245BM 寫時序為,當 TXE#為低,表示當前FIFO發送緩沖區空,可以向發送緩沖區寫入數據。在WR為高電平時,微控制器將8位數據D[0…7]送到并行I/O口上,在WR信號電平由高變低時數據被寫入發送緩沖區中。當TXE#為高時,表示當前FIFO發送緩沖區已滿或者正在寫入上一個字節,此時禁止向發送緩沖區中寫入任何數據。微控制器向FT245BM寫入數據時應確保TXE#為低。

2.3 FPGA設計模塊

FPGA采用Altera公司CycloneⅡ系列產品中的EP2C5。它采用90nm工作制作,工作電為壓1.2V,內部具有兩個鎖相環,4068個 LE單元,26個M4K型RAM塊,總RAM容量達119,808位。EP2C5T144C8的I/O口達142個,最高工作頻率達250MHz,是一款高性價比的FPGA產品。

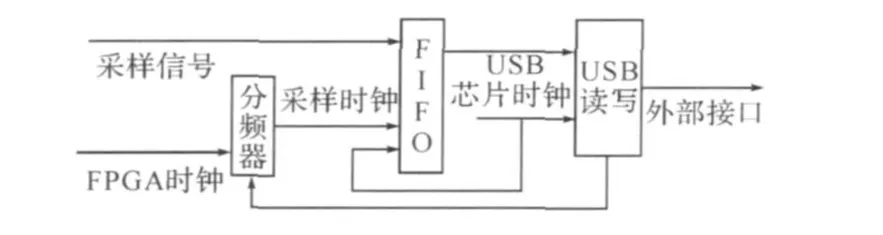

圖2 FPGA算法結構

如圖2所示為FPGA設計模塊的算法結構,分頻器將FPGA時鐘進行分頻產生采樣時鐘,以達到我們要求的采樣速率。采樣時鐘驅動FIFO讀取采樣信號,USB讀寫器一方面判斷FIFO滿足特定要求后,通過外部接口向上傳輸數據,另一方面接收PC向下傳輸的數據,用于配置分頻器的系數,改變采樣頻率。分頻器的設計較簡單,內部有一個累加器進行循環累加,根據配置的分頻器系數,輸出采樣時鐘[4]。

FIFO的設計采用Altera帶有的免費的IP core,在QuartusⅡ軟件平臺下,通過Megawizward向導產生8×2048位的FIFO。FIFO產生的重要引腳有wrclk(寫信號),rdclk(讀信號),rdreq(讀請求信號),wrreq(寫請求信號),rdempty(讀空間空標志),wrempty(寫空間空標志),wrfull(寫空間滿標志),rdfull(讀空間滿標志),wrusedw(寫空間可用數據),rdusedw(讀空間可用數據)。將Megawizward產生的FIFO進行封裝,fifo_read_i指示USB讀寫處理器請求數據,fifo_read_o表示當前FIFO準備好輸出數據。fifo_read_o信號由三個信號確定,當reset信號產生時置零:當 rdusedw[10]為 1,即至少有1024個數據時置1:當fifo_read_o信號為1且rdempty為1時置0,即數據讀完。FIFO的寫時鐘采用FPGA的時鐘,為50MHz,而讀時鐘則采用FT245BM 芯片的時鐘6M。

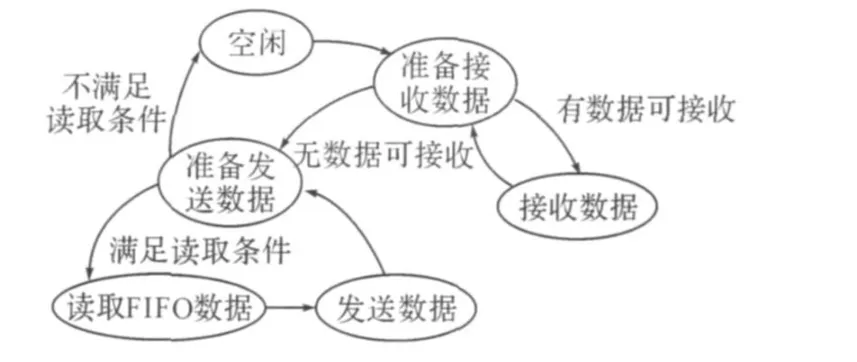

USB讀寫器內部由一個狀態機實現,完成兩個功能。一個功能是判斷FT245BM是否有向下的數據,若是則將數據接收過來配置給分頻器。另一個功能是判斷FPGA中的FIFO是否滿足要求,若是則讀取數據向上傳輸,直到將內部的FIFO讀空。

如圖3所示,為USB讀寫器的狀態機。當狀態機處于空閑狀態時,檢測F T245BM接收緩存中是否有是數據,若有,則將數據接收,作為分頻器的分頻系數:否則跳出狀態,檢測FPGA內部FIFO緩存是否滿足條件。若是,則讀取緩存區中的數據直到將FIFO緩存讀空,讀空后自然不滿足讀取條件,跳到空閑狀態:若緩存區不滿足條件直接跳到空閑狀態。

圖3 USB讀寫器狀態機

2.4 上層機軟件設計

USB設備插入PC機時操作系統會請求安裝設備驅動程序,FTDI公司為基于FT245BM的USB接口設備提供了VCP、D2XX(動態鏈接庫)兩種驅動程序。選擇不同的驅動程序,PC機端軟件設計方法也不同。

選擇安裝VCP驅動程序時,操作系統將基于FT245BM的USB接口設備虛擬成為串行通信口,對這一虛擬的串行口的操作就等同于對該USB接口設備的操作,因此在應用程序中可以利用串行通信控件來簡化PC機端軟件的設計。目前比較成熟的串行通信控件有MSCOMM、SPCOMM、PCCOMM等[3]。但是根據FTDI公司提供的資料上看VCP的數據傳輸數率只能達到300kb/s。因此,軟件的設計是基于FT245BM的第二種設計思路,即利用D2XX來設計。

選擇D2XX作為USB接口的設備驅動程序,應用程序通過 FTD2XX.DLL、FTD2XX.SYS、Window s USBDriver Stack來實現對FT245BM的讀寫。因此,在程序編寫時只需調用FTD2XX.DLL中的函數,便可完成對USB接口設備的讀寫操作。FTD2XX.DLL提供了豐富的接口函數來訪問FT245BM。主要函數簡介如下:

FT_ListDevice:獲取當前PC機上連接的所有的FTDI USB接口設備的信息:FT_Open,FT_OpenEx:打開FTDI USB接口:FT_Read:從FTDI USB接口讀取數據:FT_Write:向FTDI USB接口寫入數據:FT_Close:關閉FTDI USB接口:FT_SetTimeOut:設置讀寫延時時間大小:FT_GetDeviceInfoList:獲取USB設備的列表:FT_GetDeviceInfoDetail:獲取某個USB設備的詳細信息:FT_GetStatus:獲取FT245BM中接收緩存和發送緩存的大小。以上函數是一些基本函數,另有其它功能的函數不一一列舉。總之,D2XX提供的函數齊全,不僅包括對FT245BM芯片的操作,數據流控制,而且還能對EEPROM進行操作,例如能對EEPROM進行讀寫,擦除等。EEPROM內可存儲了FT245BM產品的詳細信息,通過FT公司自帶的軟件MProg 3.0a,可以將一些USB設備的基本參數下載到EEPROM中。

在軟件的設計中,選用的開發平臺為VC++6.0。為了使界面美觀大方,設計庫選用了微軟提供的MFC。設計中增開了一條線程,用于讀取USB口的數據,并將數據輸出顯示在程序界面中。當然由于數據采集量大,若是完全顯示對于系統資源的消耗過大,因此顯示的策略是每隔50ms顯示一次,并采用雙緩存圖形顯示技術[5],消除圖形顯示的抖動,使得顯示的效果更好。同時程序還附帶完成對USB上傳速率性能的測試。

3 USB性能測試

在本文設計的采集系統中,無論在AD采集還是FPGA內部算法,都不會成為系統采樣速度的瓶頸。一方面原因是所采用AD芯片的轉化速率為20MSPS,高于FT245BM 電路的時鐘6M:另一方面原因在于FPGA具有的高速并行的特點,在系統中采用的時鐘頻率為50M,這是能夠滿足要求的。因此,采集系統傳輸性能的瓶頸在FT245BM上。所以,對F T245BM性能的測試能反應出整個采集系統的傳輸性能。

測試FPGA上傳數率的測試,FPGA以不間斷的發送模式向上位機發送數據,上位機同時檢測數據的正確性,錯誤則此時數據發送無效。數據格式為相鄰數據位反。發送數據的單位為Byte,發送的數據大小模式有100Byte,500Byte,1kByte,5kByte,8kByte,10kByte。計算機向FT245BM設備發送一個開始字符,該字符同時選定了發送數據大小的模式,FPGA正確收到有效字符之后,發送該模式大小的數據包,計算機接收并檢測其有效性。時間的測量在發出開始字符后開始計時,直到接收到預定大小的數據包。在上層機中,通過使用機器指令 RDTSC(Read Time Stamp Counter)來讀取CPU的時間戳實現時間的測量,其可達到納秒級的計時精度。

在下層的FPGA中,對設計進行略微的修改。為了使得測試數據的可控,在FPGA內部,斷開與FIFO之前的連接,代之以一個信號源控制器。該信號源控制器的數據格式為相鄰數據反相。一開始,FPGA處于等待狀態,查詢到FT245BM有數據時,通過控制引腳狀態來接收數據。通過預先定義了一組數據標志代表發送不同大小的數據包。若接收數據為預先定義的模式標志,則進入發送狀態,發送數據直到發送完所有預定的數據。

表1 發送數據速率表(Kbyte/s)

表1為發送數據速率表。根據上述的數據結果顯示,在數據傳輸中,數據包尺寸較小的情況下,發送數率不大,速率大小也不穩定,而發送的數據包尺寸較大時,速率趨于恒定,一般能達到1Mbps以上。數據的發送同系統的繁忙程度有一定得聯系,因為Windows是基于多線程的操作系統,對于不同的優先級的進程分配不同的資源和效率,系統越繁忙,發送數據的速率也越慢。因此,測試表明系統的傳輸性能應該在1.5M以上。

4 調試與結果

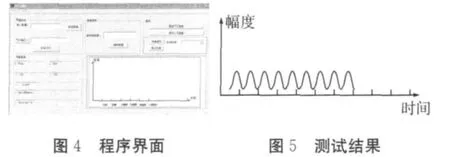

如圖4所示,為設計軟件的程序界面圖。左下角的顯示框內顯示當前設備的信息,包括Flag,Type,Vendor ID(生產廠商 ID)和Product ID(產品ID),LocID,Serial Number,Description。在右上角有采集波形,停止采集按鈕,主要完成對數據的采集工作,接收從FPGA上來的數據。通過采樣間隔下拉選框,我們可以設置采樣頻率,共有5個可選的頻率,分別為50K,1K,10K,100K,1M。

測試條件為溫度21℃,大氣壓0.1Mpa,采樣間隔為500kHz。外部信號峰峰值(Vp-p)2V,頻率為40kHz,偏移2V。在打開設備之后,點擊“采集波形”,波形顯示如圖5所示。結果表明,采樣效果良好,穩定,滿足我們的要求。

5 結語

系統設計包括FT245BM設計模塊,FPGA的設計模塊和PC機的設計模塊。F T245BM模塊主要完成PC機和FPGA的通信。FPGA的設計模塊負責采樣外部信號,并與USB芯片進行交互。PC機的設計基于F TDI公司開發的D2XX驅動和Microsoft公司支持的MFC類庫,利用VC++開發軟件設計圖形界面,具有很高的友好性和互動性。測試方案證明,本采集系統的實時傳輸速率可達到1.5MBps以上。

本系統以FT245BM芯片為中介,完成PC機與FPGA的交互,控制FPGA采集外部信號。結果表明該系統,安全可靠,高速穩定,達到了實用要求。

[1]林秀珍,梁志強.通用串行總線USB及其應用[J].現代電子技術,2003(7)

[2]FT245BM data sheet.Future Technology Devices Intl.Ltd,2005:1~24

[3]徐鋒.基于FT245BM的快速USB接口的實現[J].電子工程師,2007(3)

[4]諸振勇,翁木云.FPGA設計及應用[M].西安:西安電子科技大學出版社,2002:112~207

[5]Julio Sanchez.Windows圖形編程[M].羅駿,等譯.北京:清華大學出版社,2000:15~17