分段供電開關的狀態監測系統設計*

胡練武 江漢紅 芮萬智 王 潔

(海軍工程大學電氣與信息工程學院 武漢 430033)

1 引言

在高速磁懸浮列車和其他高速直線推進系統中,動力沖程一般較長。為提高電機效率、降低輸入容量,需采用分段供電網絡形式,通過分段供電開關控制直線電機各段初級(定子)串連分段運行。此類高速直線推進系統一般工作于高電壓和強電流下,且分段供電的切換開關需頻繁通斷,故工程上通常采用無觸點的雙向可控硅交流開關(即晶閘管組件,包含正反2個晶閘管)作為各段初級繞組的開關器件。高速直線推進系統中,直線電機有三相繞組,每相的長初級被分成多段,這樣,會存在大量的晶閘管開關組件。而它們的性能狀態將直接影響到高速直線推進系統運行的可靠性。因此,對分段供電開關的故障狀態進行在線監測顯得尤為重要。

2 分段供電開關工作狀態分析

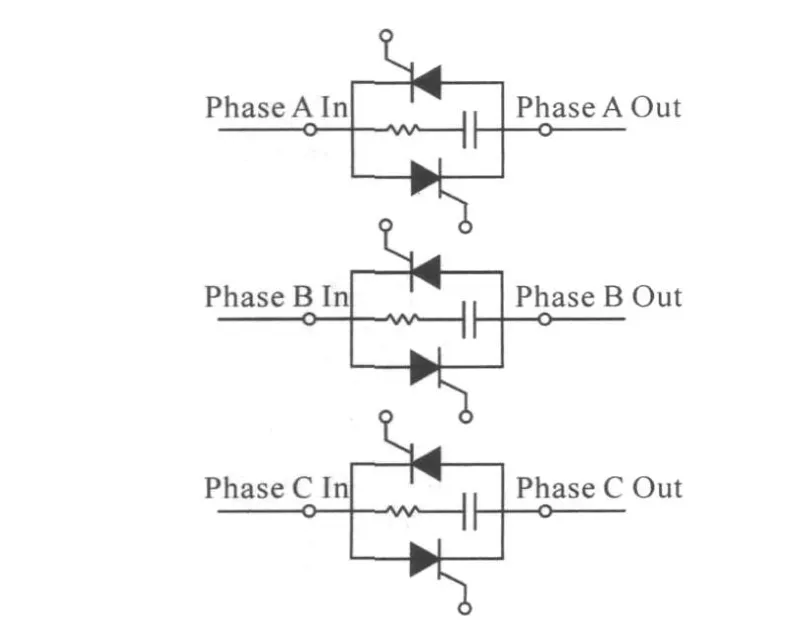

高速直線推進系統中,直線電機有三相繞組,每相的長初級繞組被分成N段,采用雙向可控硅(晶閘管)交流開關對各段繞組進行通、斷電控制。如圖1所示。

無故障情況下,給晶閘管的控制極加適當的觸發電壓,可以使晶閘管正常導通。但是如果晶閘管極間發生短路或者超溫,那么將導致晶閘管的損壞,不能正常導通。

圖1 直線電機分段供電開關

3 系統總體設計

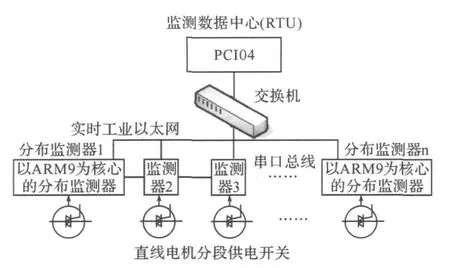

基于集散測控的設計思想,這里將監測系統設計為兩級:第一級直接面向直線電機的分段供電開關,由若干個分布監測器組成,基于ARM9設計,用于分散監測;第二級通過計算機網絡對第一級采集的直線電機分段供電開關數據進行提取匯集,由一個主監測器組成,基于PC104設計,用作監測數據中心。

圖2 直線電機分段供電開關狀態監測系統總體結構

4 系統硬件設計

4.1 分布監測器設計

4.1.1 分布監測器主體電路設計

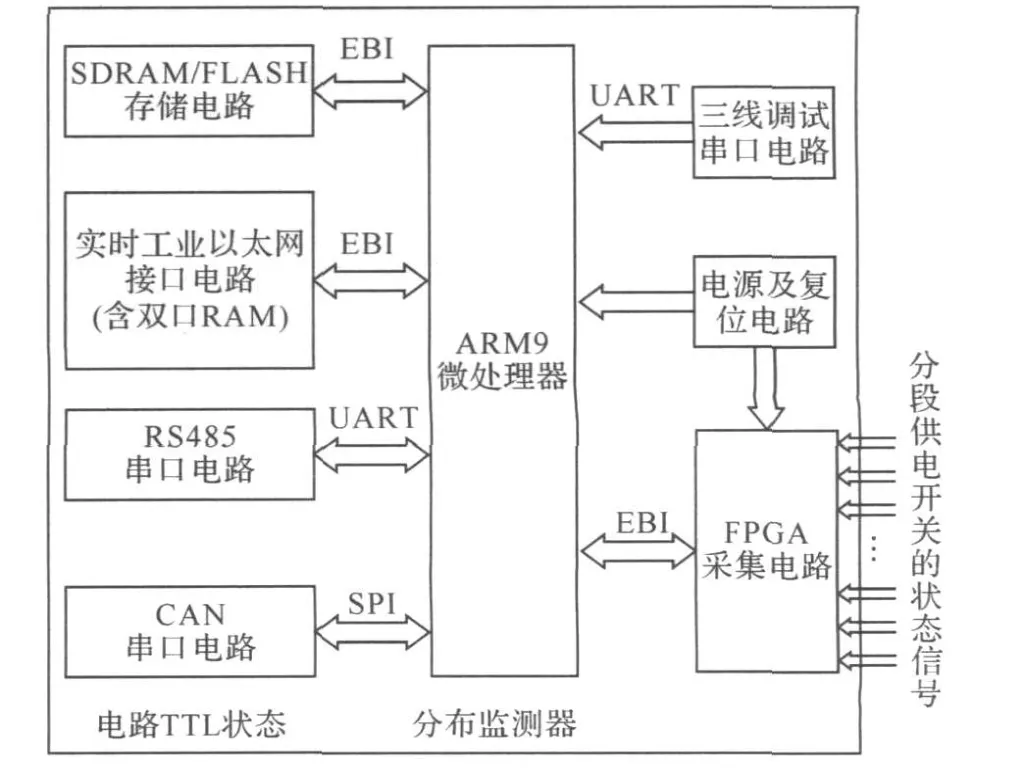

在本系統中,分布監測器主要由ARM9微處理器、電源及復位電路、FPGA采集電路、SDRAM/FLASH存儲電路、三線調試串口電路、RS485串口電路、CAN串口電路、實時工業以太網接口電路等功能模塊組成,如圖3所示。

分布監測器以工業級ARM9微處理器為核心進行設計,用FPGA芯片作為ARM9微處理器的協處理器,給系統擴展了105個并行I/O口,直線電機分段供電開關的多路T TL狀態量通過FPGA的并行I/O口進入監測器。ARM9微處理器讀取FPGA上I/O寄存器的狀態數據,暫存在SDRAM中,并對狀態數據進行分析處理,然后打包成實時工業以太網數據幀發送給監測數據中心。

圖3 分布監測器主體電路結構

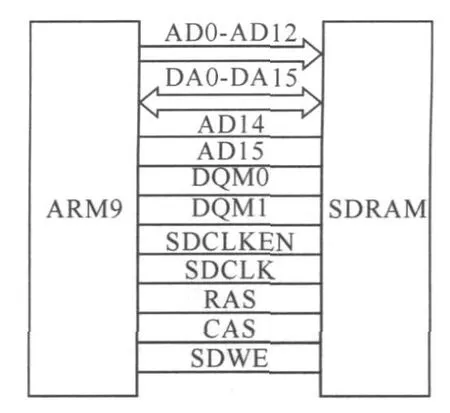

1)SDRAM/FLASH存儲電路設計

SDRAM是掉電易失性RAM存儲器,主要用來存放程序運行過程中產生的指令和數據[1]。本系統采用兩片SDRAM 芯片對ARM9微處理器的SRAM進行擴展。單片SDRAM 芯片是16位的,容量32MB,采用兩片則可以擴展到32位,64MB。連接電路,如圖4所示。

圖4 SDRAM存儲電路

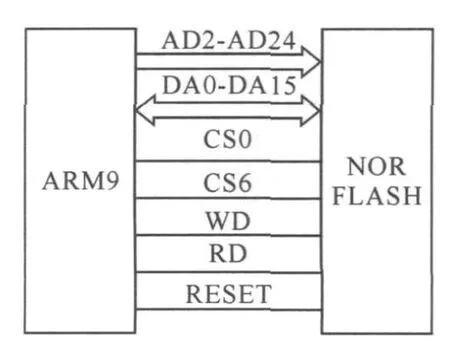

閃存是掉電非易失性ROM存儲器,可用來固化嵌入式操作系統的引導程序、芯片驅動程序以及存儲用戶編寫的應用軟件和其他在系統掉電后需要保存的數據(如每個I/O所對應的分段供電開關序列號)。在系統設計時,我們為ARM9微處理器擴展了NOR FLASH。連接電路,如圖5所示。

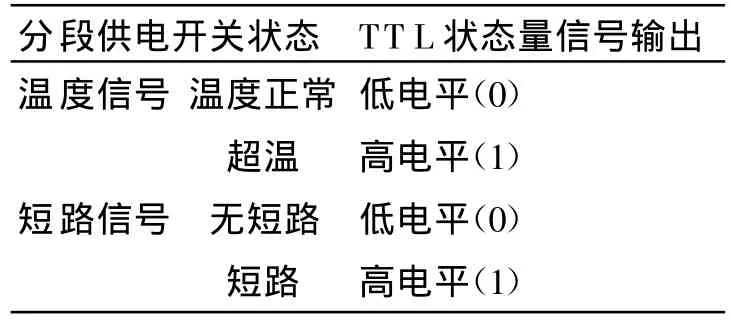

2)TT L狀態量信號采集電路設計

故障狀態檢測與識別:檢測通道的故障(正常)信號以高(低)電平方式指示,其一旦有故障產生就會保持高電平不變直到故障排除。直線電機分段供電開關的狀態信號輸出如表1所示。

圖5 NOR FLASH存儲電路

表1 分段供電開關的狀態信號識別與輸出

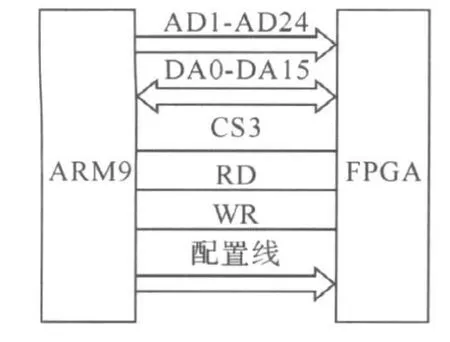

圖6 FPGA與ARM9的接口電路

每個分布監測器監測36個分段供電開關,即 72個 T TL狀態量。分布監測器通過可編程I/O口對這些TT L狀態量信號進行采集。由于 ARM9上的可編程I/O端口數量有限,不能滿足大量T TL狀態量信號的同步采集需求。本系統采用工業級FPGA芯片作為ARM9微處理器的協處理器,給系統擴展了105個可用于 T TL狀態量信號采集的 I/O。FPGA與ARM9主要通過配置線、數據總線、地址總線、控制信號線相連,如圖6所示。

4.1.2 分布監測器組網電路設計

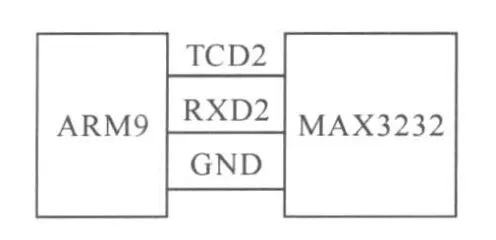

1)三線調試串口電路設計

圖7 三線調試串口(RS232)電路

三線調試串口主要是作為ARM9微處理器與用于嵌入式開發的宿主機PC進行數據交換的接口。連接電路,如圖7所示。

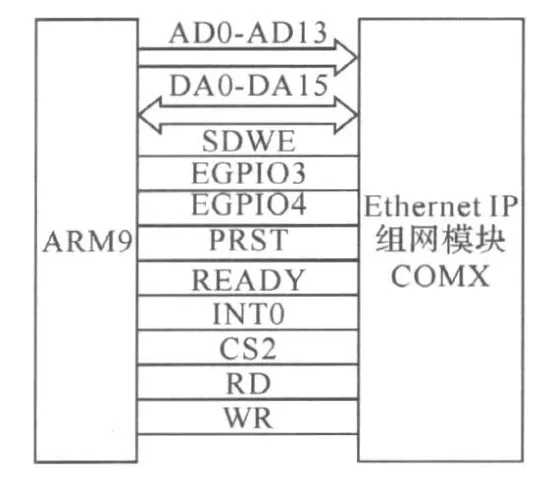

2)實時工業以太網接口電路設計

圖8 實時工業以太網接口電路

工業以太網EtherNet/IP,是一種適用于工業環境的通訊體系,能夠在廣闊的區域中支持大量現場設備的連接[2]。 本 系 統 在ARM9微處理器上擴展了一個50芯的插槽,作為與Ethernet/IP組網模塊COMX的接口。Ethernet/IP組網模塊COMX與ARM9之間通過Ethernet/IP組網模塊COMX內的雙口RAM共享數據。連接電路,如圖8所示。

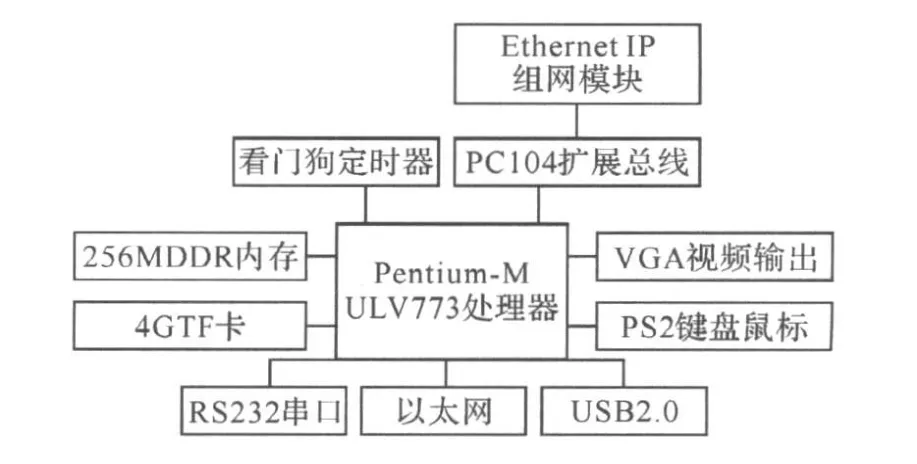

4.2 監測數據中心設計

PC104系統作為一種工業計算機系統目前在工業控制領域的應用越來越廣。由于PC104規范采用總線插接結構,使得PC104系統具有結構緊湊、應用靈活、整機功耗低等優點。本設計中,采用一臺PC104工控計算機作為監測系統的數據中心。該PC104工控機采用了Mobile Intel Pentium M ULV 773處理器,頻率為 1300MHz。板載256M的DDR內存,4G TF卡,支持 USB 2.0和12通道COM口,標準VGA視頻輸出接口,LCD液晶顯示。主要硬件組成,如圖9所示。

圖9 監測中心硬件組成框圖

其中,處理器通過PC104擴展總線與 Ethernet-IP組網模塊相連,使PC104工控機支持實時工業以太網通信。PC104工控機作為監測數據中心,接收各分布監測器上傳的狀態數據,并進行分析和處理,提供給用戶。

5 系統軟件設計

本系統在WIN CE嵌入式操作系統下,實現了TT L狀態量信號的采集和通信功能。主要的軟件功能模塊有:基于FPGA的狀態量采集模塊、基于ARM9的FPGA設備驅動模塊、分布監測器主程序、監測數據中心主程序等。

5.1 基于FPGA的狀態量采集模塊

在QuartusII軟件平臺上進行開發,采用VHDL語言編寫。代碼實現如下:

1)實體說明(Entity):描述 FPGA 的輸入、輸出端口信號:CS、rd、wr、data(15 dow nto 0)、address(3 downto 0)、T TLsignals(120 downto 0)。

2)構造體描述:設計I/O數據寄存器,用來暫存TT Lsignals(120 downto 0)對應引腳的電平狀態;針對ARM9的總線讀寫時序設計了FPGA的讀數據進程和寫數據進程。

5.2 基于ARM9的FPGA設備驅動模塊

在Platform Builder4.2開發環境下,對FPGA設備驅動程序進行開發。FPGA驅動程序采用標準流式驅動結構進行設計[3]。主要包括以下9個函數:

1)DWORD FPGA_Open()函數,用于打開FPGA設備驅動程序。當ARM9的監測器主程序執行CreatFile()函數時,系統將調用FPGA_Open()打開FPGA設備。

2)BOOL FPGA_Close()函數,用于關閉FPGA驅動程序的事例。當監測器主程序通過Close-Handle()函數來調用 FPGA_Close()后,驅動程序引用的事例將不再有效。

3)DWORD FPGA_Init()函數:當監測器主程序開始使用FPGA設備時,設備管理器通過ActivateDeviceEx()函數調用FPGA_Init()來初始化FPGA設備。

4)BOOL FPGA_Deinit()函數:當需要卸載FPGA驅動時,設備管理器會調用該函數來卸載FPGA驅動程序。

5)DWORD FPGA_Read()函數:當FPGA 驅動程序被打開后,監測器主程序可以使用ReadFile()函數對FPGA設備進行讀操作。操作成功,返回實際讀取的字節數,如果失敗,則返回-1。

6)DWORD FPGA_Write()函數:當 FPGA驅動程序被打開后,監測器主程序可以使用Write-File()對FPGA設備進行寫操作。

7)BOOL FPGA_IOControl()函數:應用程序使用DeviceIOControl()函數來通知操作系統調用這個函數。通過參數dwCode來通知FPGA驅動程序要執行的操作。

8)void FPGA_PowerDown()函數:電源管理。

9)void FPGA_PowerUp()函數:電源管理。

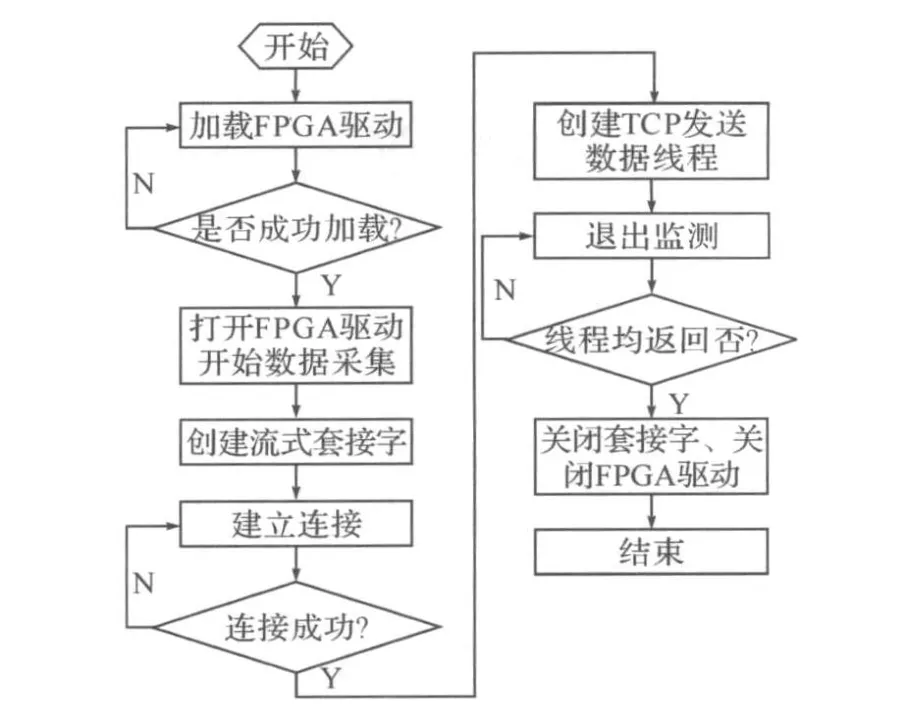

5.3 分布監測器主程序

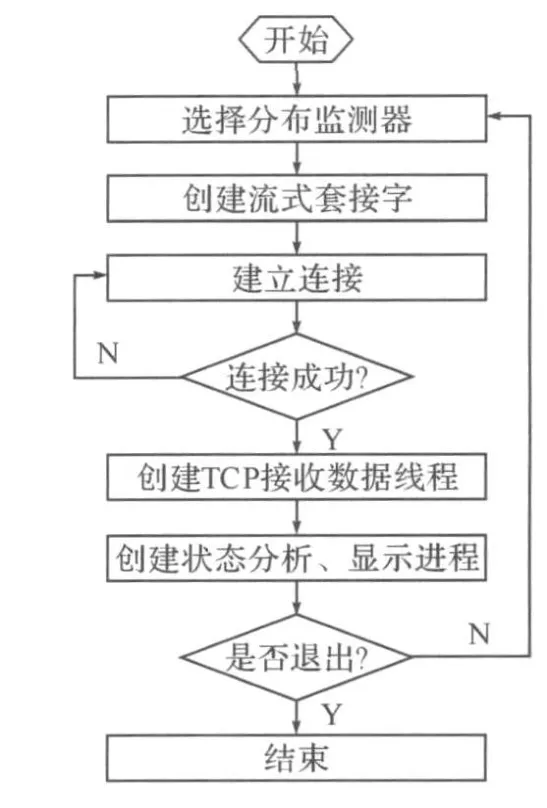

在Microsoft embedded Visual C++4.0開發環境下,對監測器主程序進行開發。監測器主程序主要包括以下幾個功能模塊:FPGA驅動的加載、網絡連接及參數的設置、數據采集及發送、退出監測。由于本系統對數據的安全性要求較高,所以我們采用流式套接字,用TCP協議傳輸分段供電段開關的狀態數據。軟件流程如圖10所示。

圖10 分布監測器主程序的軟件流程

5.4 監測數據中心主程序

監測數據中心(RTU)主程序運行于PC104,在VC++開發環境下編寫。監測數據中心(RTU)主程序主要實現以下功能:1)連接分布監測器;2)通過以太網接收分布監測器上傳的狀態數據;3)對分段供電開關的狀態數據進行分析、處理;4)通過狀態矩陣將分段供電開關的狀態直觀的顯示給用戶。軟件流程如圖11所示。

圖11 監測數據中心主程序的軟件流程

6 實測結果分析

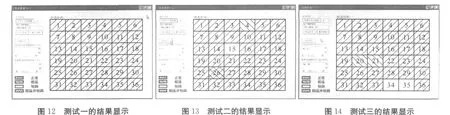

測試一

分段供電開關狀態正常,無故障信號輸入。監測數據中心顯示結果如圖12所示。

注:狀態矩陣中的綠色方格表示對應的分段供電段開關的狀態正常,紅色表示短路狀態,白色表示超溫狀態,黃色表示兩種故障狀態同時存在。

測試二

4號分段供電開關輸入超溫信號,15號分段供電開關輸入短路信號和超溫信號,26號分段供電開關輸入短路信號,監測數據中心顯示結果如圖13所示。

測試三

20號和21號分段供電開關輸入超溫信號,34號和35號分段供電開關輸入短路信號,監測數據中心顯示結果如圖14所示。

實測結果表明,該系統能夠準確、可靠的對連接在分布監測器上的36個分段供電開關的超溫和短路兩種故障狀態進行在線實時監測。

7 結語

本文采用ARM9微處理器實現了對長初級短次級直線電機分段供電開關的狀態監測。系統采用ARM9加FPGA的方式進行I/O擴展,由FPGA上的高速并行I/O完成對直線電機分段供電開關的超溫和短路兩種狀態量的采集,具有速度快、精度高的優勢,狀態采集實時性達1ms。數據通信上,本系統在ARM9微處理器上實現了實時工業以太網通信,保證了分布監測器與監測數據中心進行數據通信的實時性和可靠性。

[1]周立功,等.ARM嵌入式系統教程[M].北京:北京航空航天大學出版社,2005:33~71

[2]李正軍.現場總線與工業以太網及其應用系統設計[M].北京:北京人民郵電出版社,2006,2

[3]周立功,等.ARM&WinCE實驗與實踐[M].北京:北京航空航天大學出版社,2007,7

[4]高麗,林里,孔若英.EtherNet/IP在工業控制領域的應用研究[J].開發研究與設計技術,2007(2):123~125

[5]劉瑞安.嵌入系統特征、研究概況與設計實現[J].自動化與儀器表,2004(3):5~8

[6]鹿海霞.嵌入式振動信號采集網絡通信設計[D].東南大學碩士學位論文,2006:11

[7]林長青,孫勝利.基于FPGA的多路高速數據采集系統[J].電測與儀表學報,2005,42(5):52~54

[8]夏婷,等.嵌入式狀態監測與故障診斷裝置的設計[J].微計算機信息(測控自動化),2008(4):1~6

[9]Bimal K Bose.M odern Power Electronics and AC Drives[M].PH PTR,2002

[10]XU Zheng,ZHANG Gui-bin,LIU Hai-feng.The Controllable Impedance Range of TCSC and Its TCR Reactance Constraints[C]//Power Engineering Society Summer Meeting,IEEE,2001:939~943