基于FPGA的半硬回收數據采集存儲系統設計

聶 飛,張 榮,黃海瑩

(中國工程物理研究院 總體工程研究所,綿陽 621900)

1 引言

半硬回收系統作為多通道數據采集存儲裝置,主要負責記錄某系統空中飛行試驗全程的加速度、環境參數以及各種動作控制信號。在飛行試驗完成后,將半硬回收裝置內的存儲器取出并連接到新的數據采集存儲裝置上,利用計算機將存儲器內的信號回讀并顯示出來。由于在設計中要求半硬回收系統硬件尺寸不大于φ60 mm,同時要與3.3 V和5 V系統接口,這對硬件設計提出了較高難度的要求,在硬件上確保計算機軟件的高速數據回讀、高速校驗,保證了科技人員在試驗現場即可觀測測量的結果。本文利用VHDL語言和 QuartusⅡ7.1軟件作為開發環境完成了整個半硬回收系統硬件設計。

2 系統硬件組成

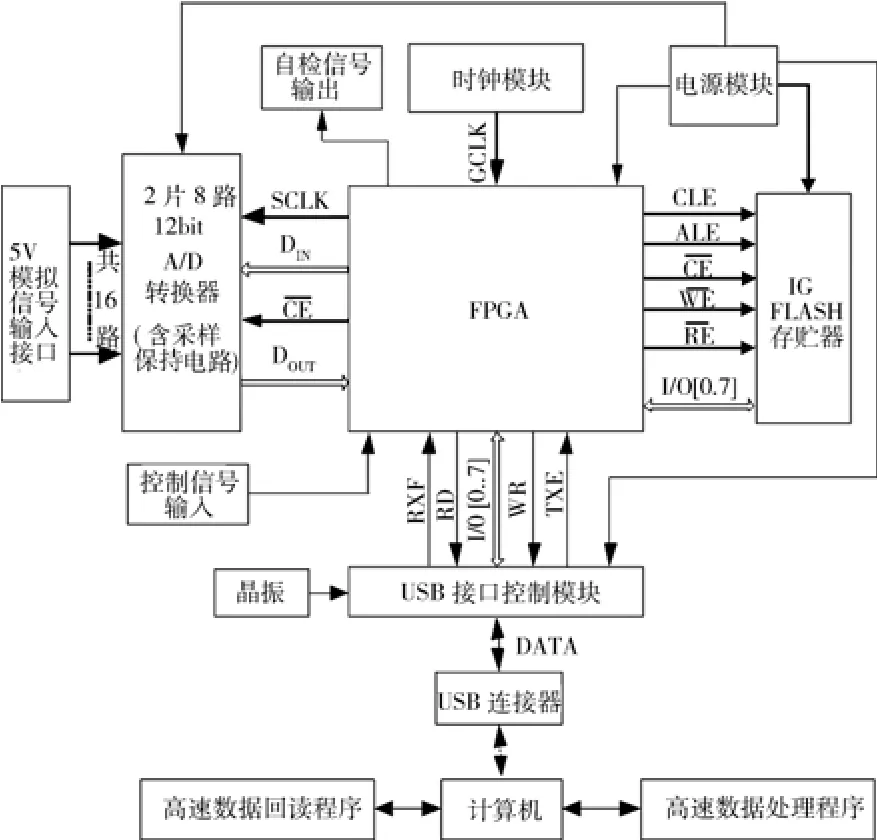

半硬回收數據采集存儲系統主要由 FPGA、A/D轉換器、Flash存儲器、USB接口芯片以及電源模塊構成,系統原理如圖1所示。

數據采集、存儲系統設計技術指標如下:(1) 模擬信號輸入通道數16路;(2) 模擬信號輸入范圍0~5 V;(3) 數據分辨率12 bit;(4)3路數字信號輸入,1路數字信號輸出;(5) 采樣頻率 10 kHz(最大可升級到 20 kHz);(6) 存儲器容量1 GB。

圖1 半硬回收數據采集存儲系統Fig.1 Schematic diagram of half-reclaimable data acquisition and storage system

3 FPGA時序設計

3.1 主控邏輯模塊設計

主控邏輯模塊在半硬回收數據采集系統中擔任時序控制、數據緩存、Flash讀寫擦除、A/D轉換器的啟動、USB接口讀寫以及與程控系統通信等重要工作,是設計的重點。FPGA選用ALTERA公司的 EP1K50。設計思路采用“自上而下”[1]的模式。

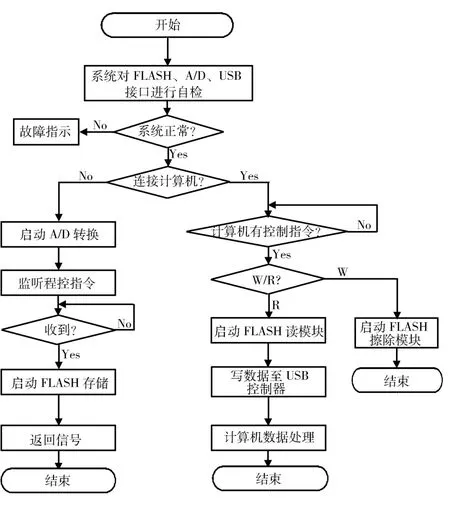

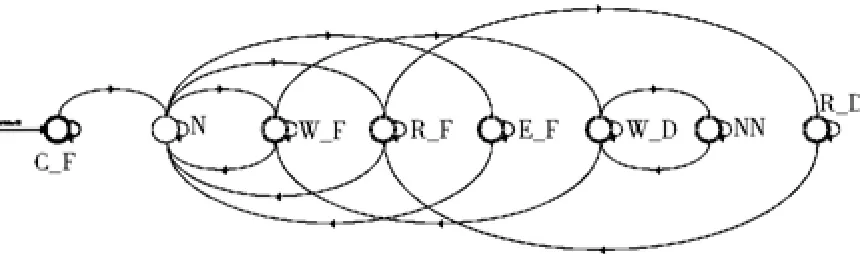

系統在通電時完成FPGA配置后,FPGA開始工作。首先要完成系統的自檢,自檢工作主要包括Flash的無效塊檢測和初始化、A/D轉換器和USB接口控制模塊的初始化。系統自檢完后通過LED指示系統向程控輸出狀態信號,系統正常則啟動 A/D轉換器,此時數據不存儲,系統處于等待命令狀態,當接收到來自程控系統的存儲指令后,啟動Flash存儲模塊,并返回一個信號至程控系統。系統自檢完后,若USB接口連接至計算機,計算機發出讀指令后,FPGA啟動讀Flash模塊并將數據送往計算機進行處理;數據讀完后,計算機發出清空Flash指令,FPGA則啟動擦除Flash模塊。主控邏輯模塊工作流程如圖2。主控邏輯模塊包含C_F、N、W_F、R_F、E_F、W_D、NN、R_D共8個狀態,其狀態轉移如圖3。

圖2 主控邏輯模塊工作流程Fig.2 Flow chart of main controller module

圖3 主控邏輯狀態轉移Fig.3 Transferring of main controller logic states

3.2 A/D時序設計

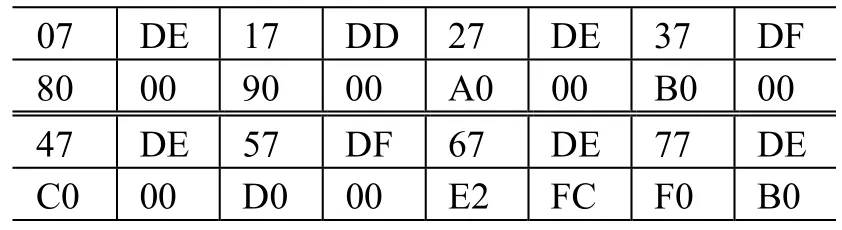

本系統中A/D芯片選用AD7928[2],該芯片為8路模擬輸入,輸入電壓范圍2.5~5 V可選,采樣數據為 12 bit,單通道最高采樣頻率 1 Mbit/s,每次數據轉換需要16個時鐘周期,輸出數據格式見表1。

在本系統中,使用了2片AD7928,共16個模擬輸入通道,1#A/D的輸入通道編號為0~7,2#A/D的輸入通道編號為8~15,因此需用4位表示當前數據輸出通道號,即當1#A/D輸出數據時在其輸出地址的基礎上增加一位“0”,2#A/D輸出數據時在其輸出地址的基礎上增加一位“1”,這樣通道和數據共16位,采用2個字節表示,其數據編碼格式見表 2。編碼好后的數據依次存入在FPGA內開辟的2 048 B的FIFO中。

表1 AD7928數據輸出格式Table 1 Data output format of AD7928

表2 16通道采樣數據編碼格式樣表Table 2 Code format of 16 channel sample data

A/D在通電后,首先需對控制寄存器進行操作,AD7928的控制寄存器為12 bit只寫寄存器,在控制寄存器中完成通道輸入電壓范圍設置、A/D通道選擇、輸出數據編碼格式設置以及電源模式設置等,本設計中控制字為“110111111001”,由于輸入控制字在16個周期內完成,最后4個周期一般設置為“1”。圖4為QuartusⅡ7.1下VHDL代碼編寫的A/D控制模塊仿真結果。

圖4 A/D時序仿真結果Fig.4 Simulation result of AD time sequence

3.3 Flash模塊設計

系統選用了三星公司的閃存芯片K9K8G08U0A[3]作為數據存儲器,該 Flash容量為8 Gbit,采用3.3 V供電,它可以在400 μs內完成一頁2 112個字節的編程操作,還可以在2 ms內完成128 kB字節的擦除操作,同時數據區內的數據能以50 ns/B的速度讀出。K9K8G08U0A大容量閃存芯片的 I/O口既可以作為地址的輸入端,也可以作為數據的輸入/輸出端,同時還可以作為指令的輸入端。芯片上的寫控制器能自動控制所有編程和擦除操作,包括提供必要的重復脈沖、內部確認和數據空間等。

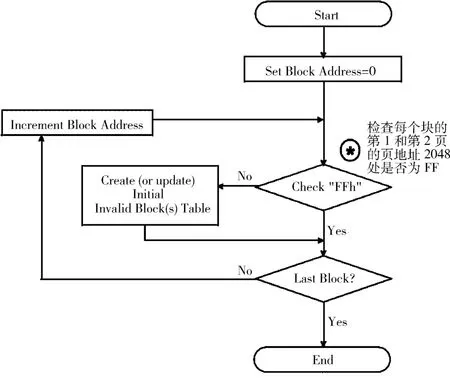

Flash芯片在出廠時可能存在壞塊,在使用過程中也會產生壞塊。壞塊是包含一位或多位無效位的塊。壞塊在大多數情況下也是可擦寫的,并且一旦被擦掉就不可能恢復。因此在Flash進行讀、寫或擦除操作前,必須檢測出Flash中的壞塊,并建立塊的好壞狀態表以備執行其他操作時進行查詢。K9K8G08U0A的塊檢測操作流程如圖5。

對于 Flash的寫操作如果按頁進行,在保證不丟失 A/D采樣數據的情況下至少需要開辟4 096 B的緩存空間,同時對于建立塊的好壞信息表需要8 192 bit的存儲空間,在這種情況下就超過了所選FPGA的內部資源容量,因此Flash的讀寫操作均改為半頁操作,即將數據緩存空間改為2 048 B,當FIFO半滿時主控邏輯啟動Flash的寫操作。

圖5 K9K8G08U0A的塊檢測操作流程Fig.5 Block check flow chart of K9K8G08U0A

3.4 USB接口設計

半硬回收系統所采集數據最終通過 USB接口上傳到計算機,同時計算機通過USB接口下發指令到半硬回收系統,其指令包括:(1) 利用計算機向回讀裝置發送與結束數據預采集命令。該功能用于調試半硬回收裝置硬件時使用;(2) 利用計算機向裝置發送擦寫 Flash存儲記憶體的命令。該功能用于數據采集前清除 Flash內容。命令功能表見表3。

表3 USB命令表Table 3 Commands of USB

半硬回收裝置數據回讀系統硬件利用 FTDI公司生產的FT245BM芯片實現系統與計算機之間的 USB總線接口通訊。FT245BM 芯片支持USB1.1與USB2.0規范,數據最大傳輸速率可達1 MB/s。USB接口的VHDL設計主要包括接收數據和發送數據兩個狀態。

4 結論

多次利用標準信號源以及振動試驗、火炮試驗對半硬回收裝置進行考核調試,結果表明系統能有效采集、存儲數據,與計算機通信時能有效接收命令和回傳數據,數據上傳速率為8 Mbit/s,系統運行穩定可靠。

(References)

[1]Stefan S, Lennart L.VHDL設計電子線路[M].邊計年, 薛宏熙, 譯.北京: 清華大學出版社, 2008: 10

[2]Analog Device.8-channel, 1MSPS, 8-/10-/12-bit ADCs AD7908/AD7918/ AD7928[G], 2006

[3]Samsung Electronics Co., Ltd..K9XXG08UXA Flash Memory[G], 2006