基于嵌入式系統的誤碼儀的總體設計

古志強,石春和,賈盼恩 (軍械工程學院,河北 石家莊 050003)

基于嵌入式系統的誤碼儀的總體設計

古志強,石春和,賈盼恩 (軍械工程學院,河北 石家莊 050003)

誤碼儀是專門為測試通信信道誤碼率而開發的儀器,其測試的直觀性給工程實際應用帶來了極大的便利。設計了基于嵌入式系統和FPGA的簡易誤碼儀,充分利用了FPGA強大的可編程能力和豐富的資源,以及WinCE嵌入式系統體積小、功能強大等優勢。設計了基于FPGA的誤碼測試板,該板通過PC104總線與PCM-3350嵌入式系統板進行通信,在實驗平臺上初步實現了其功能,具有很好的實用價值。

嵌入式系統;誤碼測試儀;FPGA;PC104

0 引 言

由于數字通信具有許多優良的特性,數字傳輸方式日益受到歡迎。但在數字通信中,信道噪聲使得接收端不可避免地會出現誤碼而影響通信的可靠性,在數字通信中誤碼率是一項主要的質量指標[1]。因而,誤碼與誤碼率的研究與檢測一直深受關注。誤碼儀將信道誤碼率結果直觀、準確地顯示出來,從而可方便地判斷數字通信系統的可靠性。本文充分利用了FPGA的靈活性,以及嵌入式系統的體積小、功能強大等優勢,設計了該簡單實用的誤碼儀。

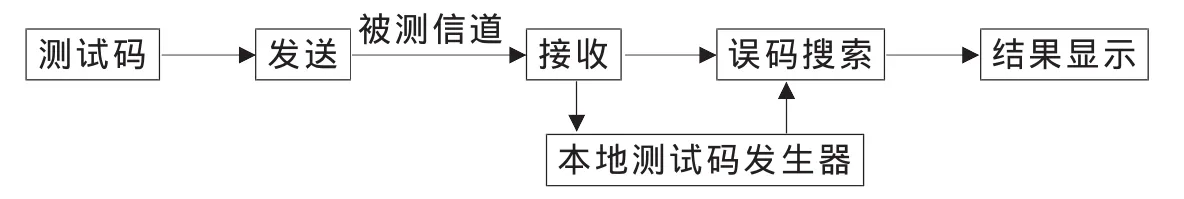

1 誤碼測試系統的基本原理

誤碼率的測試儀主要由發送模塊和接收模塊兩個部分組成[2]。首先,由發送模塊產生偽隨機碼序列數據流,作為誤碼測試的測試碼;經過發送端發送到被測信道,測試碼通過被測信道后由接收端模塊接收,經過一定的處理后,將其與本地產生的、與發端形式相同的偽隨機碼比特流進行比較,分析比較的結果即可計算誤碼率,從而完成誤碼測試。誤碼率計算方法如下[2]:

式中,m為傳輸的誤碼數,N為發送的碼元總數。

如圖1所示,其中,接收端的時鐘提取電路為本地測試碼發生器提供與發送端同頻率的時鐘,從而保證接收端時鐘的正確性。

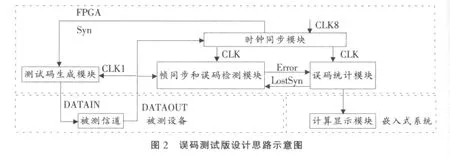

2 誤碼測試板的設計思路

誤碼測試板設計思路示意圖如圖2所示,該板由FPGA及其外圍電路組成,核心器件為FPGA,其工作原理如下:

圖1 誤碼率測試原理圖

在低頻時鐘CLK1的驅動下,將 “測試碼生成模塊”生成的時鐘測試數據輸入到被測信道,由FPGA設計的接收端接收。接收端包含有時鐘同步模塊、幀同步和誤碼檢測模塊和誤碼統計模塊。 “時鐘同步模塊”在高頻時鐘CLK8的驅動下,提取時鐘測試數據流的時鐘信號,時鐘同步成功后,便得到同步時鐘CLK和時鐘同步信號Syn,并用Syn信號通知發送端時鐘同步階段已完成,使 “測試碼生成模塊”開始發送周期為T=29-1的m序列 (即該系統標準的誤碼率測試碼)。m序列經過被測信道進入接收端的 “幀同步和誤碼檢測模塊”,接下來進行幀同步搜索,當首次搜索到幀同步信號時,所有計數器復位并開始計數,并對一幀數據進行誤碼檢測;若非首次搜索到幀同步信號,則只對幀信號進行誤碼檢測。檢測到的誤碼信號傳遞給 “誤碼統計模塊”,該模塊負責統計誤碼數,并把誤碼數送給顯示模塊進行誤碼率計算和顯示。在誤碼檢測過程中,若一幀數據的誤碼數達到誤碼閾值或者激活 “Reset”鍵,則該模塊會給幀同步和誤碼檢測模塊發送LostSyn信號,使所有的計數器清零,并使系統重新進行幀同步搜索和誤碼檢測。

3 誤碼儀軟硬件設計

3.1 誤碼儀硬件設計

誤碼儀的主要硬件構成為研華公司的PCM-3350嵌入式系統板和自行設計的以ALTERA EPF10K20TC144-4芯片為核心的誤碼測試板。

PCM-3350是一款基于X86體系微處理器和PC104總線的模塊,板載功耗低,可以無風扇工作,支持Windows CE系統,兼容工業計算機的所有功能,專門為嵌入式系統開發設計,能夠適合各種場合和各種惡劣環境[3]。

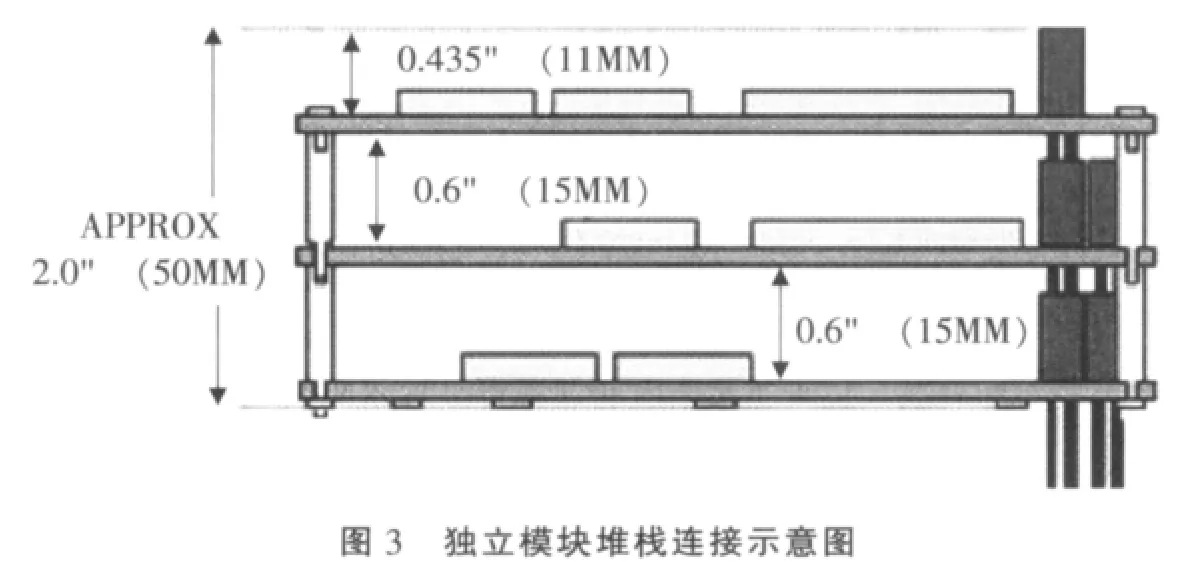

PCM-3350和誤碼測試板通過PC104相連接。其中,PC/104總線信號定義和功能與它們在ISA總線相應部分是完全相同的。104根線分為5類:地址線、數據線、控制線、時鐘線、電源線。其模塊的擴展和應用非常靈活[3]。在嵌入式系統中通常有獨立的模塊堆棧和作為元件應用兩種基本方法來使用。該設計中采用獨立模塊堆棧的方法,即PC104總線模塊之間的連接是通過上層的針和下層的孔互相咬和相連,這種層疊封裝有極好的抗震性,也可以硬件減小占用的面積。該設計中誤碼測試板和PCM-3350的連接方式就是采用獨立模塊堆棧的方式。獨立模塊堆棧連接示意圖如圖3所示。

誤碼測試板的設計以EPF10K20TC144-4芯片為核心,充分利用了FPGA芯片靈活的編程能力,使得設計的周期和成本大大降低。EPF10K20TC144-4芯片具有144個外部引腳,有102個可以被配置使用,具有1 152個邏輯單元,12 288個RAM位,1 344個觸發器。該器件使用TQFP封裝方式,支持高達60MHz的數據速率[3]。測試碼發送模塊和接收模塊都由該芯片實現,同時為了調試方便,設計了手動誤碼加入模塊。

誤碼測試板與PC104總線進行連接時,使用的總線信號包括:數據總線,SD0~SD15;地址總線,SA0~SA9;讀寫線,IOW、IOR;DMA控制信號,AEN;電源和地線,+5V、+12V、GND等。其中,SA0~SA9直接與FPGA配置為輸入的10位IO引腳相連。SD0~SD15直接與FPGA配置為輸出的16位引腳相連接。IOW、IOR、AEN直接與FPGA配置為輸入的3位IO引腳相連。其他為電源、晶振和FPGA配置模塊和掉電保護等外圍電路。

3.2 誤碼儀的軟件設計

WinCE是開放體系結構的嵌入式操作系統,具備完備的操作系統特性包,能較好地滿足開發基于嵌入式誤碼儀的需求[4]。

為了使自行設計的誤碼測試板能實現其功能,為其開發了配套軟件,包括應用程序和流式接口驅動程序。

設備驅動程序是操作系統與硬件交互的方式,是連接硬件與操作系統之間的橋梁,操作硬件是驅動的首要任務[5]。在WindowsCE下,多數驅動程序都以用戶狀態下的DLL文件形式存在。DLL文件最大的優勢在于可在系統運行時動態加載。本設計中的流式接口驅動程序的加載就是通過應用程序動態加載實現的。流式接口驅動程序具有定制的接口,是一般類型的設備驅動程序,其驅動程序文件一般也表現為 “*.dll”文件。這種驅動程序的函數是一組固定的函數,稱為流接口函數,這些函數使得應用程序可以通過文件系統訪問這些驅動程序,也就是說,流式接口驅動程序把設備抽象為文件進行操作。

Windows CE中定義的流式接口函數有 12個[5],分別為 XXX_Open(),XXX_Close(),XXX_Init(),XXX_Deinit(), XXX_Read(), XXX_Write(), XXX_Seek(), XXX_IOControl(), XXX_PowerUp(), XXX_Power-Down(),XXX_PreClose(),XXX_PreDeinit()。其中XXX是驅動程序的設備名稱,有些函數是直接與某個文件操作API對應的;而有些函數是為了某些特殊的目的。在本設計中設備名稱為BER,所以命名用到幾個函數為BER_Init(),BER_Deint(),BER_Read(),剩余幾個流式接口函數不進行任何實質性的操作,可以置為空函數。在BER_Init()中實現一些全局變量的初始化,在BER_Deinit()中實現全局變量的恢復,在BER_Read()實現了從總線上讀取數據的功能。

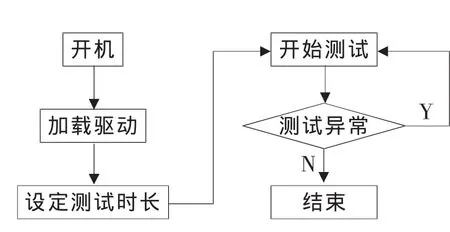

該設計的應用程序基本結構如圖4所示。

該軟件的開發環境為EVC4.0,面板中顯示的項目有誤碼個數、誤碼率、測試時間和當前時間,以及測試進度。使用方法為:首先打開電源,系統初始化的過程中應用程序自行啟動并動態加載流接口驅動程序,然后進入設置測試時長的界面。設置完后按確認鍵進入測試面板,面板中的顯示實時的計算結果。

誤碼相關數據從讀出到顯示的基本流程為:首先由應用程序每0.5s調用讀函數,讀函數通過調用下面這個函數:

BOOL ReadFile(

HANDLE hFile,

LPVOID lpBuffer,

DWORD nNumberOfBytesToRead,

LPDWORD lpNumberOfBytesRead,

LPOVERLAPPED lpOverlapped

);

驅動程序就將要讀取的數據返回給應用程序。應用程序得到所需數據后,再將數據按照誤碼率計算方法進行運算,計算的結果在誤碼儀的測試軟件面板中顯示出來。

對于FPGA的程序設計,采用VHDL語言和原理圖混合的方法實現五大功能模塊,有測試碼生成模塊、時鐘同步模塊、幀同步和誤碼檢測模塊、誤碼統計模塊,LE使用率為91%。

圖4 應用程序基本結構

4 結束語

為了驗證以上所述設計方法的有效性,在理論研究的同時,也進行了一些實驗。在對整個系統調試過程中,直接將發送端接到接收端進行自測時,設定測試時間為30分鐘,如果沒有手動加入誤碼,則誤碼個數顯示為“0”,誤碼率顯示為 “0”;如果手動加入誤碼,誤碼個數與手動加入誤碼次數相一致,誤碼率顯示正確。系統調試結果表明,該方案具有可行性。在以后的研究中將進一步完善之。

[1] 樊昌信,曹麗娜.通信原理[M].6版.北京:國防工業出版社,2006:398.

[2] 楊亮.低速率誤碼測試儀的設計和實現[D].鄭州:鄭州大學,2005.

[3] 關進輝.面向防空指揮系統的空情信息模擬訓練器的設計與實現[D].石家莊:軍械工程學院,2010.

[4] 趙國峰,朱其林.基于WinCE移動終端的無線視頻會議系統[J].通信技術,2008,41(8):201-203.

[5] 何宗鍵.Windows CE嵌入式系統[M].北京:北京航空航天大學出版社,2006:194-264.

Design of BER Test Apparatus Based on Embeded System

GU Zhi-qiang,SHI Chun-he,JIA Pan-en (Ordnance Engineering College,Shijiazhuang 050003,China)

BER test apparatus is designed to test bit error rate of communication channel.Intuition of the test brings great convenience to the practical application.A sample BER test apparatus based on embedded system and FPGA is designed,making full use of the design flexibility and powerful function of FPGA and WinCE embedded system.The BER test board is designed and its communication with the PCM-3350 board depends on PC104.Its preliminary function is achieved on the experiment platform,It has a good practical value.

embedded system;BER test apparatus;FPGA;PC104

TN911

A

1002-3100(2010)09-0089-03

2010-06-22

古志強(1987-),男,江西尋烏人,軍械工程學院碩士研究生,研究方向:控制系統性能檢測與故障診斷。