LPCVD制備二氧化硅薄膜工藝研究

王儉峰,佟麗英,李亞光,李秀強

(中國電子科技集團公司第四十六研究所,天津300220)

當前CMOS已成為MOS電路的主流,為解決問鎖效應和軟失效,在CMOS電路生產中大量使用外延片。這種CMOS用的外延片,多用背面多晶硅作為吸除源,并用低溫SiO2封閉,以防止在硅外延過程中雜質對正在生長外延層的“摻雜”,從而使外延層不受破壞[1]。因此,在硅拋光片加工工藝中廣泛應用了吸雜和背封技術。背封技術中一般是用化學氣相淀積方法在硅片背面生長一層SiO2膜,以達到消除雜質對外延工藝的不利影響。目前,由于相對其他方法在均勻性、淀積速率及使用安全性方面具有更大優勢,TEOS源LPCVD(低壓化學氣相淀積)法已逐步成為淀積SiO2膜的主流工藝。

本文對TEOS源LPCVD(低壓化學氣相淀積)法淀積SiO2膜的淀積速率及均勻性方面進行了有益探索,并在此基礎上總結出了一組較好的淀積工藝條件。

1 實驗及原理

SiO2膜的淀積采用LPCVD法,使TEOS(正硅酸乙酯)在700℃,50 Pa左右的條件下熱分解制得。

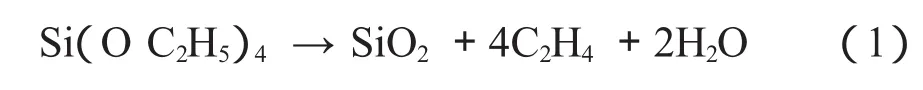

化學氣相反應可以概括描述為:

TEOS也就是 Si(O C2H5)4,學名正硅酸乙脂,又稱四乙氧基硅烷,常溫下為無色液體,淀積時在鋼瓶中揮發進入爐管內,TEOS的流量由TEOS源瓶的溫度來控制。

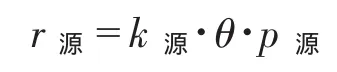

反應物在爐中的分壓主要由源溫度和反應壓力共同決定。只要其中一個條件改變,反應物分壓就會改變。當TEOS源(下面簡稱源)進入反應室,由于邊界層的存在,源只能擴散進入襯底表面,而生長表面有一定密度的活性點,氣態源分子可以與其結合形成活化絡合物,發生表面反應,生成固態粒子和吸附態氣體副產物,之后吸附態的副產物解吸離開表面。在這個過程中,可知吸附速率為:

其中:θ為未被占據的表面活性點占總數的百分數,p源為源分壓。

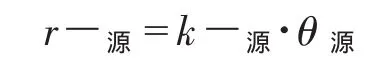

若吸附后為分解而解吸,則:

在表面分解時淀積速率: r=k·θ源

反應后副產物解吸: r-氣=k-氣·θ氣

而 θ+θ源+θ氣=1

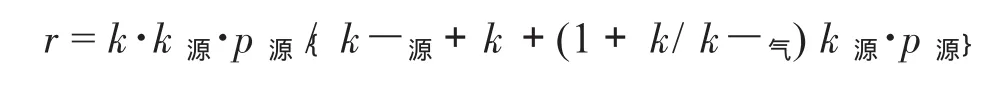

由以上各式得

淀積速率

2 結果與討論

2.1 TEOS源溫度對淀積速率的影響

TEOS源的溫度直接影響了TEOS的流量,從而影響反應物分壓,故若TEOS源的溫度過低,則淀積會由于反應物過少而根本長不上膜,而過高會使均勻性變差。

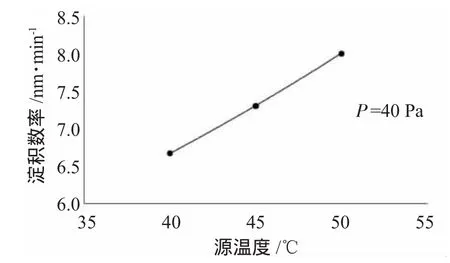

在其他條件(淀積溫度、反應壓力等)相同的情況下通過改變TEOS源溫度,對于不同的TEOS源溫度所生長的SiO2膜,結合淀積時間算出T=710℃時,淀積速率與TEOS源溫度關系如圖1所示。

由圖中可以看出,隨著TEOS源溫度的增加,SiO2的淀積速率呈線性增大。

圖1 淀積速率與TEOS源溫度的關系

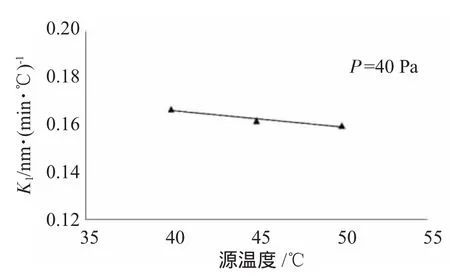

圖2 K1與TEOS源溫度關系

若設K1=C·V/T源,其中C為系數,V為淀積速率,T為TEOS源溫度。則K1可以表達每TEOS源溫度對淀積速率的影響。由于其他條件不變,C為常數。若設C=1,則如圖2所示,可以看出隨著TEOS源溫度的增加,TEOS源溫度中的每一攝氏度對淀積速率的影響幾乎不變且保持在較高數值。這說明在此條件范圍內,到達硅片表面的反應物的量一直都是淀積速率的重要因素。增大TEOS源溫度可有效地增大淀積速率。

分析其原因,在襯底表面,由公式(1)可知,反應前后氣體分子由一個TEOS分子轉變為四個C2H4分子和兩個H2O水分子,當反應室壓力一定時,隨反應的進行,必然導致TEOS分子所占分壓在較低水平。此時,提高TEOS溫度,則使TEOS源釋放率增大,從而使室內源分子所占比例增大,淀積速率增大。

2.2 反應壓力對淀積速率的影響

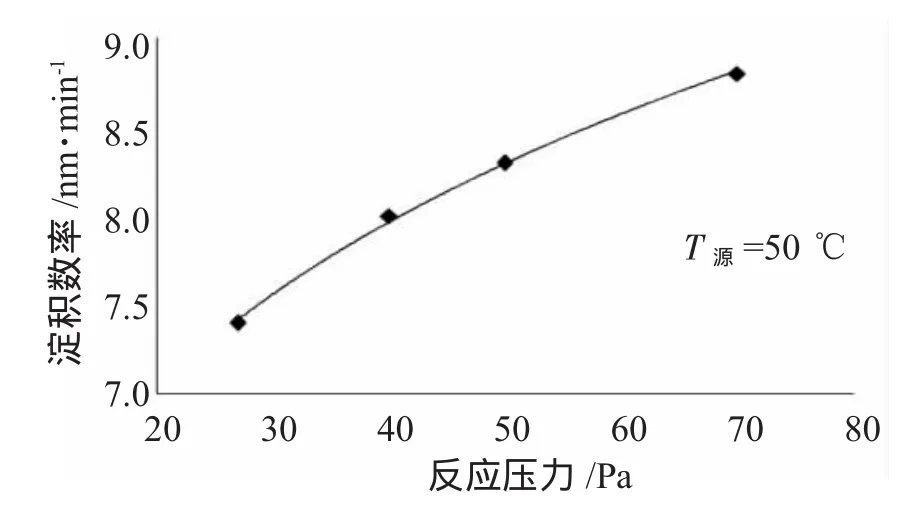

由圖3可以看出,在反應室內隨著反應壓力的升高,SiO2的淀積速率基本呈線性增大。

圖3 反應壓力與淀積速率關系

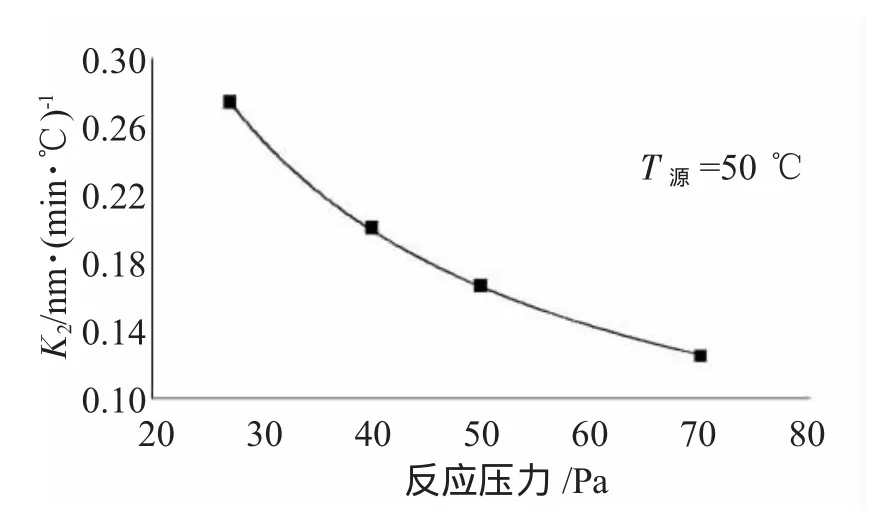

圖4 K2與反應壓力的關系

若設K2=C·V/P,其中C為系數,V為淀積速率,P為反應壓力。則K2可以表達每反應壓力對淀積速率的影響。由于其他條件不變,C為常數。若設C=1,則如圖4所示,可以看出隨著反應壓力的增加,每帕壓力對淀積速率的影響逐漸減弱且降低速率隨壓力升高逐漸放緩。這說明在低壓范圍內反應壓力對淀積速率有更大影響。分析其原因為,在低壓時,淀積速率較低,反應室內氣體中氣態TEOS源占有較大分壓,而隨壓力升高,反應速率增大,附產物分子氣體產生的速率也逐漸增大,氣態TEOS源所占分壓逐漸減小,致使壓力升高對淀積速率的增益逐漸減小。

2.3 SiO2膜的均勻性

對于淀積SiO2膜來說,均勻性是一個很大的問題。薄膜的均勻性一般分片內均勻性和片間均勻性。經驗證明,對于片內均勻性來說,片距起重要作用。片距較小時,片間容易存積過多熱分解產生的附產物而使片間氣態TEOS源不均勻,從而導致硅片各部分淀積速率快慢不一。片距較大時,反之;而壓力較低時,反應室內氣態TEOS源所占分壓比較穩定,片內各點淀積速率比較一致。隨著壓力的升高,反應室內硅片表面附近氣態TEOS源所占分壓趨于不穩定,從而使硅片各部分淀積速率難以控制,導致片內均勻性變差。片距在5 cm左右,壓力在50 Pa以下時對SiO2膜質量來說可以接受。此外,不同位置及反應溫度對片內均勻性也有一定影響。

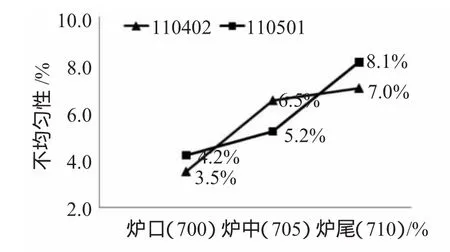

圖5為對爐內3點位置硅片SiO2膜片內均勻性的統計圖。在靠近爐口部分,源供應充足,硅片內各點源濃度較一致,而對于爐尾部分,由于前面反應消耗,源濃度占氣氛百分比較低,使硅片表面各點源濃度不容易達到均衡,而高的反應溫度又增強了這個結果。故而出現了從爐口至爐尾的不均勻性的增大。

圖5 不同位置硅片的片內均勻性

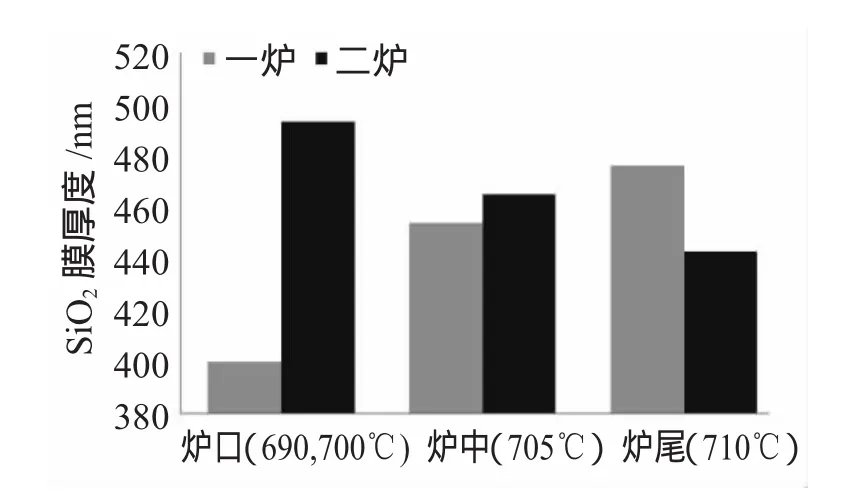

對于片間均勻性來說,反應溫度的影響為主要因素。如圖6所示,在源溫度為42℃、壓力為48 Pa時同樣淀積60m in,一爐和二爐的爐口、爐中、爐尾溫度分別為700℃、70℃、715℃,690℃、710℃、715℃。當只降低爐口溫度10℃時,爐中各點硅片厚度就有很大差別。之所以出現這種情況,分析認為是由于源釋放率即源流量不是很高時,由于源由爐口出進入,使得爐口處硅片得以首先發生反應。至于爐中的硅片能得到多少源進行反應,很大程度上取決于爐口硅片的反應速率。而爐尾硅片反應所需的源更是由前兩部分反應速率所決定。這就是所謂的輸運耗散。故此,為了抵消輸運耗散對均勻性的作用,就必須調節爐內3點溫度以使各處反應速率相等或近似相等。

圖6 反應溫度對均勻性的影響

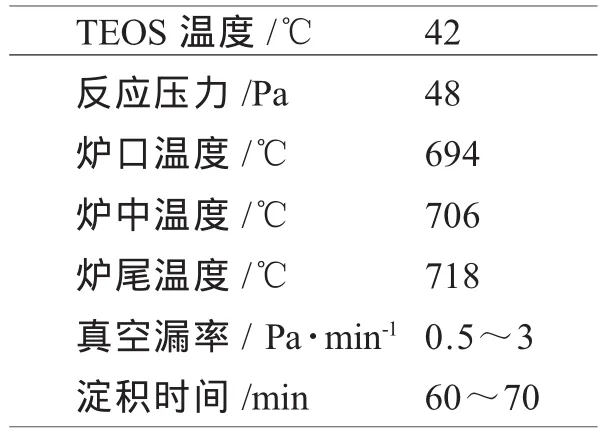

據此,通過調節各參數獲得了較好的淀積條件,其典型制備條件如表l所示。

表l二氧化硅膜的典型淀積條件

3 結論

TEOS源LPCVD法生長SiO2膜具有均勻性、重復性較好且成本較低等優點。本文對此方法淀積SiO2膜的生長速率及均勻性進行了討論,詳細分析了各反應條件與淀積速率和均勻性的內在關系。并且依此通過不斷嘗試得出了較好的工藝條件。通過對淀積速率的定量分析,可以很容易計算出任意SiO2膜厚度的淀積條件。

[1]沈天慧,李積和,何蓮萍.用多晶硅吸雜和SiO2背封工藝提高硅片質量,微電子學與計算機[J].1997(2):17.

[2]簡崇璽.LPCVD制備氮化硅薄膜工藝集成電路通訊[J].2008,26(2):18-21.

[3]劉洪俠,郝躍,朱秉升.LPCVD制SPOS薄膜淀積工藝的研究[J].西安電子科技大學學報(自然科學版),2000,27(3):309-311.