基于FPGA的RS232/422多通道接口設計與實現

徐 智,張義濤

(1.中航工業直升機設計研究所,江西景德鎮 333001;2.陸航駐景德鎮地區代表室,江西景德鎮 333000)

0 引言

RS232/422串口是目前最常用的一種工業標準,它具有技術成熟、性能可靠、操作簡單等優點,在民用和軍用航空領域被廣泛應用。

傳統的RS232/422總線接口大都采用專用的總線板卡,這種方案集成度低、成本高。當面對多設備時,就需要通過增加板卡數量來滿足多設備的要求,故而增加了系統的體積和重量。為了在最小系統中實現多通道RS232/422總線的收發和降低占用CPU時間,筆者基于FPGA設計了多通道RS232/422總線接口,使多路信號的收發和處理變得靈活、有序。

1 技術方案

1.1 RS232/422 協議簡介

基本的UART通信只需要兩條信號線(RXD、TXD)就可以完成數據的相互通信,接收與發送的全雙工形式,其中TXD是 UART的發送端,RXD是UART的接收端。UART基本特點是:在信號線上有兩種狀態,可分別用邏輯1(高電平)和邏輯0(低電平)來區分。在發送器空閑時,數據線應保持在邏輯高電平狀態,發送器是通過發送起始位來開始一個字符的傳送,起始位使數據線處于邏輯低電平狀態,提示接收器數據開始傳輸,數據位一般為8位一個字節的數(也有6位、7位的情況),低位(LSB)在前,高位(MSB)在后,校驗位一般用來判斷接收的數據位有無錯誤,一般是奇偶校驗,停止位在最后,用以標志UART一個字符傳送的結束,它對應于邏輯1狀態。

1.2 結構原理

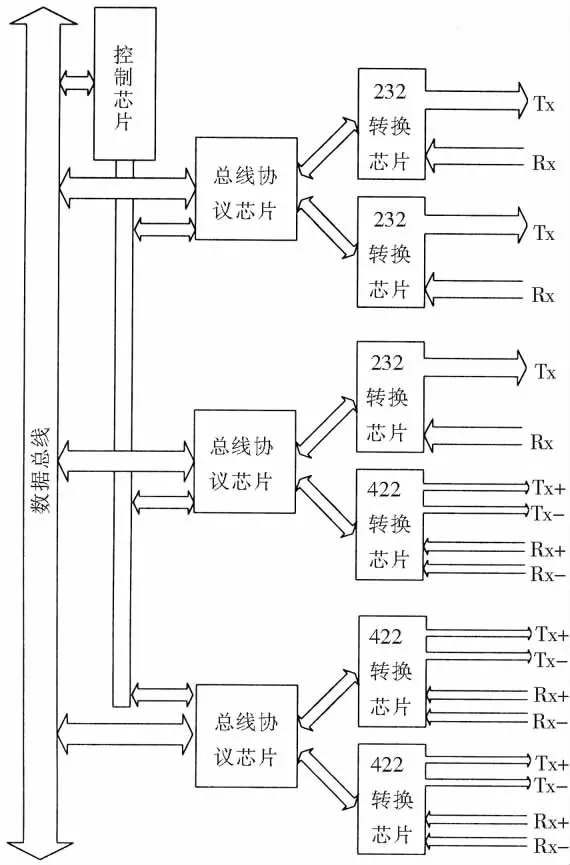

RS232/422總線是計算機與各任務設備之間進行數據交互的通道,完成數據信號的收發。它由控制芯片、總線協議芯片和電平轉換芯片組成。控制芯片從數據總線接收來自CPU的數據指令,對總線協議芯片進行配置和邏輯控制。總線協議芯片接收完數據后,將中斷信號和完整的數據信號發送給控制芯片。控制芯片通過數據總線將數據信號發送給CPU。它的結構原理如圖1所示。

圖1 接口結構原理圖

1)總線協議芯片

總線協議芯片TL16C754是4通道,每通道有64B FIFO的UART,通過3個總線協議芯片可以構成12個通道的UART。在FIFO工作模式下,每通道的發送和接收FIFO深度可以設置,減少了CPU的中斷/查詢頻率,提高了系統的效率。TL16C754輸出LVTTL電平,對4個通道TX,RX進行電平轉換,可以擴展成RS422或RS232口。在本接口電路中共選用了3片TL16C754來提供12路UART。

2)轉換芯片

Max3033,Max3093是4路 RS422電平轉換芯片。Max3033接收來自TL16C754的串行數據,轉換成滿足RS422協議的差分輸出信號。Max3094接收外部的RS422差分輸入信號,將信號轉換成串行數據傳輸給TL16C754。本接口電路中共提供了8路RS422。

Max3232是2路全雙工RS232電平轉換芯片。Max3232接收來自TL16C754的串行數據,轉換成滿足RS232協議的串行輸出信號;同時Max3232接收來自外部的RS232的串行輸入信號,將信號轉換成串行數據傳輸給TL16C754。本接口電路中共提供了6路RS232。

3)控制芯片

控制芯片實際上就是通過硬件描述語言[1],在可編程邏輯器件(FPGA)上設計實現的芯片。FPGA內部資源豐富,通過它能有效提高系統的集成度,縮小系統體積,降低成本。FPGA是RS232/422多通道接口電路的核心[2],任務是接收CPU的指令,對3片TL16C754協議芯片進行初始化,并將接收到的數據由CPU指定的通道輸出。在接收到協議芯片的中斷信號后,對中斷源進行判斷,提醒CPU到相應的通道接收新的總線數據。依據該設計原理,FPGA中提供了時鐘發生模塊、數據寄存器、地址寄存器、中斷辨識寄存器以及控制邏輯轉換的狀態機。

2 多通道總線收發的實現

2.1 協議芯片的初始化

TL16C754的串行通道由控制寄存器 LCR、IER、DLL、DLM、MCR和FCR編程。這些控制字決定字符長度、停止位的個數、奇偶校驗、波特率以及調制調解器接口。控制寄存器可以以任意順序寫入,但是IER必須最后一個寫入,因為它控制中斷。本系統中波特率設置為19200,系統工作在DMA模式1中。以設置通道A為例:

FPGA接收到數據總線上的配置字,依次配置DLL、DLH(除數鎖存寄存器)、EFR(增強功能寄存器)、MCR(調制調節器控制寄存器)、TLR(觸發等級寄存器)、FCR(FIFO控制寄存器)、LCR(線路控制寄存器)和IER(中斷識別寄存器)。通過配置上述寄存器,可將串行通道設置為19200波特率,8位有效數據位,1位停止位,無奇偶校驗。

2.2 發送/接收模塊的設計

發送模塊主要由發送FIFO緩存構成,由于協議芯片兩端連接的總線傳輸速率不同,因此用發送FIFO作為數據緩存。各個通道都有64個字節長度的發送FIFO緩存結構。只要發送FIFO中有數據,它就通過發送邏輯模塊發送出去,同時產生奇偶校驗和停止位。通過TLR寄存器可以設置觸發等級,當發送FIFO中空閑空間達到觸發等級的條件時,TXRDY信號被協議芯片給出。在本系統中,各個通道的發送是通過CPU定時器分時發送的。

接收模塊主要由接收FIFO緩存構成,由于協議芯片兩端連接的總線傳輸速率不同,因此用接收FIFO作為數據緩存。每個通道的接收FIFO也是64字節的空間。通過TLR寄存器可以設置觸發等級,當接收FIFO中接收到的數據達到觸發等級時,RXRDY信號被協議芯片給出。

2.3 多通道的切換

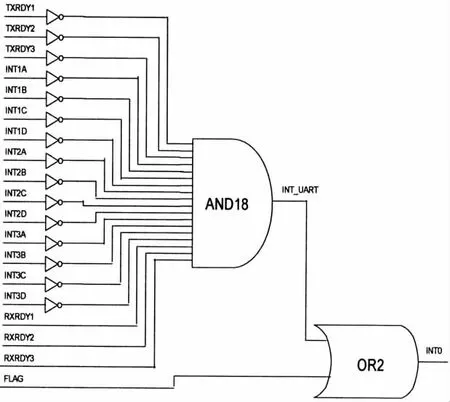

本系統中使用了3片協議芯片,每個協議芯片中有1個 TXRDY,1個 RXRDY和4個 INT信號。如圖2所示,將18個信號與在一起,產生一個中斷信號INT_UART,INT_UART和FLAG或在一起,產生中斷信號INT0,INT0與CPU相連,取其下降沿為中斷觸發信號。如圖2所示。

圖2 中斷信號

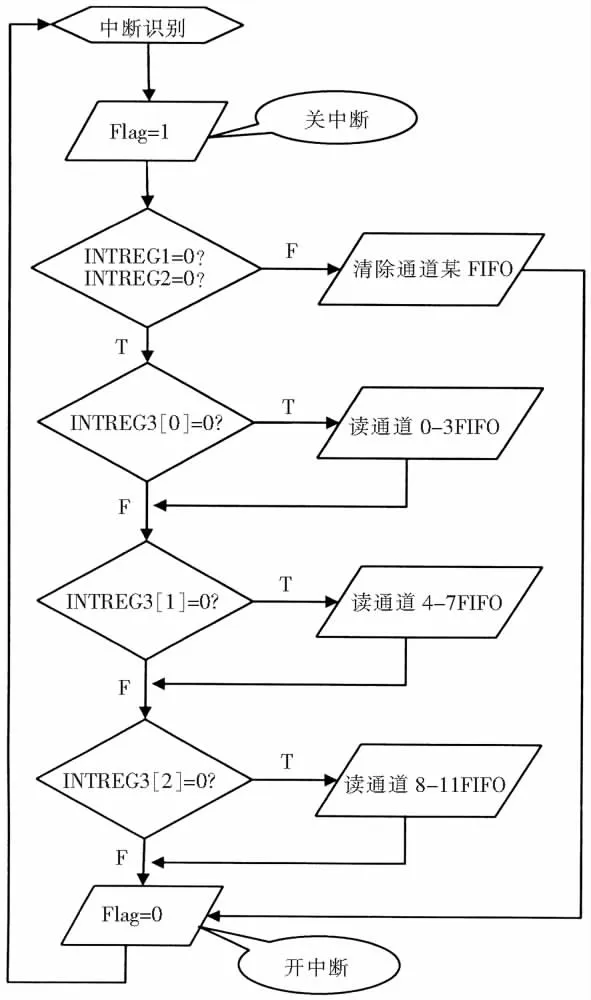

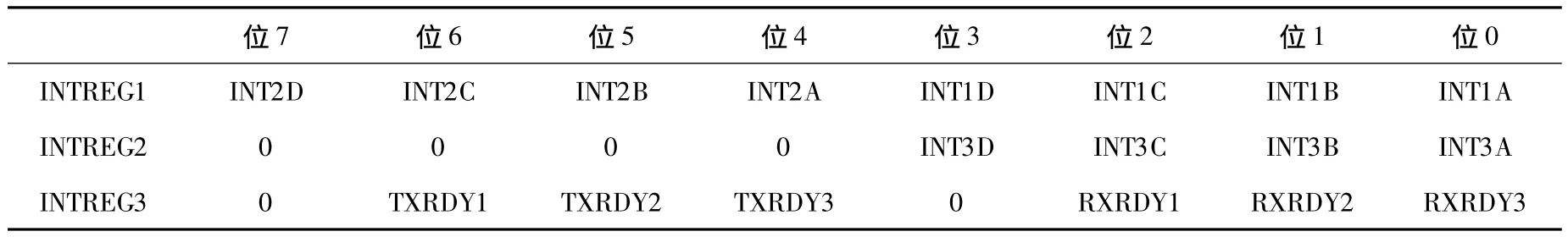

當CPU接收到INT0的中斷信號后,CPU將FLAG信號置高,從而屏蔽18個中斷源。此時,CPU進入到中斷服務程序。在中斷服務程序中,CPU讀取FPGA提供的3個中斷辨識寄存器INTREG1,INTREG2和INTREG3,如表1所示。CPU首先對INTREG1和INTREG2進行判斷,當它們全為0時,說明接收FIFO中的數據都是正確的,不存在成幀,奇偶校驗、數據溢出錯誤。INTREG3中的低3位,表示接收FIFO中的數據到達了觸發等級,CPU可以對FIFO進行讀取。CPU通過對INTREG3中低3位的判斷,可以清楚的知道哪個協議芯片的數據準備就緒,然后對指定的通道進行數據讀取操作。

這種中斷機制的引入減少了底層數據對CPU的中斷次數,使得CPU有更多的時間去進行任務調度管理。中斷服務流程如圖3所示。

圖3 中斷服務程序流程圖

表1 中斷辨識寄存器

3 結果分析和結束語

將該系統的發送接收端口接到PC機的串口端,利用PC機超級終端可以正確顯示系統通過任意UART端口發送出來的數據。本接口系統已經成功運用在某型號無人直升機航空信號仿真平臺中。

本文基于FPGA技術,設計并實現了多通道的RS232/422接口電路,通過通道的選擇和切換,提高了系統的處理能力。通過測試確定,多通道接口轉換的信號符合UART規范。這種設計思路可以方便地應用到其他類型的總線通信模塊的設計中。

[1]潘松,王國棟.VHDL實用教程[M].成都:電子科技大學出版社,2001.

[2]曹會華,賀占莊.基于有限狀態機實現全雙工可編程UART[J].計算機技術與發展,2007,17(2):54-56.