基于FPGA的多路高速信號可重構系統平臺設計

朱 昊 劉化君 宋宇飛

南京工程學院 江蘇南京 211167

基于FPGA的多路高速信號可重構系統平臺設計

朱 昊 劉化君 宋宇飛

南京工程學院 江蘇南京 211167

提出了基于FPGA的多路信號高速采集、存儲、處理系統的設計方案。給出了現代電子系統的需求分析。介紹了系統的硬件結構,討論了FPGA內部的資源分配與設計,分析了系統的可重構特點。實際應用表明,本系統具有功能靈活、處理速度高、抗干擾能力強的特點,可作為高速信號通用處理平臺使用。

FPGA;多信號;高速處理;系統重構

隨著電子技術的發展,電子系統處理信號的能力越來越強大。用戶對電子產品的要求也在不斷提高。傳統的低速系統已經逐漸不能滿足用戶的需求。另一方面,電子器件的成本越來越低,以往各種昂貴的功能強大的高速處理芯片已經逐漸平價化。因此,現在基于高速處理芯片的電子系統在生活中的應用越來越廣泛。對于這一變化趨勢,作為大學電子類教學來說,也應該逐漸調整教學重心,逐步加強各種新型高速處理芯片以及高速信號處理系統設計的介紹,以此來加強與實際需求的銜接。

1 現代電子系統的功能需求

1.1 信號處理數量多

現代電子系統往往都具有多種功能,這就要求系統能并行處理多路模擬、數字信號。這在工業控制領域尤其明顯,某些領域,如針織機械要求同時處理上百路信號。以往處理信號較少時,控制系統中通常采用微處理器,如各種單片機或數字信號處理器(Digital Signal Processor,DSP)等。但對于現在的復雜控制系統,限于處理能力、速度以及引腳數量,僅僅靠用普通的微處理器往往難以完成任務。對此,通常只能采取多個微處理器聯機的并行處理模式,或者添加其他芯片擴展系統資源來完成系統的控制任務。但這樣做不僅增加了大量的外部電路和系統成本,而且大大增加了系統的復雜性,同時系統的可靠性也會受到影響,這顯然是設計者所不希望的。

1.2 信號處理速度高

現代電子器件中,各種處理芯片的主頻越來越高。在現代生活的各個領域中,電子系統的處理速度越來越快。傳統的單片機主頻一般在6M~12MHz,對于現代高速電子產品而言已經越來越難以勝任。可編程邏輯器件(Programmable Logic Device,PLD)、ARM(Advanced RISC Machines)以及DSP等芯片可通過內部鎖相環(Phase Locked Loop,PLL)生成高達500~700MHz的時鐘信號,因此在各種民用、工業、軍事領域內廣受青睞。

1.3 電路體積和功耗小

現代電子產品中,手持設備以及微小型設備越來越多。低功耗在現代電子系統中逐漸成為一個重要的指標。另一方面,電路板的體積也不斷縮小。因此,傳統數字電路設計中多芯片結構已經不能滿足這種需求。而PLD芯片憑借其可編程實現復雜數字邏輯的功能,在現代電子系統設計中逐漸被作為數字邏輯電路的取代品。

2 系統硬件架構設計

2.1 系統總體架構

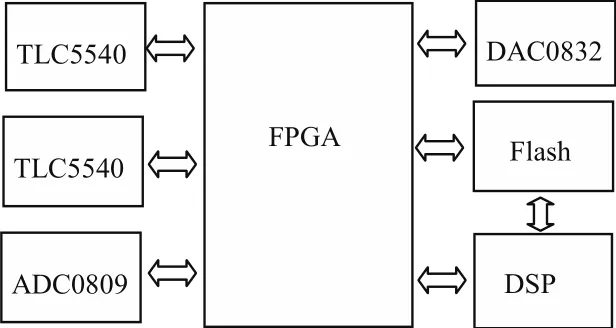

該系統選用現場可編程門陣列(Field Programmable Gate Array,FPGA)為核心處理芯片,FPGA是目前PLD芯片中最常用的一種。它作為專用集成電路(Application Specifi c Integrate Circuit,ASIC)領域中的一種半定制電路而出現,既解決了定制電路功能單一的不足,又克服了原有簡單可編程器件資源有限的缺點。其內部豐富的數字電路資源以及外部IO引腳更加適用于復雜邏輯的數字信號并行處理。該系統中,FPGA完成多路信號的并行采集、存儲以及輸出功能。選用FPGA可以整合傳統數字電路設計中的眾多數字芯片,使得電路體積充分縮減,同時有效地減少電路系統的功耗。

考慮到該系統完成信號處理的復雜程度較高,從運算能力角度來說,僅采用FPGA芯片難以完成復雜信號運算。因此該系統選用一片高速DSP專門用于復雜信號處理和數據運算。

該系統選用一片Flash芯片作為系統的數據存儲器。由于該系統中DSP內部不含EPROM,所以為了能夠獨立運行,當系統脫離仿真環境以后,必須把編譯后的可執行代碼和上電自舉所需的自舉表存儲在外部存儲器之中。另一方面,FPGA的核心結構為SRAM,同樣需要將配置數據存放在片外存儲器中。因此,系統中的Flash芯片除了用于系統工作時的數據存儲之外,還同時存放DSP和Flash的下載程序和配置數據。

系統輸入接口分為模擬和數字兩個部分。模擬部分選擇了2片高速AD和1片低速AD。高速AD為單通道輸入;低速AD可支持8路模擬信號輸入。由于目前低功耗電子系統的廣泛應用,3.3V的LVTTL電平邏輯系統使用越來越廣泛。因此系統的數字輸入部分通過數據總線轉換芯片74LVC16245來實現TTL電平和LVTTL電平信號通用系統。

系統輸出部分選用8位數模轉換芯片以及低通濾波電路作為模擬數據輸出接口。

系統中FPGA,DSP和Flash三種芯片采用3.3V電平邏輯,而AD芯片和DA芯片為5V邏輯電平。因此AD芯片和DA芯片與FPGA連接時,也需要加接數據總線轉換芯片74LVC1624作為電平轉換。系統結構框圖如圖1所示。

圖1 系統結構框圖

2.2 核心芯片選擇

該系統中的FPGA芯片選用美國Altera公司Cyclone II系列芯片中的EP2C8Q208芯片。CycloneII系列芯片是Altera公司推出的新一代低成本FPGA,用于中等復雜度且追求性價比的系統。基于Altera公司的開發環境QuartusII可以對芯片內部硬件資源進行編程并對芯片管腳的功能進行定義。

該系統中的DSP芯片選用美國TI公司5000系列中的TMS3205410芯片。5000系列芯片是TI公司一大類新型而重要的階段性16位定點數字信號處理器,在各種應用領域有著廣泛的應用。

該系統中的Flash芯片選用Spansion公司的S29GL064M芯片,其存儲容量為64Mbit。FPGA芯片EP2C8Q208的配置數據大小約為1.9Mbit,可見該芯片足夠用于存放FPGA配置數據和DSP程序。

該系統中的模數轉換芯片選用了2種,分別為TLC5540和ADC0809。TLC5540是美國TI公司推出的高速8位AD轉換器。它的最高轉換速率可達40MSPS。TLC5540可廣泛應用于數字電視、醫學圖像、視頻會議、CCD掃描儀、高速數據變換及QAM調制器等應用方面。AD0809是美國國家半導體公司生產的8位AD轉換芯片。其最高采樣頻率為10KSPS。但其片內帶有鎖存功能的8路模擬多路開關,因此可以對8路模擬電壓信號分時進行轉換。

該系統中的DA芯片選用8位DAC0832芯片。

2.3 可重構系統實現

FPGA的核心結構由SRAM構成。由于SRAM的掉電易失特性,所以需要把決定FPGA內部的配置數據存放在片外存儲器中,每次加電時,配置數據都必須重新下載。因此對于FPGA來說,并不采用常見的系統編程(In System Programming,ISP)方式下載程序,取而代之的是通過在線配置方式(In Circuit Reconfigurability,ICR)配置數據。基于FPGA的可重構系統是指在FPGA器件已經配置好的情況下,在線進行重新配置,以改變電路邏輯結構和功能。在FPGA工作時,利用FPGA的ICR特性,通過外部控制信號選擇不同的配置數據,經過在線更新后,可以實時改變FPGA內部的電路邏輯結構。

FPGA配置方法有PC機配置、專用芯片配置、微處理器配置等多種方式。PC機配置是指FPGA的配置數據存放在PC機中,由PC機通過下載電纜對FPGA進行系統重構。PC配置法雖然在調試時非常方便,但對于獨立產品來說并不現實。專用配置芯片自帶時序生成系統,使用方便,但只能存放一個配置文件,即FPGA只能實現單一功能,如果需要改變FPGA的結構,只能重新設計、綜合適配后把數據下載到配置芯片中,過程繁瑣。而利用微處理器對FPGA進行配置則可把多個配置文件存放在片內或片外存儲器中,通過微處理器的程序實時選擇不同的配置文件對FPGA進行重構,通過這種方式使得1片FPGA具有多種功能,且能夠進行實時功能切換,具有非常實用的價值。

該系統利用DSP和Flash芯片共同構成FPGA的重構電路,Flash內同時存放了FPGA和DSP的配置程序。兩者配置過程為:

(1)在CCS中編寫編譯DSP應用程序、自舉程序并生成相應二進制代碼。

(2)在QuartusII中設計系統、綜合、適配并生成相應二進制代碼。

(3)在CCS中編寫Flash燒寫程序,下載至DSP。

(4)系統上電,DSP運行燒寫程序,將DSP應用程序、自舉程序、FPGA配置數據全部燒寫進Flash。

(5)斷電脫離PC機。

(6)再次上電,自動運行自舉程序,先后從Flash中把DSP應用程序調入DSP的程序存儲空間,用戶可通過DSP程序隨時從Flash中調出FPGA配置數據并下載到FPGA中,實現FPGA的系統重構。

3 FPGA內部邏輯設計

FPGA內部由TLC5540控制模塊TLC5540Ctrl,ADC0809控制模塊adc0809Ctrl,FIFO存儲器模塊lpm_fifo0,FIFO時序控制模塊AD_data,邏輯運算模塊ALU,Flash控制模塊FlashCtrl和DA控制模塊DACtrl組成。

其中TLC5540Ctrl和adc0809Ctrl模塊用于控制2種AD芯片的工作時序。2個模塊均采用狀態機的設計思路通過VHDL語言編程實現。FIFO模塊用于采樣數據和處理模塊之間的數據緩沖。AD_data模塊用于控制FIFO模塊的工作時序,將AD采樣結果送入FIFO存儲器。ALU模塊完成核心邏輯處理功能,結合上文所述系統重構原理,可實現不同邏輯功能。DACtrl模塊完成DA0832的時序控制,同樣采用狀態機的思路編程實現。FlashCtrl模塊將ALU的運算結果根據需要送入Flash芯片存儲。FPGA內部結構如圖2所示。

圖2 FPGA內部結構圖

4 結束語

針對目前信號處理系統功能越來越強的趨勢,提出了一種基于FPGA技術的多路信號高速采集與處理系統。相比傳統的設計方法,該系統利用FPGA的高速特性及其在電路邏輯設計方面的特點,配合DSP的高速信號處理能力,一方面有效提高了系統處理速度,另一方面簡化了電路結構。特別是利用FPGA的在線可重構特性設計了相應電路,使得系統功能以及靈活性得到顯著的增強。該系統既可作為高校通用信號處理教學平臺,也可作為科研的通用開發系統。

[1] 王宏義,董文娟,黃宗福,等.DSP和FPGA共用Flash進行配置的方法[J].微計算機信息,2008,26:101~102,110

Design of multiple high speed signal reconfi gurable system platform based on FPGA

Zhu Hao, Liu Huajun, Song Yufei

Nanjing institute of technology, Nanjing, 211167, China

This paper introduces the design scheme of multiple high speed signal acquit, store and process system. The demand analysis of modern electronic system is put forward. The structure of hardware is introduced. The resource assign is discussed. The reconfi gurable feature of system is analyzed. The application indicates that this system is fl exible high speed and interference-free. It can be used as utility platform.

FPGA; multiple signals; high speed process; system reconfi gurable

2010-12-01 稿件編號:1012007

朱昊,碩士,講師。

南京工程學院“先進數控技術江蘇省高校重點建設實驗室”。

南京工程學院科研基金項目(編號:KXJ08114),江蘇高校科研成果產業化推進項目(編號:JHZD08-12)。