MOS器件靜電放電潛在性失效概述

楊 潔,武占成,張希軍,胡有志

(軍械工程學院靜電與電磁防護研究所,河北石家莊 050003)

MOS器件靜電放電潛在性失效概述

楊 潔,武占成,張希軍,胡有志

(軍械工程學院靜電與電磁防護研究所,河北石家莊 050003)

各類微電子器件在向著微型化與集成化方向發展的同時,隨之而來的便是其抗靜電放電能力的下降。然而,靜電放電不僅能夠在微電子器件內部造成明顯失效,而且能夠在其內部造成潛在性失效。潛在性失效,是目前最具爭議的一種失效模式,也最具威脅性。國內外研究人員在此方面積極開展了多項研究并取得了較大的進展,他們的研究結果表明:在MOS器件中確實存在靜電放電潛在性失效問題。同時,在他們的研究中對MOS器件靜電放電潛在性失效的損傷機理、檢測方法等進行了相應研究。

靜電放電;MOS器件;潛在性失效;檢測

ESD在微電子器件內部造成的失效按其外部表現可分為明顯失效和隱蔽失效,其中,隱蔽失效又稱潛在性失效,是目前最具爭議的一種失效模式[1-2],也最具威脅性。潛在性失效并不馬上引起電路或設備的癱瘓,甚至不影響器件本身的常規參數,但潛在性失效的存在會導致器件使用壽命的減短,造成使用可靠性下降。部分學者認為在由ESD造成的微電子器件使用失效中,近90%屬于潛在性失效[3]。由于潛在性失效的隱蔽性和不易察覺性導致微電子器件中的此類損傷很難被發現,此類失效模式對微電子器件的可靠性及系統的穩定性影響也最大,尤其是在要求高可靠性的領域中,潛在性失效的影響就顯得尤為重要。

由于檢測手段及方法的限制,直到1982年國外研究人員才第一次完成了有關潛在性失效的系統研究。下面主要從3個方面對MOS器件ESD潛在性失效方面的相關研究進行概述。

1 潛在性失效的試驗研究方法

總結以往的研究過程,對MOS器件潛在性失效的確認主要采用了以下4種試驗方法:1)不同模型ESD注入對失效閾值的影響;2)不同模型ESD注入+電應力試驗;3)ESD注入+熱沖擊試驗、紫外線光照試驗、熱退火試驗或老化試驗;4)極快傳輸線脈沖技術。

無論采用上述那種方法進行試驗,其主要目的就是要觀察受試器件在經歷了ESD后其各項性能或工作能力是否發生變化。

2 潛在性失效的作用規律與失效機理研究

由于潛在性失效是極輕微的損傷,它與器件的表面態、表面晶格結構或是陷阱電荷等有關,采用現有儀器設備很難觀察到其內部結構的微小變化,同時,由于器件本身的性能特點決定器件失效時的微觀機制是復雜多變的,因此器件潛在性失效的微觀機制分析也是復雜的。

1984年,CROCKETT等研究了部分HCMOS集成電路的ESD敏感度與潛在性失效[4],試驗結果表明:低水平的ESD在集成電路內造成潛在性失效,而高水平的ESD造成集成電路出現硬損傷,但最初高水平的ESD可減少潛在性失效的發生。

1985-1986 年間,NEELAKANTASWAMY提出一種潛在性失效模式,是由低水平ESD引發的熱彈性應力積累造成[5]。討論了對于芯片上保護電路的ESD潛在性失效敏感度,可用一種老化概念來模擬由低于閾值的ESD應力造成的積累退化,此方法也可用于分析潛在性失效的數據[6]。

1987年,JON等進行了關于256 KB DRAM器件ESD失效的研究,發現只有大于2μA的漏電流才可顯示潛在性失效的存在,而由低于閾值水平應力造成的ESD潛在性失效的因素總是與局部過熱點的金屬通路有關[7]。

1989年,KRAKAUER等采用電荷抽取技術研究了NMOSFET的氧化物ESD損傷的物理機理,發現:低水平ESD應力和快速恢復應力都使氧化物伴隨表面態變化出現空穴俘獲,潛在性失效存在[8]。

1993年,WILLIAM等通過對2種通用的商用成品CMOS集成電路進行ESD電流注入試驗,發現:低幅度的ESD會在CMOS集成電路內部造成潛在性失效,但一定幅度的ESD也會提高器件的抗ESD能力。隨后,通過對CMOS HEX Inverter進行電應力試驗,得出結論:低壓電應力比高壓的電應力更容易在該類器件內部造成潛在性失效[9]。

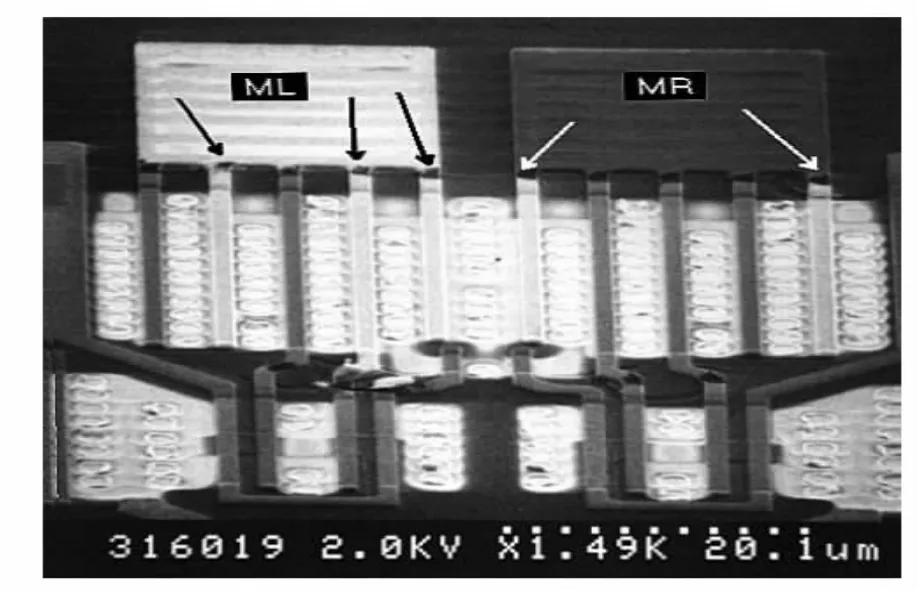

1993年,COLVIN[10]對 CMOS集成電路輸入柵極的潛在性失效進行了驗證和分析,采用掃描電鏡觀察印刷電路板,在ML和MR的柵極連接部位分別顯示了3處和2處的潛在漏電(見圖1)。

1995年,通過SONG等的研究[11]發現:CMOS集成電路中潛在性失效導致的壽命減短與漏電流存在一定的相互關系,主要分為柵極電荷俘獲和漏極與襯底間損傷2種模式。第1種失效模式是由電流直接加在沒有輸入保護電路的NMOS晶體管上,通過柵極注入電荷在柵氧化層出現損傷;另一種失效模式是由于連續電流通過器件漏極造成漏極與襯底間損傷。試驗中采用標準的TDDB測試,發現:第1種失效模式不會造成明顯的壽命減少,而第2種則會;退火效應不會顯著影響TDDB壽命時間;潛在性失效與柵極長度無太大關系;如果有輸入保護電路存在,損傷出現于保護電路中而不是輸入晶體管。

1998年,HUH等采用人體模型、機器模型以及帶電器件模型的ESD對CMOS晶體光和超大規模集成電路進行了潛在性失效的試驗研究[12]。試驗發現:低電壓的人體模型和機器模型ESD造成受試器件漏電增加,而低電壓的帶電器件模型ESD造成受試器件漏電減小。

2004年,GUITARD等的研究表明:在RC保護結構的GCNMOS中,雪崩擊穿可觸發寄生的雙極晶體管,熱效應與強電場共同作用使氧化物滲透擊穿,用EMMI觀察可發現損傷出現在多晶硅柵極下;通過bulk與drain間的漏電測試,可證明損傷由drain-bulk間的金屬絲造成[13]。

對于各種MOS器件,電場的增加使各種失效機理開始顯現,其中主要是大量陷阱的產生和表面態變化[14]。器件的具體工作過程影響很大[15],而高溫退火對體及表面陷阱的影響也已被大量研究[16]。高電場下,漏極附近會產生熱載流子注入氧化層中,注入的載流子可在氧化物中俘獲或產生表面陷阱[17]。電荷俘獲/釋放過程中,各種參數包括柵極厚度[18]、柵極材料[19]和溫度[20]都會對其有所影響。有研究人員認為:ESD潛在性失效主要由于MOS器件中Si/SiO2的不穩定性造成,電荷俘獲是其主要因素;CMOS集成電路中ESD潛在性失效的模型是基于柵氧化物電荷的注入及俘獲[9]。

圖1 發生潛在性失效的CMOS集成電路的SEM PVC圖像

3 ESD潛在性失效的檢測方法研究

關于電子器件各種失效的檢測方法多種多樣,但對潛在性失效的無損檢測方法仍沒有定論。

20世紀90年代,美國學者研究了潛在性ESD/EOS失效、壽命降低和CMOS集成電路漏電流之間的關系[21],并得出結論:漏電流、I-V特性和退火行為都可以用來檢測ESD潛在性失效。

中國學者來萍等人分別通過I-V特性和靜態電流兩方面來標定CMOS電路的潛在性失效[22],潛在性失效的幾種典型模式有:1)氧化層介質和半導體之間的界面擊穿;2)金屬化窗口接角處的PN結損傷或介質-半導體擊穿;3)輸出區NMOS管的漏區接觸孔損傷。特性變化表現為部分輸入或輸出端口的I-V特性變軟,漏電增大。通過I-V特性和靜態小電流都是表征CMOS電路ESD潛在性失效的有效方法,但二者都需要原始參照值。

中國花永鮮和馬仲發[23-24]用低頻噪聲法(LFN法,即測量1/f噪聲)探測ESD潛在性失效進行了實驗研究,發現:1/f噪聲的產生是由位于Si/SiO2界面附近1~3 nm范圍內載流子、陷阱通過散射、俘獲及發射引起的遷移率和數目的漲落所致,此范圍也是ESD的敏感范圍,采用LFN法可以明顯探測到ESD損傷。國外也有學者對用LFN法探測MOS器件ESD潛在性失效進行了專門的試驗研究[13],結果同樣表明LFN法可以探測ESD損傷,而且LFN法要比漏電流靈敏近20倍,比跨導的最大相對退化量要大6倍以上。

除上述方法外,國外研究人員還用三次諧波檢測器件的潛在性失效,發現:它比I-V特性法靈敏10倍[25];利用掃描電鏡的電子感應電流技術(EBIC)檢測C-V曲線變化可表明Si/SiO2界面是否出現損傷點[25];采用掃描激光反射檢溫儀測量10 ns內聚合體鈍化層的溫度空間分布[26];利用俄歇電子能譜分析分析半導體表面分子組成,并研究半導體的表面態變化[27]等等。上述手段均曾用來觀察和分析MOS器件內部的ESD潛在性失效。

4 結 語

自確認ESD潛在性失效的存在已經過去20余年,人們對MOS器件的ESD潛在性失效的認識不斷加深,但仍有許多問題需要深入研究才能解決,如其他微電子器件潛在性失效的表征參數、物理機制的研究、微電子系統的ESD潛在性失效問題以及ESD潛在性失效防護的通用方法等。

[1] MCATEER O J.Electrostatic Discharge Control[M].New York:McGraw-Hill Publishing Company,1989.257-261.

[2] 劉尚合.靜電放電理論與防護[M].北京:兵器工業出版社,1999.180-194,222-230.

[3] 劉尚合,武占成.靜電放電及危害防護[M].北京:北京郵電大學出版社,2004.62-94,128-134.

[4] CROCKETT R G M,SMITH J G,HUGHES J F.ESD sensitivity and latency effects in some HCMOS integrated circuits[A].Proc.EOS/ESD Symp.,EOS-6[C].[S.l.]:EOS/ESD Association Inc,1984.196-201.

[5] NEELAKANTASWAMY P S,SARKAR T K,TURKMAN I R.Residual failures in microelectronic devices due to thermoelastic strains caused by repetitive electrical overstressing:A model for latent failures[A].Proc.EOS/ESD Symp.,EOS-7[C].[S.l.]:EOS/ESD Association Inc,1985.77-83.

[6] NEELAKANTASWAMY P S,TURKMAN R I,SARKAR T K.Susceptibility of on-chip protection circuits to latent failures caused by electrostatic discharges[J].Solid-State Electron,1986,29:677-679.

[7] JON M C,WELSHER T L.The metallurgical study of ESD damage in 256K DRAM devices[A].Proc.EOS/ESD Symp.,EOS-9[C].[S.l.]:EOS/ESD Association Inc,1987.78-87.

[8] KRAKAUER D B,MISTRY K R.On latency and the physical mechanisms underlying gate oxide damage during ESD events in n-channel MOSFET's[A].Proc.EOS/ESD Symp.,EOS-11[C].[S.l.]:EOS/ESD Association Inc,1989.121-126.

[9] WILLIAM D G,ZDENEC K,KENNETH W K.Latent effects due to ESD in CMOS integrated circuits:Review and experiments[J].IEEE Transactions on Industry Application,1993,29(1):88-97.

[10] COLVIN J.The Identification and analysis of latent esd damageon CMOS input gates[A].EOS/ESD Symposium [C].[S.l.]:EOS/ESD Association Inc,1993.109-118.

[11] SONG M,ENG D C,MACWILLIAMS K P.Quantifying ESD/EOS Latent Damage and Integrated Circuit Leakage Currents[A].EOS/ESD Symposium[C].[S.l.]:EOS/ESD Association Inc,1995.304-310.

[12] HUH Y,LEE M G,LEE J.A Study of ESD-induced latent damage in CMOS integrated circuits[A].36th Annual International Reliability Physics Symposium[C].Reno:Nevada,1998.279-283.

[13] GUITARD N,TREMOUILLES D,BAFLEUR M.Low frequency noise measurements for ESD latent defect detection in high reliability applications[J].Microelectronics Reliability,2004,44(6):1 781-1 786.

[14] OZAWA Y,IWASE M,TORIUMI A.Interface state generation due to electron tunneling into thin oxides[A].27th Annual Proceedings,International[C].AZ:[s.n.],1989.22-27.

[15] HOFMANN K,SCHULZ M.Process-induced interface and bulk states in MOS structures[J].Journal Electrochem Soc,1985,132:201-220.

[16] BERGER M,AVNI E,SHAPPIR J.Effect of high-temperature anneal on interface stages generation in stressed metal-oxide-semiconductor devices[J].Applied Phys Lett,1991,58:598-600.

[17] DAVIS M,LAHRI R.Gate oxide charge-to-breakdown correlation to MOSFET hot-electron degradation [J].IEEE Electron Device Lett,1988,9:183-185.

[18] BERGER M,AVNI E,SHAPPIR J.The effect of aluminum gate thickness on charge trapping in metal-oxide-semiconductor devices[J].Applied Phys,1989,66:4 821-4 826.

[19] AVNI E,SONNENBLINK Y,NISSANCOHEN Y.The effect of gate material on oxide degradation due to charge-injection and metaloxide-semiconductor capacitors[J].Solid-State Electron,1988,31:245-250.

[20] 黃瑞毅,劉 發.Ga As微波器件ESD失效機理研究與分析技術[R].廣州:電子工業部第五研究所,1994.

[21] HU C.Hot-electron-induced MOSFET degradation-model,monitor,and improvement[J].IEEE Trans.Electron Devices,1985,32:375-385.

[22] 來 萍,劉 發.探索用靜態小電流參數表征CMOS電路的靜電放電(ESD)潛在性損傷[A].第八界全國可靠性物理學術討論會[C].[S.l.]:[s.n.],1999.42-46.

[23] 馬仲發,莊亦琪,杜 磊,等.一種敏感的MOSFET ESD潛在性損傷檢測方法[J].半導體學報,2002,23(11):1 211-1 216.

[24] 花永鮮,莊亦琪,杜 磊.MOS器件靜電放電潛在性損傷的1/f噪聲檢測方法[J].西安電子科技大學學報(自然科學版),2001,28(5):621-624.

[25] HELLSTR?M Sten.ESD-The Scourge of Electronics[M].London:Springer-Verlag Berlin Heidelberg,1998.

[26] JU Y S,LEUNG Y K,WONG S S,et al.Short-timescale thermal mapping of semiconductor devices[J].IEEE Electron Device Letters,1997,18(5):169-171.

[27] 付 明.半導體器件失效分析與檢測[J].儀表技術與傳感器,1997(12):35-38.

TN4;O441

A

1008-1542(2011)07-0034-04

2011-06-20;責任編輯:李 穆

國家自然科學基金資助項目(60871066;60971042)

楊 潔(1980-),女,河北石家莊人,講師,博士,主要從事微電子器件靜電與電磁效應及防護方面的相關研究工作。