面向集群計(jì)算的專用模塊硬件系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

單芳芳,王 櫻,梁曉艷

(1.中原工學(xué)院,鄭州 450007;2.中興工業(yè)園,廣東深圳 518000)

面向集群計(jì)算的專用模塊硬件系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

單芳芳1,王 櫻1,梁曉艷2

(1.中原工學(xué)院,鄭州 450007;2.中興工業(yè)園,廣東深圳 518000)

介紹了虛擬字符設(shè)備驅(qū)動(dòng)在專用數(shù)據(jù)處理系統(tǒng)中的應(yīng)用,給出了處理器MPC8347通過CPLD對其他芯片進(jìn)行控制的硬件連接設(shè)計(jì),以及系統(tǒng)軟件的關(guān)鍵代碼及流程,為基于M PC8347的同類產(chǎn)品開發(fā)提供參考.

M PC8347;芯片測試;字符設(shè)備驅(qū)動(dòng);上電自檢

在嵌入式計(jì)算機(jī)體系結(jié)構(gòu)中,硬件系統(tǒng)處在體系的底層,其上層有硬件驅(qū)動(dòng)和SOC片上系統(tǒng)及應(yīng)用軟件[1].調(diào)試硬件的繁瑣程度遠(yuǎn)高于調(diào)試軟件,尤其是基于多芯片并存的復(fù)雜硬件系統(tǒng),更需要一種便捷的手段來幫助在硬件系統(tǒng)的設(shè)計(jì)過程中找出并解決存在的問題.本文給出了一種檢驗(yàn)系統(tǒng)正確性的虛擬字符設(shè)備驅(qū)動(dòng)程序,該驅(qū)動(dòng)程序可以對專用數(shù)據(jù)處理芯片進(jìn)行各種不同性質(zhì)的測試并完成系統(tǒng)的上電自檢工作.

1 專用數(shù)據(jù)處理系統(tǒng)結(jié)構(gòu)

1.1 系統(tǒng)設(shè)計(jì)

專用數(shù)據(jù)處理系統(tǒng)的功能是處理請求端通過以太網(wǎng)絡(luò)發(fā)送的數(shù)據(jù),并將處理完成的數(shù)據(jù)返回請求端.專用數(shù)據(jù)處理系統(tǒng)的硬件設(shè)計(jì)采用底板+核心板的模式.系統(tǒng)的結(jié)構(gòu)如圖1所示.核心板承載M PC8347、Flash等核心資源(圖1中層一),底板上焊接專用數(shù)據(jù)處理芯片及CPLD芯片和 FPGA芯片(圖1中層二).CPLD芯片對Local Bus信號譯碼后為各專用數(shù)據(jù)處理芯片(包括 FPGA)提供片選、讀寫、復(fù)位等信號.這樣的設(shè)計(jì)增加了硬件系統(tǒng)的靈活性,方便在底板上布置滿足不同需要的芯片,且利于硬件系統(tǒng)升級.

1.2 CPLD中的控制邏輯設(shè)計(jì)

圖1 硬件系統(tǒng)結(jié)構(gòu)圖

底板上焊接多個(gè)專用數(shù)據(jù)處理芯片,需要M PC8347提供片選、讀寫、復(fù)位等控制信號.這些信號的譯碼部分如用硬件連線沒有靈活性,且一旦設(shè)計(jì)有缺陷,修改起來相當(dāng)麻煩,費(fèi)時(shí)費(fèi)力.用可編程邏輯器件如FPGA(現(xiàn)場可編程門陣列)或CPLD(復(fù)雜可編程邏輯器件)設(shè)計(jì)邏輯轉(zhuǎn)換電路,可以有效解決這些問題[2-3].本文采用CPLD實(shí)現(xiàn)M PC8347同專用數(shù)據(jù)處理芯片之間的控制信號交換,可以簡化系統(tǒng),且保密性好.

CPLD中的片選部分(地址空間分配)示例如下:

CPLD_CS<=(NOT(LBA 11))OR(NOT(LBA 10))OR(LBA 9)OR(LBCS3);

F_CS < =(NO T(LBA 11))OR (NOT(LBA 10))OR(NOT(LBA 9))OR(LBCS3).

用地址線LBA 11-LBA 9在Local Bus地址范圍內(nèi)對底板上所有芯片進(jìn)行地址譯碼.

LBCS3選中的范圍是Local bus的第四個(gè)區(qū)域:0xF9000000-0x Fa000000,該區(qū)域空間大小為16 MB.通過對地址線LBA 11-LBA 9的譯碼得到CPLD的片選信號CPLD_CS和 FPGA的片選信號F_CS,地址分別為0x F9300000和0x F9700000.其他專用數(shù)據(jù)處理芯片也用同樣的方式得到自己的地址.

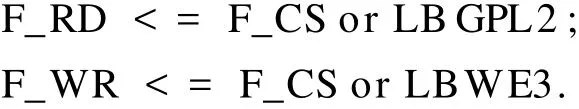

CPLD中讀寫信號部分譯碼示例如下:

其中,LBGPL2是M PC8347提供的Local Bus讀信號,用于控制Local Bus的所有讀操作.LBW E3是M PC8347提供的Local Bus寫信號,用于控制Local Bus的所有寫操作.M PC8347為Local Bus提供的讀寫信號(LBGPL2和LBWE3)或上片選信號(F_CS)作為芯片的讀寫信號(F_RD和F_WR),保證當(dāng)片選和系統(tǒng)的讀寫同時(shí)有效時(shí)M PC8347才對芯片進(jìn)行讀寫操作.其他專用數(shù)據(jù)處理芯片的讀寫信號也用同樣的方式獲得.

CPLD中的其他控制邏輯示例如下:

以上代碼完成FPGA芯片的工作模式選擇.當(dāng)信號CPLD_IO_WR_S的上升沿到來,且LBA 13為0、LBA 12為1時(shí),數(shù)據(jù)線LBD上的數(shù)據(jù)(選擇FPGA工作模式的數(shù)據(jù))被送入 FPGA的模式選擇寄存器FPGA_InReg.其他芯片的模式選擇同上.

2 虛擬字符設(shè)備驅(qū)動(dòng)設(shè)計(jì)

設(shè)備驅(qū)動(dòng)程序是Linux操作系統(tǒng)內(nèi)核的重要組成部分,它在內(nèi)核與硬件設(shè)備之間建立了標(biāo)準(zhǔn)的抽象接口.通過這個(gè)接口,用戶可以像處理普通文件一樣對硬件設(shè)備進(jìn)行打開、讀寫、關(guān)閉等操作.本文采用與設(shè)備無關(guān)的虛擬字符設(shè)備驅(qū)動(dòng)程序完成專用數(shù)據(jù)處理芯片與Linux系統(tǒng)內(nèi)核之間的數(shù)據(jù)交換.

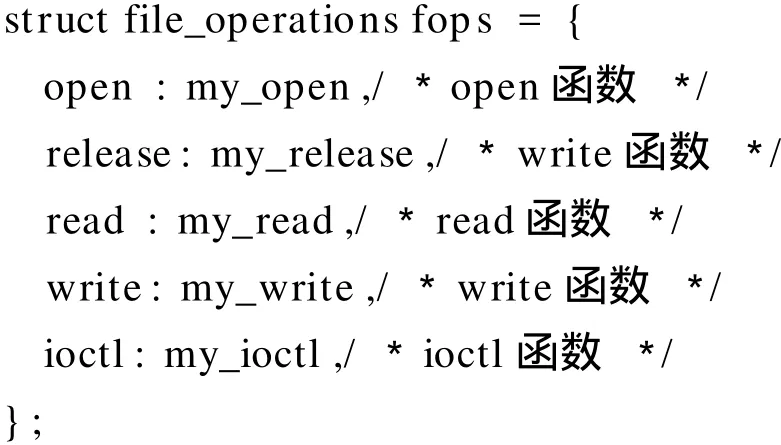

專用數(shù)據(jù)處理系統(tǒng)中的所有數(shù)據(jù)處理芯片被看作同一個(gè)虛擬字符設(shè)備,不同芯片完成該設(shè)備的不同功能.虛擬字符設(shè)備驅(qū)動(dòng)程序?qū)崿F(xiàn)對CPLD和FPGA等芯片的測試.對專用數(shù)據(jù)處理系統(tǒng)硬件進(jìn)行測試時(shí),首先創(chuàng)建虛擬設(shè)備節(jié)點(diǎn),打開虛擬字符設(shè)備,然后加載驅(qū)動(dòng)程序模塊(ppcdriver.o),運(yùn)行應(yīng)用程序testapp.應(yīng)用程序提示用戶輸入進(jìn)行測試的命令碼(例如測試FPGA的命令碼為FPGA TEST).虛擬字符設(shè)備驅(qū)動(dòng)程序根據(jù)不同的命令碼調(diào)用各個(gè)芯片的測試功能[4].定義驅(qū)動(dòng)中文件操作結(jié)構(gòu)如下:

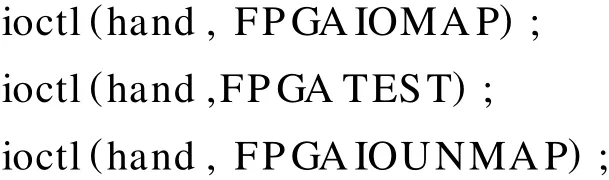

Linux下驅(qū)動(dòng)程序不能直接訪問物理內(nèi)存,為了讓虛擬字符設(shè)備驅(qū)動(dòng)程序可以訪問I/O內(nèi)存,需要利用內(nèi)核提供的內(nèi)存映射函數(shù)把虛擬地址賦予設(shè)備,把虛擬地址指定到 I/O內(nèi)存區(qū)域[5].下面是testapp.c代碼中對FPGA芯片進(jìn)行測試的部分:

用戶在應(yīng)用程序中輸入命令碼FPGA IOM AP,選擇在虛擬字符設(shè)備驅(qū)動(dòng)程序里對FPGA用到的物理地址進(jìn)行映射,接著執(zhí)行 FPGA的測試.測試完成后用命令碼FPGA IOUNM AP對映射過的地址進(jìn)行取消映射操作.命令碼均在虛擬字符設(shè)備驅(qū)動(dòng)程序的ioctl函數(shù)中實(shí)現(xiàn).對物理地址的映射和取消映射操作必須成對出現(xiàn),即映射過的地址必須釋放.

3 軟件系統(tǒng)應(yīng)用

3.1 系統(tǒng)可完成的測試

以FPGA為例,虛擬字符設(shè)備驅(qū)動(dòng)程序可完成其正確性測試、處理器最佳配置測試和數(shù)據(jù)處理速率測試.

(1)正確性測試.根據(jù) FPGA的功能定義,檢測其數(shù)據(jù)處理結(jié)果是否正確.如果不正確,查找硬件故障原因,直到獲得預(yù)期結(jié)果,以保證芯片工作的正確性.

(2)處理器最佳配置測試.該項(xiàng)測試用ioctl函數(shù)中的IOSETREG命令完成.虛擬字符設(shè)備驅(qū)動(dòng)程序不斷修改處理器的2個(gè)參數(shù),同時(shí)驗(yàn)證FPGA芯片工作的正確性,最終得到芯片正常工作時(shí)處理器的最高配置.

修改的2個(gè)處理器參數(shù),一個(gè)是M PC8347插入總線訪問周期的等待時(shí)鐘周期個(gè)數(shù)(OR3寄存器的SCY域),在保證芯片正常工作的前提下,逐漸減小該值,得到插入的最小時(shí)鐘周期數(shù);另一個(gè)是描述M PC8347的系統(tǒng)時(shí)鐘和Local Bus總線時(shí)鐘之間的倍數(shù)關(guān)系(LCRR寄存器的CL KD IV域).

經(jīng)過測試,FPGA的處理器的最佳配置如下:OR3寄存器的SCY域?yàn)?,即M PC8347只有在訪問FPGA的過程中至少插入4個(gè)等待時(shí)鐘周期,FPGA才能正常工作;LCRR寄存器的CL KD IV域?yàn)?,即系統(tǒng)時(shí)鐘頻率是Local Bus總線頻率的2倍時(shí),FPGA能達(dá)到最快速度.

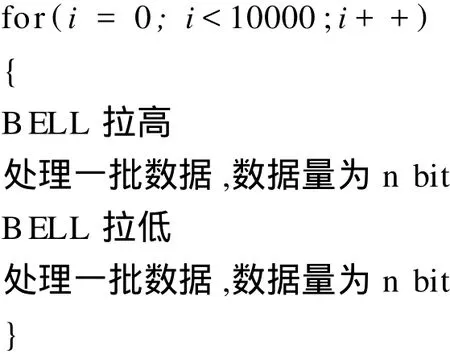

(3)數(shù)據(jù)處理速率測試.虛擬驅(qū)動(dòng)程序控制FPGA連續(xù)處理2批同樣的數(shù)據(jù).在FPGA處理第一批數(shù)據(jù)時(shí),驅(qū)動(dòng)程序?qū)PLD的BELL信號置為高電平;在FPGA處理第二批數(shù)據(jù)時(shí),驅(qū)動(dòng)程序?qū)?CPLD的BELL信號置為低電平.CPLD的BELL信號在FPGA處理這2批數(shù)據(jù)時(shí)形成一個(gè)方波周期,記作t(單位:s),每批數(shù)據(jù)的數(shù)據(jù)量為n(單位:bit);驅(qū)動(dòng)程序重復(fù)執(zhí)行該過程,在BELL信號上產(chǎn)生規(guī)則的方波,記下方波的頻率f(單位:M Hz),通過下面公式計(jì)算得到FPGA芯片的數(shù)據(jù)處理速率v(單位:M bit/s):

v=2nf

虛擬驅(qū)動(dòng)程序中進(jìn)行 FPGA數(shù)據(jù)處理速率測試的偽代碼如下:

3.2 代碼上電自檢

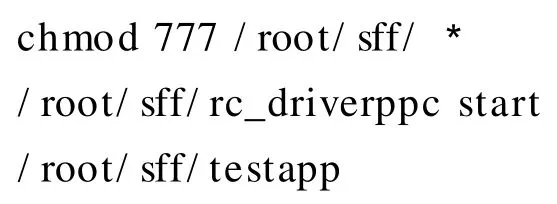

將虛擬驅(qū)動(dòng)程序模塊和應(yīng)用程序的可執(zhí)行文件加入文件系統(tǒng)ramdisk中,修改ramdisk中的腳本文件rc,將需要執(zhí)行的內(nèi)容加入腳本文件末尾.需要加入的執(zhí)行內(nèi)容如下:

修改后的腳本文件使系統(tǒng)啟動(dòng)時(shí)自動(dòng)進(jìn)行虛擬驅(qū)動(dòng)程序的加載和應(yīng)用程序的執(zhí)行,達(dá)到系統(tǒng)上電自檢的效果.

4 結(jié) 語

論文完成對專用數(shù)據(jù)處理系統(tǒng)正確性的檢驗(yàn),得到專用數(shù)據(jù)處理芯片發(fā)揮最大效率的M PC8347配置參數(shù).虛擬字符設(shè)備驅(qū)動(dòng)程序成功輔助專用數(shù)據(jù)處理系統(tǒng)的硬件設(shè)計(jì),并為編寫處理批量數(shù)據(jù)的代碼奠定基礎(chǔ).

[1]陳冬旭,程小輝,龔幼民.基于UML的嵌入式硬件系統(tǒng)模型研究[J].微計(jì)算機(jī)信息 ,2008,3(2):88-89.

[2]胡振華.VHDL與FPGA設(shè)計(jì)[M].北京:中國鐵道出版社,2003:1-10.

[3]Charles H Roth Jr,Lizy Kurian John.數(shù)字系統(tǒng)設(shè)計(jì)與VHDL[M].第2版.北京:電子工業(yè)出版社,2008:5-8.

[4]Jonathan Corbet,A lessandro,Greg Kroah-Hartman.L INUX設(shè)備驅(qū)動(dòng)程序[M].第3版.魏永明,耿岳,鐘書毅譯.北京:中國電力出版社,2005:7-80.

[5]倪繼利Linux內(nèi)核分析及編程[M].北京:電子工業(yè)出版社,2005:92-100.

Design and Realization of Virtual Character Device Driver in Special Data Processing System

SHAN Fang-fang1,WANG Ying1,L IANG Xiao-yan2

(Zhongyuan University of Technology,Zhengzhou 450007,China)

Thispaper introducesan app lication of Virtual Character Device Driver in Special Data Processing System.Cpu controls the other chips through doing operations on CPLD,design of connection between hardw are is discussed.Key part of system softw are and code flow are also discussed here.A nd this paper gives useful in other similar p roduct design.

M PC8347;chip test;character device driver;pow er on self-check

TP309

A

10.3969/j.issn.1671-6906.2011.01.018

1671-6906(2011)01-0066-04

2011-01-24

單芳芳(1984-),女,河南鄭州人,碩士.