高速采集系統的時鐘端接設計與仿真*

白紅蕊,馬秀榮,白 媛,吳 健

(天津理工大學計算機與通信工程學院,通信器件教育部工程研究中心,天津 300384)

目前對高速采集系統的要求越來越高,緊耦合的LVPECL(Low-voltage Positive Referenced Emitter Coupled Logic)差分時鐘能夠更好地抑制其他動態網絡的干擾,從而使其布線方式成為高速時鐘信號的主要互連結構[1]。然而若不對差分時鐘信號進行恰當的端接設計,時鐘信號將會感受到阻抗突變,產生的反射噪聲會導致時鐘信號頻率不穩定,采集的數據不準確[2-3]。因此合理的LVPECL 差分信號端接方法設計是確保高速采集系統可靠性的重要工作之一。

對于LVPECL 差分時鐘信號的端接設計,國內外學者進行了大量的研究。文獻[4]研究了單端PECL/ECL 典型的端接設計方法,但沒有考慮交流耦合和差分PECL/ECL 信號的情況;文獻[5-6]中研究了LVPECL 差分驅動直流、交流耦合的端接設計方法,但該方法只考慮差分信號阻抗匹配,而未考慮單端阻抗匹配,導致單端信號反射引起振鈴現象,破壞差分時鐘和其它信號的特性。在深入分析上述方法的優劣基礎上,提出了一種改進的LVPECL 差分時鐘信號端接設計,有效地抑制單端信號的反射噪聲,為高速采集系統差分時鐘的互連設計提供了一種新思路。

1 基于AD9254 的高速數據采集系統

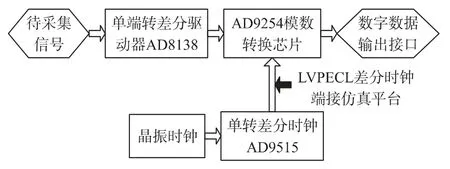

文中以基于AD9254 數據采集系統為仿真平臺,在Cadence 環境下,分別對常用的交流耦合端接和改進的LVPECL 差分信號端接設計進行了仿真實驗。基于AD9254 高速數據采集系統整體結構框圖,如圖1所示。一路待采集的信號通過差分放大模塊后傳送到模數轉換芯片作為采樣數據,另一路為溫控晶振產生的時鐘信號通過可編譯調整的差分時鐘模塊后傳送到模數轉換芯片作為采樣時鐘。

圖1 AD 高速數據采集系統整體結構框圖

數模轉換芯片采用美國AD 公司推出AD9254 150 Msample/s(每秒百萬次采樣)轉換速率14 bit分辨率的模數轉換器。時鐘分配芯片采用1.6 GHz兩輸出,頻率和延時可調的AD9515。時鐘端接設計對應與框圖中AD9515 驅動端和AD9254 接收端之間。只有合理的端接才能確保時鐘信號的完整性。因此,下面對端接設計進行理論分析。

2 高速采集系統時鐘端接設計分析

2.1 常用的交流耦合端接方法

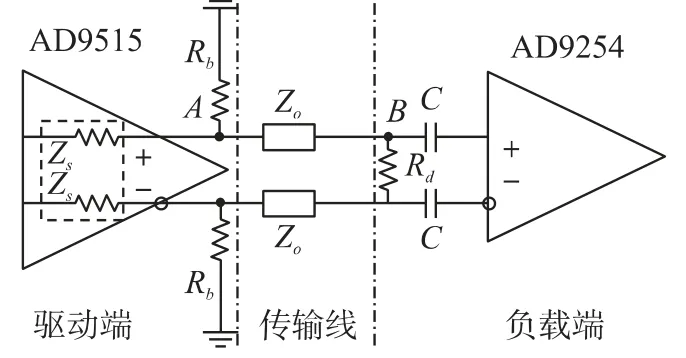

LVPECL 常用的交流耦合端接設計方法如圖2所示。整個端接方法由驅動端、傳輸線和負載端3 部分組成。

圖2 常用的交流耦合端接方法

驅動端部分的Zs為其單端等效輸出阻抗,Rb為單端直流偏置電阻,它的作用是為LVPECL 單端信號的靜態電平提供電流回路,滿足標準負載電流IL的要求。已知LVPECL 信號輸出正、負端的靜態電平典型值均為VCC-1.3V(VCC為器件的電源電壓),IL為14 mA。LVPECL 信號輸出電壓幅度為VLVPECL。故Rb一般近似采用:

傳輸線部分的Z0為傳輸線的特征阻抗。

負載端的C為隔直電容,Rd為差分端接負載,它的作用是對LVPECL 差分信號進行阻抗匹配,抑制差分信號的反射。Rd應為:

Rdiff為差分阻抗。

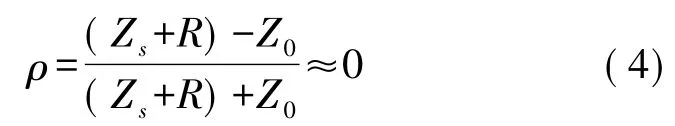

由圖2 的分析可知,當輸出阻抗Zs和傳輸線阻抗Z0不匹配時,反射系數ρ[7]可表示為:

故信號在圖2 中點A 處感受到阻抗突變,從而在端接中引起了反射噪聲,出現了振鈴現象。

當反射噪聲轉化為差模噪聲時就會破壞時鐘信號的差分特性。雖然信號在圖2 中點B 端接了差分阻抗,抑制差分信號的反射,但由于點A 處引起的反射噪聲已經破壞信號的差分特性,故交流耦合端接方法中接收的差分信號并不能完全消除在點A處引起的反射噪聲。

可見,常用的差分交流耦合端接方法只進行了差分輸出阻抗匹配,而沒有進行單端輸出阻抗匹配,從而引起的LVPECL 單端反射噪聲破壞了差分信號的差分特性。

2.2 改進的LVPECL 差分時鐘信號端接方法

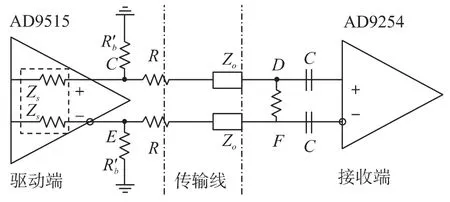

本文提出一種改進的LVPECL 差分時鐘信號端接方法,將單端匹配設計引入到端接設計中,從而改善單端反射噪聲的抑制效果。改進的LVPECL 差分時鐘信號端接方法如圖3所示。

圖3 改進的LVPECL 差分時鐘信號端接方法

與常用的差分交流耦合端接方法相比,圖3 驅動端引入了串聯阻抗匹配電阻R,它的作用是保證LVPECL 單端信號的Zs和R 的串聯與Z0相匹配,使反射系數ρ 近似為0,消除反射噪聲。當R=ZOZS時,

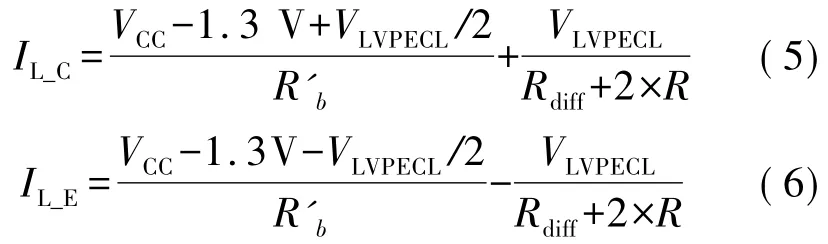

R′b為直流偏置電阻。因為R 的引入,使得R′b與圖2 中Rb不同。已知C、E點輸出的是差分時鐘信號,假定某一時刻C點電壓為相對高,IL_C、IL_E分別為流過C、E點的負載電流,根據電路結構可知:

根據上述公式可知IL_C>IL_E,為了確保電流最大時仍滿足IL負載電流要求,因此R′b應為

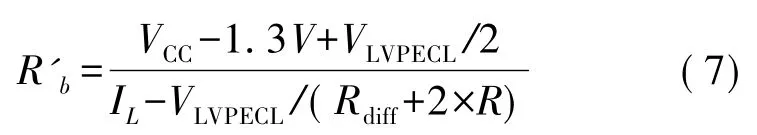

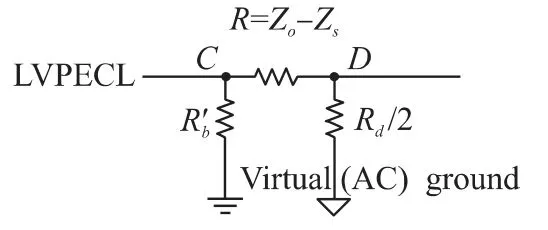

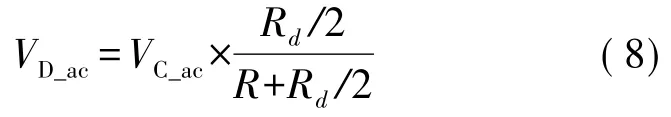

除此之外,R 的引入也使得端接設計構成一個電阻衰減網絡,如圖4所示。

圖4 電阻衰減網絡

LVPECL 差分時鐘信號經過電阻衰減網絡,和為圖4 中C、D 的交流電壓。則有

因此在設計端接方法的時候,R、R′b參數的選擇不僅要考慮滿足抑制反射的要求,同時要折中考慮VD_ac滿足常用負載端輸入高、低電平的范圍要求,一般輸入時鐘信號高低電平的要求為0~0.8 V為低電平,1.2-VCC為高電平。

3 仿真參數確定和仿真平臺搭建

3.1 仿真參數確定

AD9515 差分時鐘信號配置為LVPECL 差分信號輸出,傳輸線為差分微帶線。

根據AD9254、AD9515 的封裝,確定線寬W=10 mil;介質高度H=6 mil;覆銅厚度T=1.35 mil;介電常數Er=4.2;差分線寬S=6 mil。通過微帶線特性和Polar_si9000 傳輸線場分析器求解[8-9],計算得出:Z0=51.01Ω;Zdiff=87Ω。

根據AD9515 IBIS模型可知其輸出阻抗ZS≈8Ω,選取R≈40Ω,Rdiff≈100Ω,Rb=240Ω,R′b=200Ω。由以上參量可以確定≈0.555×VLVPECL,滿足接收端輸入差分時鐘信號要求。通過負載端接收的差分信號過沖來衡量系統抑制反射噪聲的能力。

3.2 仿真平臺搭建

在Cadence SI 軟件中建立圖2、圖3所示的拓撲結構。

首先,將驗證后的IBIS(Input/Output Buffer Information Specification)仿真模型加載到Cadence SI仿真軟件中。IBIS模型[10-11]是一種行為模型,通過V/I和V/T 曲線描述器件管腳的輸入、輸出的電氣特性,而不涉及器件內部電路的組成。IBIS模型常用于板級信號完整性分析,通過仿真觀察不同器件間傳輸線路中的信號完整性問題。

其次,根據圖2、圖3所示端接方法建立相應的拓撲結構。且由于芯片封裝與基本元器件焊接需要一定的空間間隙,故在驅動端輸出信號處和接收端接收信號處分別加入100 mil 的差分微帶線。

然后,設置結構中的激勵源采用100 MHz 時鐘信號。差分微帶線的參數按照§4.1 中的參數定義,其它器件參數根據圖2、圖3 中的參數確定。

4 仿真結果與分析

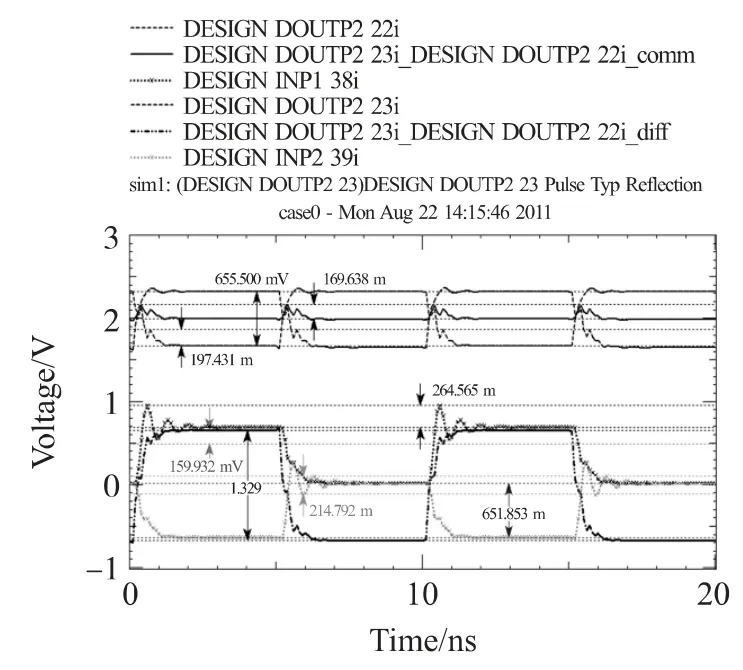

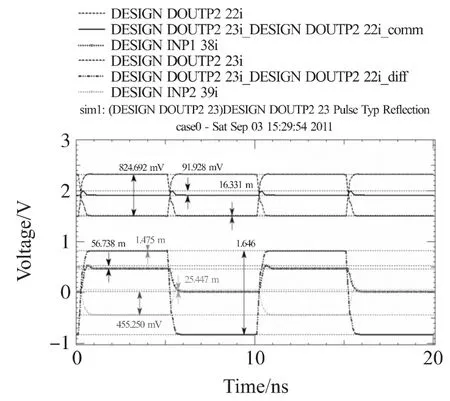

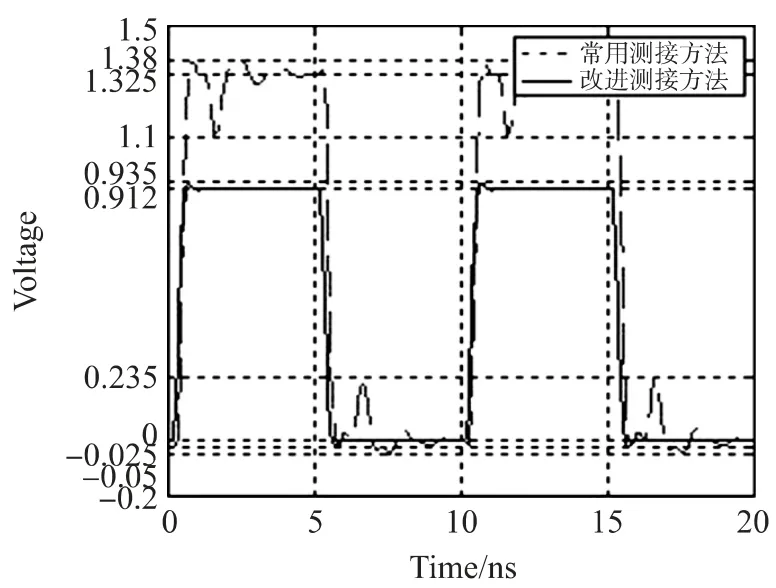

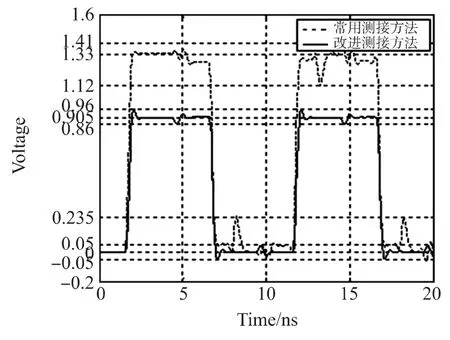

時鐘信號頻率為100 MHz、傳輸距離為200 mil時兩種端接方法仿真結果如圖5、圖6、圖7和表1所示,鑒于電壓過沖量是衡量反射噪聲的重要指標[12],用過沖做反射噪聲抑制的衡量指標。

圖5 常用的交流耦合端接的仿真結果

圖6 改進的LVPECL 差分時鐘信號端接方法

圖7 接收的兩路差分時鐘信號差分后的信號

4.1 改進的端接方法對反射噪聲的抑制仿真

圖5、圖6 中虛線DESIGN DOUTP22i和23i為驅動端AD9515 輸出的兩路差分時鐘信號,點劃線DESIGN DOUTP23i_DOUTP22i_diff為兩路差分時鐘信號差分后的信號;帶星號的虛線DESIGN INP38i和39i為AD9254 負載端接收的兩路差分時鐘信號,兩路差分后的信號如圖7所示。圖7 中實線為常用的交流耦合端接設計的仿真結果,虛線為改進的LVPECL 差分端接的仿真結果。相應的最大電壓過沖見圖中標注。

圖5、圖7 表明常用的交流耦合端接中驅動端輸出的兩路差分時鐘信號差分后的信號(圖5 中點劃線DESIGN DOUTP23i_DOUTP22i_diff)和負載端接收的兩路差分時鐘信號差分后的信號(圖7 中虛線)存在反射噪聲,信號抖動明顯;而圖6、圖7 表明改進的端接中相應的差分后信號(圖6 中的點劃線DESIGN DOUTP23i_DOUTP22i_diff和圖6 中的實線)幾乎沒有反射噪聲,信號抖動很小。

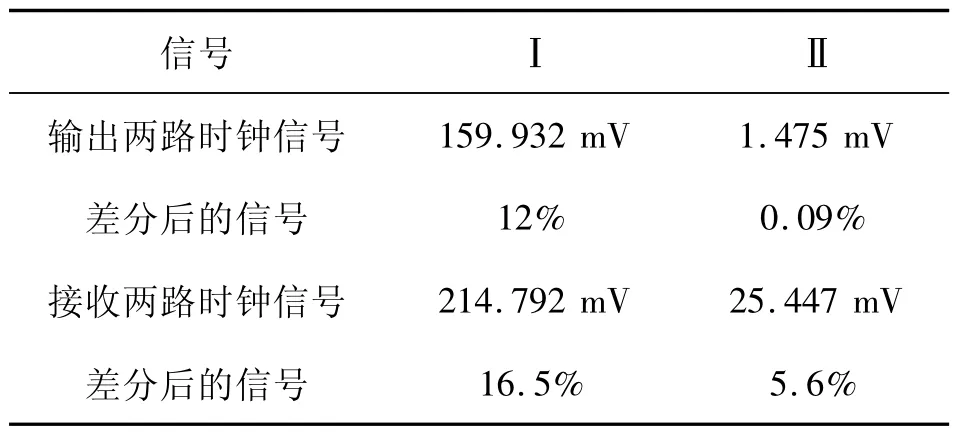

驅動端輸出和負載端接收的兩路差分時鐘信號差分后的信號是關鍵信號。關鍵信號的過沖及其占相應信號電平峰峰值(Vp-p)的百分比,如表1所示。

表1 不同端接設計的仿真結果

表中“Ⅰ”代表常用的差分交流耦合端接,“Ⅱ”代表本文改進的LVPECL 差分時鐘信號端接。由表1可以看出Ⅰ中輸出信號存在反射噪聲,破壞接收端信號差分特性,接收的差分后信號過沖214.792 mV,占Vp-p 的16.5%;而Ⅱ中幾乎沒有反射噪聲,信號抖動很小,接收的信號差分特性良好,電壓過沖在25.447 mV,占Vp-p 的5.6%,過沖比前者減少了10.9%。

由此可知,改進的端接方法可以很好地抑制反射噪聲。下面分析不同傳輸距離和信號頻率時,改進的端接方法對反射噪聲的抑制情況。

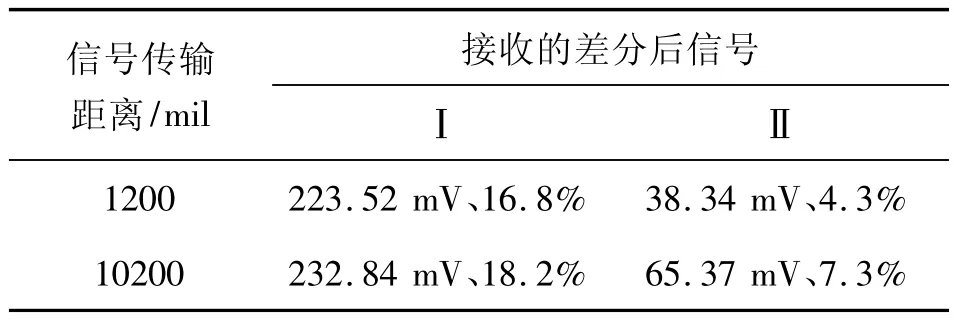

4.2 不同傳輸距離下端接抑制反射噪聲的仿真

為了分析傳輸距離的增加會加大對對信號失真度完整性的影響,為驗證改進的端接方式在不同傳輸距離下的反射噪聲的抑制情況,本文對不同端接在傳輸距離分別為1200 mil、10 200 mil,信號頻率為100 MHz 時進行仿真實驗,仿真的結果如圖8和表2。

圖8 傳輸距離10 200 mil 時接收差分信號

表2 傳輸距離為1 200 mil、10 200 mil 的仿真結果

圖8 中實線為常用交流耦合端接設計的仿真結果;虛線為改進的LVPECL 差分信號端接的仿真結果,實線和虛線分別代表相應端接負載端接收的兩路差分時鐘信號差分后的信號。

圖8和表2 數據表明當傳輸距離增加時,負載端接收的差分后信號電壓過沖有一定的增加但是變化不大,在表2 的Ⅰ中交流耦合中最小過沖為223.52 mV,占Vp-p 的16.8%;而在Ⅱ改進的LVPECL 差分時鐘信號端接過沖最大為65.37 mV,占Vp-p 的7.3%。由此可見,當傳輸距離小于10 200 mil 時改進的LVPECL 差分時鐘信號端接與交流耦合端接方法相比,能夠更好地抑制差分時鐘信號的反射噪聲。

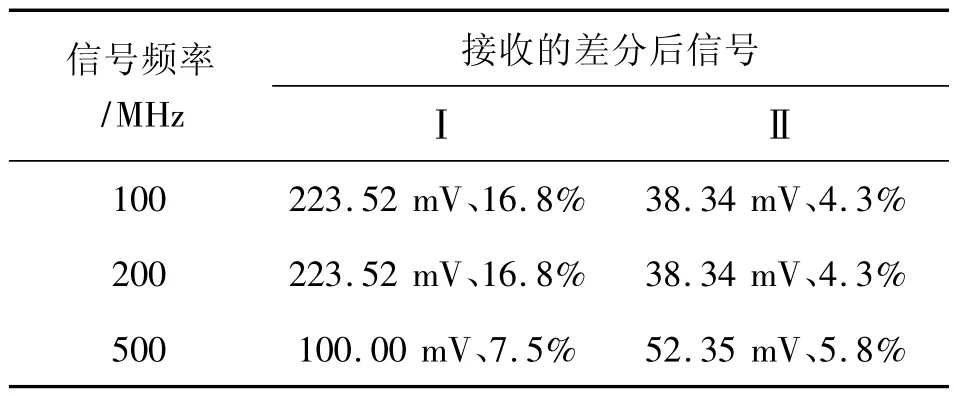

4.3 不同信號頻率下端接抑制反射噪聲的仿真

端接適合的頻率范圍是需要進一步分析的。因此,對文中提到的兩種端接在信號頻率分別為100 MHz、200 MHz、500 MHz,傳輸距離為1 200 mil 時進行仿真實驗。接收的兩路差分時鐘信號差分后的信號(簡稱差分后信號)的過沖以及其占相應信號電壓峰峰值(Vp-p)的百分比,如表3所示。

表3 信號頻率為100 MHz、200 MHz、500 MHz 的仿真結果

當輸入信號小于200 MHz 時負載端接收的差分后信號電壓過沖基本保持不變,在表3Ⅰ交流耦合中約223 mV,占Vp-p 的16.8%,而在Ⅱ串聯交流耦合中約40 mV,占Vp-p 的4.3%,與Ⅰ相比過沖占Vp-p 的百分比減少了12.5%;當信號頻率在200 MHz~500MHz 之間時,Ⅰ中負載端接收差分后信號過沖隨著頻率增加逐漸減小至100 mV,最小占Vp-p的7.5%,而在Ⅱ中差分后信號過沖在52.35 mV 以下,最大占Vp-p 的5.8%。數據表明信號頻率在500 MHz 以下時,與交流耦合端接方法相比,改進的LVPECL 差分時鐘信號端接能夠更好地抑制差分時鐘信號的反射噪聲。

5 結論

本文針對差分時鐘信號在高速數據采集系統中存在的信號完整性問題,提出了一種改進的端接設計方法,進行了理論和實驗仿真分析。通過基于AD9254 的高速數據采集系統實例對不同端接設計進行仿真,驗證信號頻率小于500 MHz、傳輸距離在10 200 mil 內時,常用的交流耦合端接中接收差分信號過沖在232.84 mV 以下,最大占Vp-p 的18.2%;而改進的LVPECL 差分時鐘信號端接中接收到的差分時鐘信號過沖在65.37 mV 以下,最大占Vp-p 的7.3%,過沖占比Vp-p 的百分比比前者減少了10.9%。因此,當信號小于500 MHz 時,與常用端接相比,改進的LVPECL 差分時鐘信號端接能夠更好地抑制反射噪聲,改善了高速數據采集系統中差分時鐘信號完整性問題,提高系統的穩定性和準確度。

[1]袁智勇,何金良,陳水明.印刷電路板差分線邊緣布置的電磁兼容分析[J].電波科學學報,2004,19(6):689-693.

[2]郭土華,徐曉.基于高速嵌入式系統的信號完整性分析[J].電子技術應用,2011,37(1):55-57.

[3]陳建華,牛中奇.基于有限元法分析低電壓差分驅動電路的輻射特性[J].微波學報,2008,24(3):61-66.

[4]Boni A.1.2-Gb/s True PECL 100K Compatible I/O Interface in 0.35-μm CMOS[J].Solid-State Circuits,IEEE Journal of,2001,36(6):979-987.

[5]鄢若韞,閆景富.數據傳輸系統中PECL 電平的接口設計[J].微計算機應用,2008,29(8):109-112.

[6]趙增輝,劉中友,彭圻平.高速差分信號的互連設計[J].無線電通信技術,2010,36(1):50-53.

[7]鄧集杰,劉鐵根,褚備,等.高速視頻處理系統的信號完整性分析[J].電子測量與儀器學報,2009,23(6):34-41.

[8]Zhang M S,Li Y S,Jia C,et al.Signal Integrity Analysis of the Traces in Electromagnetic-Bandgap Structure in High-Speed Printed Circuit Boards and Packages[J].Microwave Theory and Techniques,IEEE Transactions on,2007,55(5):1054-1062.

[9]Johnson H,Graham M.High-Speed Digital Design[M].Beijing:Publishing House of Electronic Industry,2004.

[10]李成,程曉宇,畢篤彥,等.基于HyperLynx 的高速DSP 系統信號完整性仿真研究[J].電子器件,2009,32(2):445-451.

[11]李廣輝,莊奕琪,曾志斌.基于信號完整性分析的一種視頻處理系統設計[J].電子器件,2007,30(4):1325-1328.

[12]張艷麗,安琪,王硯方.基于PCB 仿真的高速時鐘電路設計研究[J].計算機仿真,2004,21(9):175-178.