一種基于RS485的SoC產品測試平臺的設計

黃世震,陳麗紅

(福州大學福建省微電子集成電路重點實驗室,福州350002)

隨著集成電路和半導體工藝技術的發展,在單一集成電路芯片上就可以實現一個復雜的電子系統,如智能卡、SD卡等,SoC正是在集成電路向集成系統轉變的大方向下產生的。由于SoC產品的功能模塊比較多,一般從封裝廠里出來后,要對各個功能模塊進一步測試,從而剔除不良品,然后根據不同的用途對產品進行初始化,完成測試過程。在產品的批量生產過程中,傳統的測試方法采用人工手動測試,存在幾個問題:①效率低,無法滿足SoC產品對時間的要求;②測試結果容易受人為因素的影響,無法滿足SoC產品對可靠性的要求。本文提出一種基于RS485總線的自動化批量測試系統的設計方法,以現有的封裝廠測試平臺為基礎,通過自行研制一些測試板,與現有的測試平臺對接,實現SoC產品的自動化批量測試,提高生產效率。文中將以一款TF卡為例,在介紹完測試平臺的硬件結構之后,側重介紹測試平臺的軟件設計方法。

1 測試平臺概述

RS485總線是業界應用最廣泛的標準通信接口之一。它采用平衡發送和差分接收方式實現通信:發送端將串行口的TTL電平信號轉換成差分信號A、B兩路輸出,經過線纜傳輸之后在接收端將差分信號還原成TTL電平信號。由于傳輸線通常使用雙絞線,又是差分傳輸,所以有極強的抗共模干擾的能力,傳輸距離在1 000 m以上,可互聯多達256個節點,非常適合組成成本低廉的多機通信系統。RS485是一個多引出線接口,這個接口可以有多個驅動器和接收器,采用主從式通信方式,可以實現一臺上位機與多臺下位機之間的串行通信。這種通信方式特別適合應用于本測試平臺中[1]。

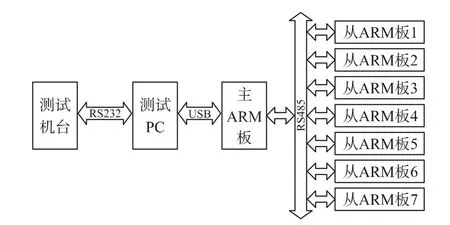

測試平臺主要包含3個部分,即測試機臺、測試PC和主從ARM測試板。測試機臺負責待測產品的安裝、測試的啟動和按照測試結果進行分類;測試PC負責發送測試機臺的啟動命令、對主ARM測試板發送命令以及將測試結果反饋給測試機臺;主ARM測試板負責接收測試PC的測試命令,并將其分發給多個從ARM測試板以及收集從測試板的測試結果反饋給測試PC。測試平臺連接圖如圖1所示。

圖1 測試平臺連接圖

具體的實施方法為:將測試機臺、測試PC、主從ARM測試板連接起來,測試機臺將測試樣品送入測試接口,然后通知測試PC啟動測試,測試PC通過USB接口發送測試命令給主ARM測試板,主ARM測試板通過RS485總線通知所有從ARM測試板啟動測試,每塊ARM測試板(包括主ARM測試版)按照程序對樣品中的模塊進行測試,并將測試結果反饋給主測試板,主測試板將結果匯總后反饋給測試PC,測試PC再將結果反饋給測試機臺,最后測試機臺根據測試結果對各個測試樣品進行分類放置,放入新的測試樣品,啟動下一輪測試。

2 測試平臺硬件設計

2.1 測試板硬件設計

測試板采用32 bit高性能ARM核微處理器S3C2416,根據嵌入式系統的最小系統設計原理,進行接口設計和硬件設計,使測試板滿足測試需要[2-4]。測試板的硬件框圖如圖2所示。

圖2 測試板硬件框圖

主要電路功能簡介如下:

電源電路 為整個系統供電,要求穩定性高。測試板上有多個系統電壓,5 V,3.3 V,1.3 V,1.2 V等,能夠滿足SoC產品的測試需要。

復位電路 完成系統的上電復位和系統在運行時用戶的按鍵復位功能;

系統時鐘電路 使用外部晶振起振,提供時鐘信號。本測試系統使用12 M晶振時鐘;

JTAG電路 測試平臺調試與測試接口,控制芯片的運行并獲取內部信息;

USART/SPI等接口 用于滿足不同SoC產品測試時的時序要求;

RS485接口電路 采用SN65HVD33芯片構成,微處理器的標準串行口通過RXD直接連接SN65HVD33芯片的R引腳,通過TXD直接連接SN65HVD33芯片的 D引腳。微處理器的 GPD3、GPD4引腳分別和SN65HVD33芯片的RE和DE相連,控制SN65HVD33芯片的發送器/接收器使能:SN65HVD33發送器有效時,微處理器可以向RS485總線發送字節;SN65HVD33接收器有效時,微處理器可以接受來自RS485總線的數據字節。任一時刻SN65HVD33芯片中的接收器和發送器只能有1個處于工作狀態[1]。

2.2 測試板編碼設計

由于RS485總線是采用半雙工通信方式,每次只能有一對節點進行通信,故要求每塊測試板有自己的地址編號[5]。本測試平臺共有4組,每組中都包含8塊ARM測試板,設計時在每塊ARM測試板上都裝上8個撥碼開關,其中低4位(4∶1)表示從ARM測試板的編號,高4位(5∶8)表示主ARM測試板編號,有效編號為0~7。由于主ARM測試板在完成通信的同時也需要進行樣品測試,其本身也相當于一塊從ARM測試板,因此其撥碼開關的低四位始終設置為0,其編號為0,其它7塊從ARM測試板編號為1~7。這樣就保證了地址編號的唯一性,能夠滿足RS485通訊的要求。例如:若撥碼開關的狀態為00100001,則表示該測試板為第2組中的第2(編號為1)塊測試板,為從測試板;而主測試板的編號默認為0,若撥碼開關的狀態為00100000,則表示該測試板為第2組中的第1(編號為0)塊測試板,為主測試板。

3 測試平臺軟件設計

3.1 測試PC端軟件設計

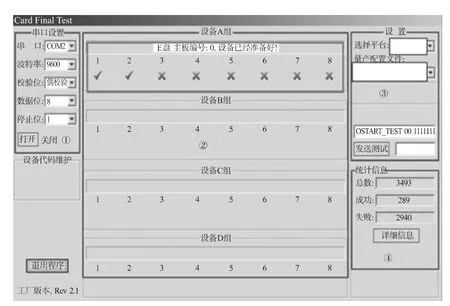

測試PC端軟件采用VC6.0編程實現,串口的通信編程利用了COMM串行通信控件,方便地訪問串口,實現數據的接收和發送[6]。測試PC端顯示界面主要包括測試PC端與主從ARM測試板的通信狀態、測試板的測試結果等。

測試軟件通過RS232接收機臺命令,并控制測試板進行相應的測試。以一種SoC產品-TF卡為例,其測試界面如圖3所示。

其中區①為串口參數設置欄,測試開始前須檢查串口號及參數設置與機臺端是否一致,然后打開串口;區②為設備狀態欄,顯示運行時各個測試板的狀態,例如上圖中在A組(主板編號為1)設備中,只有第1塊(主測試板)與第2塊測試板連接正常,可以進行測試,其余各測試板不能進行測試。區③為其他功能欄,其中“發送測試”用于手動測試過程,實際機臺自動測試過程中不需使用;“量產配置文件”用于針對不同類型的TF卡選擇不同的配置信息;“選擇平臺”用于生產不同類型的TF卡。區④為統計信息欄,顯示測試總數、成功的次數、失敗的次數。

圖3 生產測試工具主頁面

測試完成界面如圖4所示。

圖4 測試完成界面

3.2 主ARM測試板軟件設計

主ARM測試板接收測試PC發送的USB命令,根據命令運行相應的測試程序,同時將命令廣播給從ARM測試板,啟動所有ARM測試板的測試,并將測試結果反饋給測試PC。主ARM測試板控制流程如圖5所示。

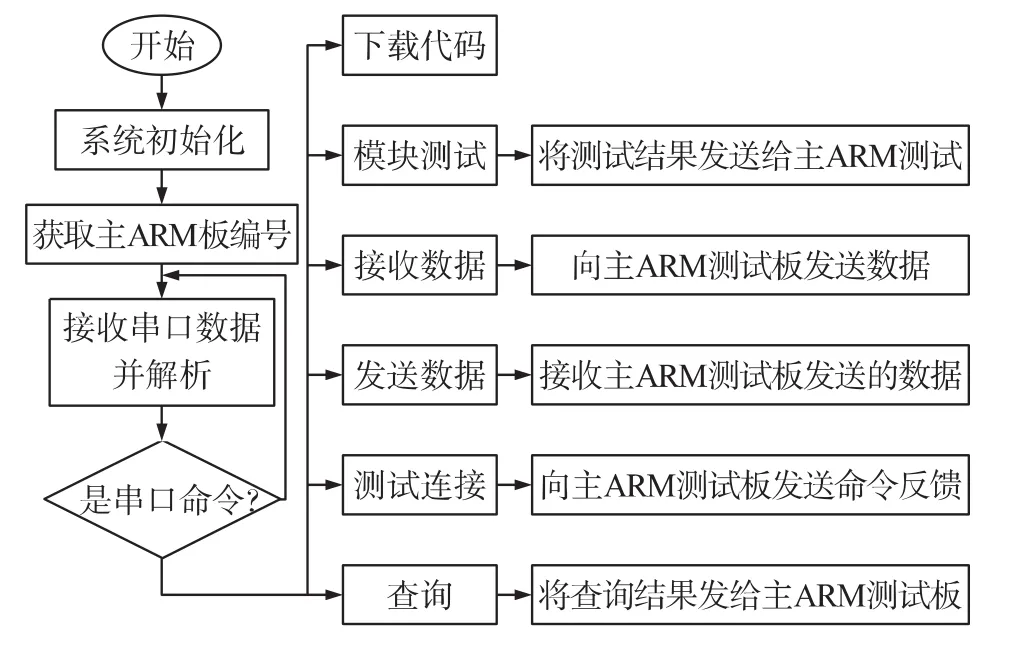

3.3 從ARM測試板軟件設計

從ARM測試板接收串口數據并解析,根據命令運行相應程序,并向主ARM板發送反饋信息。從ARM測試板控制流程如圖6所示。

圖5 主ARM測試板控制流程圖

圖6 從ARM測試板控制流程圖

3.4 主從ARM測試板通訊協議設計

3.4.1 幀格式

RS485總線只制定了物理層電氣標準,對上層通信協議沒有規定,這給設計者提供了很大的靈活性。一套完整的通訊協議應從多個方面加以考慮,既要求結構簡單、功能完備,又要求具有可擴充性與兼容性,并且盡量標準化。本測試平臺采用的通訊協議是在充分考慮到平臺本身的功能特點,再參考國際標準通信規約的基礎上制定的,適用于主ARM測試板與各個從ARM測試板進行點對點的或一主多從的數據交換方式,具體如下:

主ARM測試板命令幀:

頭碼 地址碼 操作命令 數據字段 校驗和 尾碼1 byte 1 byte 1 byte DATA CS 1 byte

從ARM測試板響應幀:

頭碼 地址碼 狀態反饋 數據字段 校驗和 尾碼1 byte 1 byte 1 byte DATA CS 1 byte

頭碼 數據幀起始標志,用于觸發通信,本協議中規定以“FF”為頭碼。

地址碼 從ARM測試板的地址編碼,設定范圍:1~7,0為廣播通信地址。

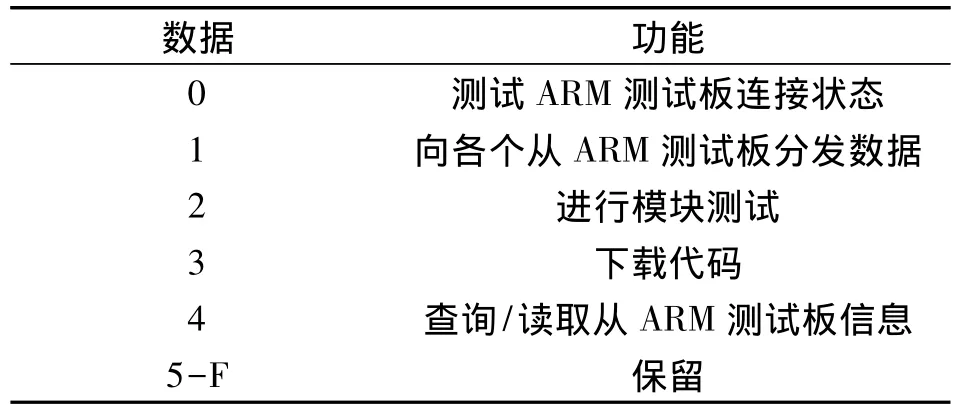

操作命令 操作命令存在于主ARM測試板發送的數據幀中,用于定義發送此次數據幀要完成的任務。根據操作命令的不同,幀長度也有所不同。操作命令為一個字節長度,每一位代表不同的內容對應不同的命令代碼,具體內容如下所示。

數據 功能0測試ARM測試板連接狀態向各個從ARM測試板分發數據2進行模塊測試3下載代碼4查詢/讀取從ARM測試板信息5-F 保留1

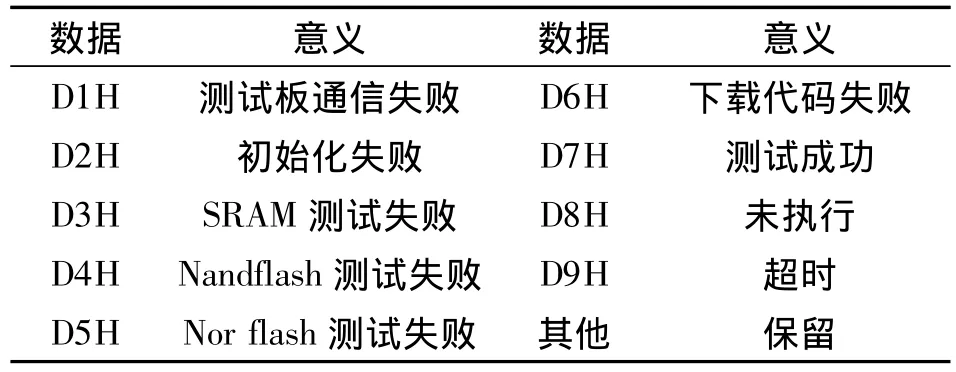

狀態反饋 從ARM測試板對主ARM測試板的響應,主要用于回饋從ARM測試板對主ARM測試板命令幀的執行情況。從ARM測試板響應定義如下:

數據 意義 數據 意義D1H 測試板通信失敗 D6H 下載代碼失敗D2H 初始化失敗 D7H 測試成功D3H SRAM測試失敗 D8H 未執行D4H Nandflash測試失敗 D9H 超時D5H Nor flash測試失敗 其他 保留

數據字段 本字段分兩部分,第1部分為一個字節,表示整個數據字段的字節數,L=0表示無數據域。第2部分則為通信中要傳輸的數據內容,傳輸內容的長度隨著操作命令而改變。

校驗和 從地址碼開始到校驗和之前的所有字節的模256的和。

尾碼 數據幀結束標志,本協議中規定以“DD”為尾碼[7-8]。3.4.2 通信過程

主ARM測試板與從ARM測試板構成的多機通信系統采用主從式結構,數據通信總是由主ARM測試板發起。主ARM測試板處于發送狀態時,從ARM測試板總是處于接收狀態。主ARM測試板定時向從ARM測試板發送地址幀,這時每塊從ARM測試板都中斷接收并與本機地址比較,若主ARM測試板發送的地址信息與本從ARM測試板的編號相符,則接收該數據,否則繼續接收總線上的數據。若從ARM測試板需要發送數據,則必須等到主測試板輪詢過該從ARM測試板時,才可提出請求。這種網絡模式下,從ARM測試板不會“偵聽”其他從ARM測試板對主ARM測試板的響應,這樣就不會對其他從ARM測試板產生錯誤的響應。

當主ARM測試板發出數據幀后,如果在規定的時間內沒有收到從機的應答幀,則主機認為幀丟失并重發數據幀;如果發送3次仍沒有收到應答幀,則系統認為該次通信失敗,報錯[5,9]。

4 結論

本文提出了一種基于RS485總線的SoC產品自動化批量測試平臺的設計,并以一種TF卡為例介紹了測試平臺的硬件設計和軟件設計。目前該測試平臺已應用于測試廠TF卡的各模塊(Nor flash、Nandflash、SRAM)的測試,經批量測試結果表明,使用該測試平臺1 h測試TF數量為傳統測試方法的32倍,顯著地提高了生產和測試的效率。

[1]廣州周立功單片機發展有限公司.RS485協議標準[S].周立功公司,2004.

[2]杜春雷.ARM體系結構與編程[M].北京:清華大學出版社,2003.

[3]馬忠梅等.ARM嵌入式處理器結構與應用基礎[M].北京:航空航天大學出版社,2001.

[4]ARM 公司.ARM Architecture Reference Manual[S].ARM 公司,2000.

[5]范越等.基于RS485總線的自動化檢測系統的研制[J].現代電子技術,2008.(05):142-144.

[6]謝春萍,陳鐵軍.基于RS485的多機串行通信系統的設計[J].玉林師范學院學報,2006.(05):158-161.

[7]李圣明,曹玉強,孫清.基于 RS485總線的分布式測控系統[J].儀表技術與傳感器,2004.(11):22-24.

[8]謝軍芳.基于RS485的分布式整流橋測試系統[J].硅谷,2008.(19):45-46.

[9]張冰.一種電子產品老化測試系統的設計與實現[J].工業控制計算機,2007.(20):13-14.