基于TotalRecall技術ASIC的FPGA原型驗證

郭安華,黃世震

(福州大學福建省微電子集成電路重點實驗室,福州350002)

目前ASIC設計的規模及復雜度正在呈指數增加,在帶來實現高性能芯片系統可能性的同時,也帶來了前所未有的芯片驗證問題,驗證和調試所占的時間可以達到總工期的70%以上[1]。驗證的方法有多種可以選擇,如軟件模擬、硬件加速模擬、硬件仿真及基于FPGA原型設計驗證等,這些方法各有利弊。而FPGA原型驗證方法一方面可使設計者可以較好的把握硬件設計的物理特性,硬件平臺能夠重復利用;另一方面基于FPGA的原型驗證平臺可以比軟件仿真速度高出4~6個數量級,填補了仿真環境與實際芯片的巨大差距。因此,FPGA原型驗證具有很高的性價比。

本文主要描述運用ToalRecall技術結合FPGA原型的一款鼠標芯片ASIC驗證平臺的實現過程。

1 驗證方法概述

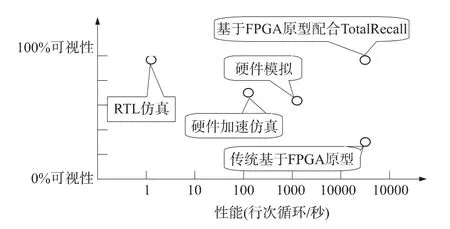

傳統的驗證方法有軟件模擬、硬件加速模擬、硬件仿真及基于FPGA原型驗證等[2],軟件模擬成本很低但驗證花費時間長,而基于FPGA的原型設計驗證方法不僅成本低,而且速度很快。硬件加速模擬及仿真的速度比軟件模擬速度快很多,但比FPGA驗證法慢很多,且其成本要比上述兩種方法高很多,所以基于FPGA原型設計驗證方法具有最高性價比。但傳統基于FPGA原型設計驗證的明顯缺點是缺乏對內部信號、狀態及寄存器內容的可視性。而結合ToalRecall技術的FPGA原型驗證方法提供了100%的可視性,還能以實時硬件速度運行。各種驗證方法的可視性對比如圖1所示。

圖1 各種設計驗證方法的可視性對比

2 ASIC芯片架構

ASIC,即專用集成電路,是指應特定要求和特定電子系統的需要而設計、制造的集成電路。本文所描述的芯片是一款鼠標芯片。圖2是設計的鼠標芯片的系統架構框圖,它包含 DSP模塊,ROM,SRAM,Sensor,LED 驅動,系統控制,USB 接口控制器模塊,電壓電路,時鐘電路,復位電路等。

圖2 ASIC框圖

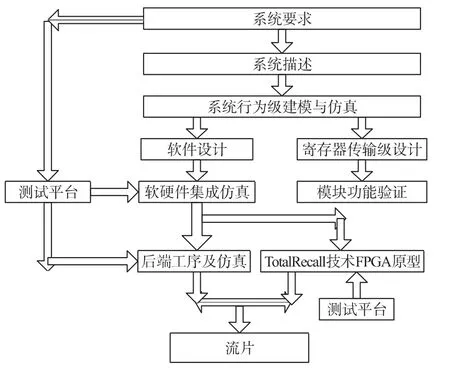

3 結合TotalRecall技術的ASIC設計流程

基于加入TotalRecall技術FPGA原型驗證的ASIC設計的基本流程如圖3所示[3]。

圖3 結合TotalRecall技術FPGA原型的ASIC設計的基本流程

由于FPGA技術的快速發展,FPGA在資源、速度、性能等方面都得到了較大的改善,FPGA在密度、速度方面和ASIC的相似性使得基于FPGA的原型運行速度接近于現實速度,不僅可以大大提高系統的仿真速度,而且還可以讓我們盡早地來測試應用軟件,從而達到節省整個ASIC開發時間的目的。

4 結合TotalRecall技術FPGA原型的設計實現

4.1 TotalRecall技術概述

TotalRecall技術結合FPGA原型可以解決傳統基于FPGA原型設計驗證系統的可視性問題,該驗證方法在提供100%可視性的同時,還可保證FPGA以實時硬件速度運行。

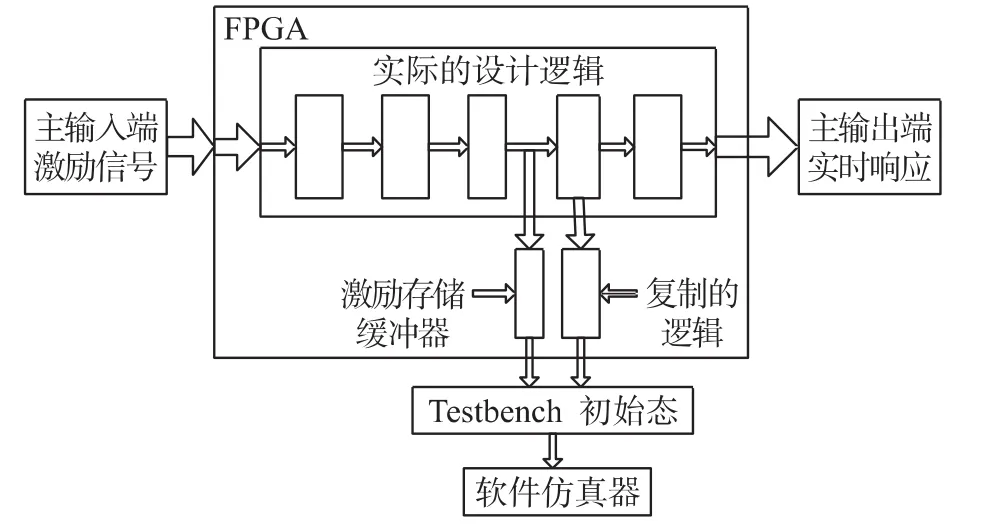

TotalRecall技術的原理是在FPGA內部復制邏輯,然后存儲該復制邏輯的激勵,同時延遲其應用。圖4是TotalRecall的原理,主輸入端的激勵信號直接輸入實際邏輯塊,輸出端的實時響應由此邏輯塊產生。同時,原始測試矢量也輸入作為緩沖器的存儲區。當檢測到輸出端的錯誤響應時,復制邏輯及其相應存儲緩沖器將暫停。此時,激勵存儲緩沖器內容及復制邏輯內容狀態由FPGA器件的JTAG端口導出,并用于軟件仿真器。

4.2 驗證板介紹

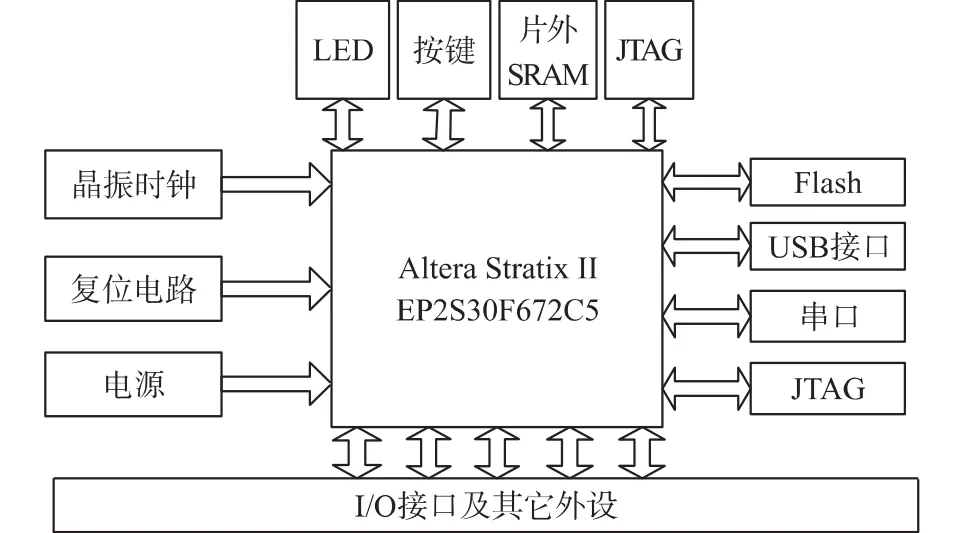

如圖5所示,FPGA驗證板采用了Altera公司的StratixⅡEP2S30F672C5型號的可編程邏輯芯片,包含27 104個查找表的資源[4],完全可以滿足項目的需要。驗證板上還提供了一般系統的電壓,板級的晶振及板級上電復位源,為了方便驗證板的使用,驗證板上還集成了一些外設及常用的系統接口。此外驗證板上還引出了大量FPGA的IO口用于功能擴展。

圖5 FPGA驗證板

4.3 設計的轉換[5]

采用FPGA原型技術驗證ASIC設計時,首先需要把ASIC設計轉化為FPGA設計。但ASIC是基于標準單元庫,FPGA則是基于查找表,ASIC和FPGA物理結構上的不同,決定了ASIC代碼需要一定的轉換才能移植到FPGA上,但這只是由于物理結構不同而對代碼進行的轉換,并不改變其功能。需要轉換的代碼主要有以下幾個方面:

(1)時鐘單元

ASIC中的時鐘從時鐘源出發,經若干層時鐘緩沖器到達每個寄存器的時鐘端,形成所謂的時鐘樹結構。ASIC時鐘樹的插入主要由布局布線工具自動完成,利用代工廠的 PLL進行時鐘設計。而FPGA中通常配置了一定數量的PLL宏單元,且有針對時鐘優化的全局時鐘網絡,可以保證相同的時鐘沿到達芯片內部每個觸發器的延遲時間差異是可以忽略的,所以時鐘單元是需要轉換的。

(2)存儲單元

ASIC中的存儲單元通常用代工廠所提供的Memory Compiler來定制,通常是不能綜合的。而FPGA提供了經過驗證并優化的存儲單元。所以存儲單元必須要進行代碼轉換的。

(3)增加流水

由于實現結構上的不同,PFGA器件內部的單元延時遠大于ASIC的基本門單元延時。

從而在同樣設計的情況下,ASIC可以滿足時序,而FPGA有可能無法滿足。為了驗證的需要,對ASIC實現的流水結構在FPGA實現時需要適當增加流水。

(4)同步設計

在FPGA設計中,同步設計是非常重要的,當從ASIC轉向FPGA設計時,需要進行同步。在ASIC的設計中,為了減少功耗,使用了門控時鐘,但由于設計的異步特性,對于FPGA來說,使用這種門控時鐘容易產生毛刺,導致數據不正確。所以在FPGA設計中,使用使能信號的電路來代替門控時鐘電路。

4.4 模擬部分的整合

FPGA是現場可編程邏輯器件,只能實現數字電路,模擬電路無法在FPGA中實現。要驗證這些模擬IP核,可以選用同樣功能的芯片或者這些模擬IP核的樣片來代替,與FPGA共同實現它們的功能,其中比較重要的幾個模擬IP轉換的方案如下所述[6]:

(1)系統電源由FPGA驗證板提供的電壓源來實現;

(2)系統復位可由FPGA板級上電復位源作為系統復位信號實現;

(3)系統中的Sensor和ADC由樣片和相同功能的芯片來實現;

(4)系統中ROM和SRAM可由FPGA內部的RAM及外部的SRAM實現;

(5)系統時鐘由振蕩器提供,采用FPGA板的晶振作為時鐘源。

5 結合TotalRecall技術FPGA原型的驗證

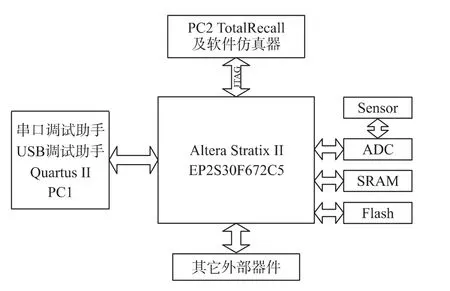

結合TotalRecall技術FPGA原型驗證平臺的整體結構如圖6所示,此平臺主要由PC機、FPGA、Flash、SRAM、Sensor樣片、ADC芯片、按鍵、串口、USB接口及一些其它的外設等組成。在PC1機上安裝Altera的FPGA軟件 QuartusⅡ,上位機 PC1通過 Altera usb blaster下載線與驗證平臺上FPGA的JTAG接口相連,這樣就實現了上位機上QuartusⅡ軟件與驗證板上FPGA之間的連接,使用QuartusⅡ軟件通過Altera usb blaster下載線把完全編譯好的工程下載到驗證板上。在PC2上TotalRecall也通過JTAG與FPGA板相連,可為FPGA驗證系統提供100%的可視性。

圖6 驗證平臺的整體結構

驗證可以分為模塊級驗證、系統級驗證兩個層次,在進行設計原型驗證時,首先應該保證驗證平臺各個模塊的正確性,對各模塊進行驗證[7]。下面以驗證系統中的USB控制器模塊為例,說明結合TotalRecall技術FPGA原型驗證平臺對設計模塊的驗證。根據USB2.0協議,USB鼠標接口主要有四個信號線:電源、地、D+及D-,且它具有兩種通信方式,一種是主機到設備的通信,另一種是設備到主機的通信。利用USB鼠標接口的D+和D-信號就可以對其進行通信驗證。具體驗證過程如下:首先,我們在上位機PC1上用VC[8]開發一個USB調試助手,由于FPGA原型驗證平臺提供了USB接口的外設,所以可以直接利用此外設來接受USB調試助手發送的數據指令,并把這些數據指令傳送到USB控制器。同時也可以接受USB控制器模塊反應的數據指令,并把它傳送到上位機PC1上的USB調試助手上。我們可以把接受到的反應數據指令與期望的值做個比較,看兩者是否一致,從而來驗證USB接口控制器模塊的正確性。當接受的響應數據與期望的值不同時,即發生了故障,可以利用TotalRecall技術復制USB控制器功能塊。如圖7所示TotalRecall技術應用于設計驗證系統中的功能塊,TotalRecall技術能夠生成局部Testbench,專門用于測試掛起功能塊。此時,激勵存儲緩沖器內容及復制的邏輯內容由FPGA器件的JTAG端口導出,并用于軟件仿真器。TotalRecall技術可以定位到故障前數百甚至上千個周期前的狀態值,用來對軟件仿真器進行初始化設置。這樣,USB控制器功能塊就能夠在實時硬件速度下提供100%的可視性,并且還能在熟悉的軟件仿真環境下跟蹤故障,從而快速的定位及解決故障,使USB控制器功能塊得到完全的驗證。

圖7 TotalRecall技術應用于系統功能塊

6 結束語

基于FPGA原型驗證對于ASIC驗證是一個非常實用的方法,結合TotalRecall技術的FPGA原型驗證方法可以有效解決傳統FPGA原型驗證可視性差的弊端。該方法不僅能夠快速檢測、調試并解決深藏的偶發及間發故障,這些故障有時會出現在實時激勵的情況下或由軟硬件之間復雜的非確定性互動引起,而且還能提供我們在熟悉的軟件仿真環境中跟蹤故障。從而大大提高了芯片驗證的效率,縮短芯片開發的時間。

[1]馬鳳翔,孫義和.SoC原型驗證技術的研究[J].電子技術應用,2005.3

[2]姚遠,張曉琳,張展.基于FPGA的可層疊組合式SoC原型系統設計[J].電子技術應用,2009,9

[3]濮津,林孝康.內嵌ARM9E內核系統級芯片的原型驗證方法[J].微計算機信息,2005.

[4]王誠,蔡海寧,吳繼華.Altera FPFA/CPLD設計(基礎篇)[M].人民郵電出版社,2011.

[5]章瑋.原型驗證過程中的ASIC到FPGA的代碼轉換[J].今日電子,2006,(7).

[6]楊安生,黃世震.基于ARM SoC的FPGA原型驗證[J].電子器件,2011.3

[7]黃麗.百萬門級專用集成電路的FPGA驗證平臺[D].西安:西安電子科技大學,2007.

[8]潘愛明,王國印.Visual C++技術內幕[M].北京:清華大學出版社,1999.