500fps圖像采集及實時顯示關鍵技術研究*

侯宏錄,高偉平

(西安工業大學 光電工程學院,陜西 西安 710021)

引 言

高幀頻相機是研究物體的高速運動或瞬態流逝現象的有效工具,廣泛應用于航空、航天以及武器系統等領域,研究高速運動物體的運動規律,在武器試驗領域可對艦載、機載導彈發射姿態進行實時記錄與跟蹤,對其性能進行分析等,為武器系統試驗驗證提供決策依據。

長期以來,中國的高幀頻相機主要依賴于進口,盡管進口相機的幀頻達到了1 000fps,可分辨率很低,且使用條件僅限于民用,所采用的技術不對外公開,可借鑒的文獻極少。國內目前研究高幀頻相機的單位極少,長春光機所在2008 年研制的高幀頻互補金屬氧化物半導體(complementary metal oxide semiconductor,CMOS)實時圖像采集系統能夠滿足高速圖像數據的采集與處理,且畫面清晰,但該系統采用Camera Link接口實現數據的傳輸,通過PCI圖像采集卡將數據采集到計算機上進行處理及顯示,系統體積較大,不符合機載相機體積小的要求[1]。

本文所研究的高幀頻圖像采集系統的分辨率為1 024×1 280,采集幀頻為500fps,對實時圖像采集和數據處理的要求很高。采用Cypress公司130萬像數的LUPA1300-2型CMOS圖像傳感器捕獲圖像信息,以現場可編程門陣列(field-programmable gate array,FPGA)為核心處理單元來完成500fps的圖像數據采集及實時顯示,對圖像數據的采集,色彩復原,先入先出隊列(first in first out,FIFO)緩存,同步動態隨機存儲器(synchronous dynamic random access memory,SDRAM)存貯及VGA 顯示進行的研究,可滿足機載、艦載和車載環境下高機動性、小型一體化的需求。

1 圖像采集系統的總體方案分析

由于要對高速運動物體的瞬態圖像進行拍攝,如爆炸瞬間,導彈發射瞬間等,需要較高的分辨率及幀頻,為滿足需求,所研究的500fps圖像采集與實時顯示系統的主要技術參數有:

拍攝幀頻:500fps;

采集像素數:1 024×1 280;

數據位寬:10bit。

由系統的主要技術參數可以計算出高幀頻數字圖像傳感器的圖像信息輸出速度為781.25 MB/s,并且LUPA1300-2圖像傳感器輸出格式為Bayer格式,需要轉化為RGB格式,格式轉化后在FPGA 內部的傳輸速度為2343.75 MB/s[2]。由此可見,系統的數據處理量很大,對FPGA、緩存器件的性能及數據處理算法的要求很高。由于幀頻很高,不需要人眼實時觀察全過程,僅觀察變化規律即可,因此在實時顯示環節,采用抽幀顯示的方式,可以減小系統的數據處理負擔,增加系統的穩定性。

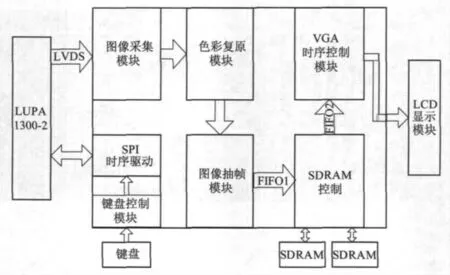

本文選用Altera公司的Cyclone II系列EP2C35型號的FPGA 芯片作為核心處理單元,系統有低壓差分信號(low-voltage differential signaling,LVDS)支持,接收端最高805 Mbit/s 數據速率,支持SDRAM、DDR2SDRAM 器件,使系統的硬件結構更為簡單。系統的總體框圖如圖1所示。

圖1 圖像采集系統的總體框圖Fig.1 The general block diagram of image acquisition system

系統工作時首先通過鍵盤啟動數字圖像傳感器LUPA1300-2,FPGA 通過串行外設接口(serial peripheral interface,SPI)總線將默認參數傳輸到LUPA1300-2,如曝光時間、像素數、開窗區域等,并對整個系統進行初始化設置。系統啟動完成后由LUPA1300-2捕獲高速運動目標的瞬態圖像信息,通過高速LVDS接口將Bayer格式的圖像傳輸到圖像采集模塊,由色彩復原模塊對完成圖像色彩重建,轉化為RGB格式圖像。圖像抽幀模塊每20幀抽取一幀圖像,且通過FIFO1緩存存儲到SDRAM 中,由FIFO2讀取SDRAM 中暫存的圖像信息并傳輸到VGA 接口,最終在LCD 上實時顯示[3]。

2 圖像采集模塊設計

圖像采集模塊對LVDS信號進行串行數據解析,得到同步信息碼,還原出正常的圖像同步信息。如行有效信號,場有效信號等,最終完成對圖像信息的采集。

LUPA1300-2是Cypress公司推出的針對機器視覺和運動分析的高性能的CMOS圖像傳感器,它能夠提供無失真圖像并執行快速讀出。LUPA1300-2在1 024×1 280分辨率下可實現500fps的圖像采集,利用視窗或子采樣讀取模式可以達到更高的幀速率;采用12路10位ADC 的LVDS以DDR 方式輸出,每通道像素率最大為630Mbit/s;采用管線化全局同步快門成像,可有效避免拍攝高速運動所產生的影像模糊和圖像畸變;通過SPI接口對CMOS 傳感器內部寄存器配置,控制傳感器的工作狀態,控制方式簡單、靈活;輸出圖像格式為Bayer格式,要在傳感器外部完成色彩重建[4]。

2.1 LUPA1300-2工作時序

LUPA1300-2 的工作流程分為如下幾步:初始化復位、訓練模式、配置片內寄存器、像素光積分、圖像信號放大和量化輸出。

LUPA1300-2在工作時首先通過RESET_N 對傳感器的片載序列發生器、內部寄存器和時序電路進行復位;復位完成后啟動訓練模式,確保讀出圖像數據的正確性;然后通過SPI總線對片內寄存器進行配置,主要包括傳感器的幀頻、曝光時間、開窗、光積分模式等;寄存器配置完成后開始對圖像進行捕獲、圖像信號放大、LVDS量化輸出。

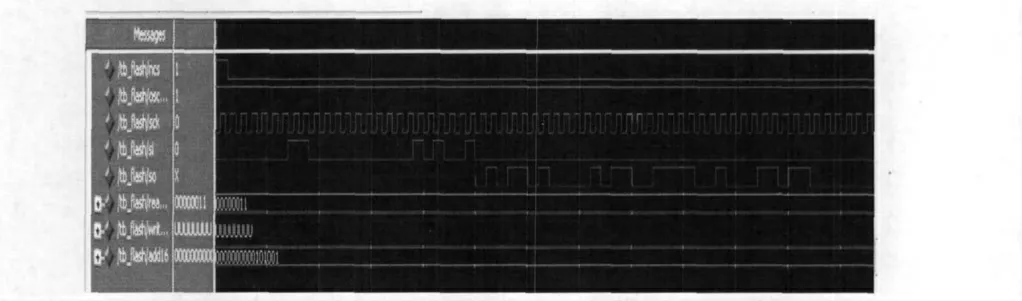

2.2 SPI總線時序驅動

FPGA 通過SPI總線對LUPA1300-2內部105個寄存器進行配置,以使傳感器能夠正常工作。SPI總線有CS、CLK、IN、OUT 四條信號線。CLK 提供接口同步時鐘,最高速率為主時鐘的三十分之一。每組數據有16位,第1位為讀寫控制命令位,第2~8位為內部寄存器的地址位,第9~16位為數據位,對應于傳感器的寄存器配置參數。其中SPI讀時序的仿真圖如圖2所示。

圖2 SPI總線讀時序仿真圖Fig.2 The simulation of SPI bus read timing sequence

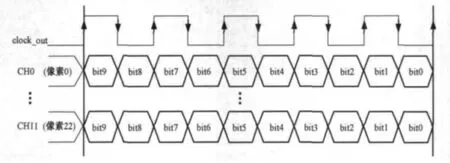

2.3 LVDS信號接收

LUPA1300-2輸出的圖像數據通過LVDS接口以DDR方式輸出,每24個像數為一個核單元,每一行總共有54個核單元。每個核單元按照一定的次序,分2次在12個通路中,以雙倍數據速率串行輸出。先輸出第0、2、4…22個像數,再輸出第1、3、5…23個像數,接著再輸出47、45、43…25個像數,再輸出第46、44、42…24個像數,以此類推,直至輸出1行的所有像數數據[5]。數據通道與像素時鐘的相位關系如圖3所示。

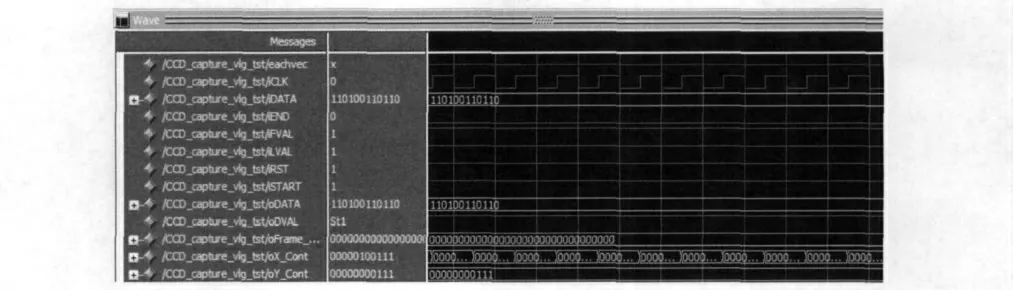

FPGA 在接收到LUPA1300-2 的圖像數據后,進過串行數據解析和像素重組,得到場標識信號iFVAL,行標識信號iLVAL和像素信號[11:0]iDATA,復位信號iRST,開始信號iSTART 和結束信號iEND,然后通過對這些信號的時序控制,接收到正確的圖像數據。

最終在ModelSim 中仿真得到圖像采集仿真圖如圖4所示。

圖3 數據通道與像素時鐘的相位關系Fig.3 The phase relationship of the data channel with the pixel clock

圖4 圖像采集模塊仿真圖Fig.4 The simulation of image acquisition modules

3 SDRAM 緩存設計

在實時顯示圖像信息時,盡管進行了抽幀,但數據處理量仍然很大,僅靠FPGA 內部的存儲空間無法滿足需求,需要高速、大容量的存儲器來緩存圖像數據,采用SDRAM 對圖像進行緩存。但FPGA 的時鐘,SDRAM 的時鐘及VGA 的時鐘均不相同,需要采用FIFO 將兩個工作頻率不同的器件進行數據的交互。FIFO 是一種先進先出的數據緩存器,分為同步FIFO 和異步FIFO 兩種,異步FIFO 是跨時鐘域系統設計中比較常見的模塊組成,它的主要作用是使2個工作頻率不同的器件在進行數據交互時實現數據的平穩傳輸[6]。

人眼的極限分辨時間為1/24s,每20幀抽取一幀,抽幀后幀頻為25fps,此時RGB 格式圖像的傳輸速率為117.187 5 MB/s。為滿足實時性需求,SDRAM 緩存時,采用乒乓交替讀入和寫出完成數據的緩存,每個SDRAM 的容量需大于一幀圖像的大小,即4.687 5 MB,存一幀數據需要的時間為0.04s。因此,選用的SDRAM 的容量應大于4.687 5 MB,讀寫速度應大于117.187 5 MB/s。設計中選用的2片SDRAM,型號為IS42S16320B,容量為64 MB,讀寫速度為286 MB/s。

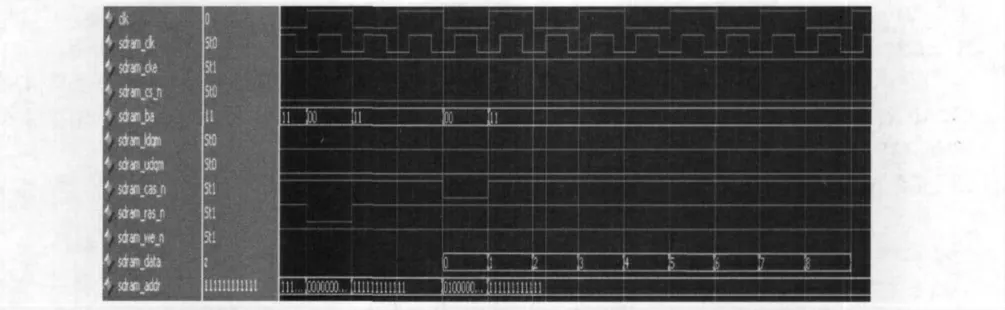

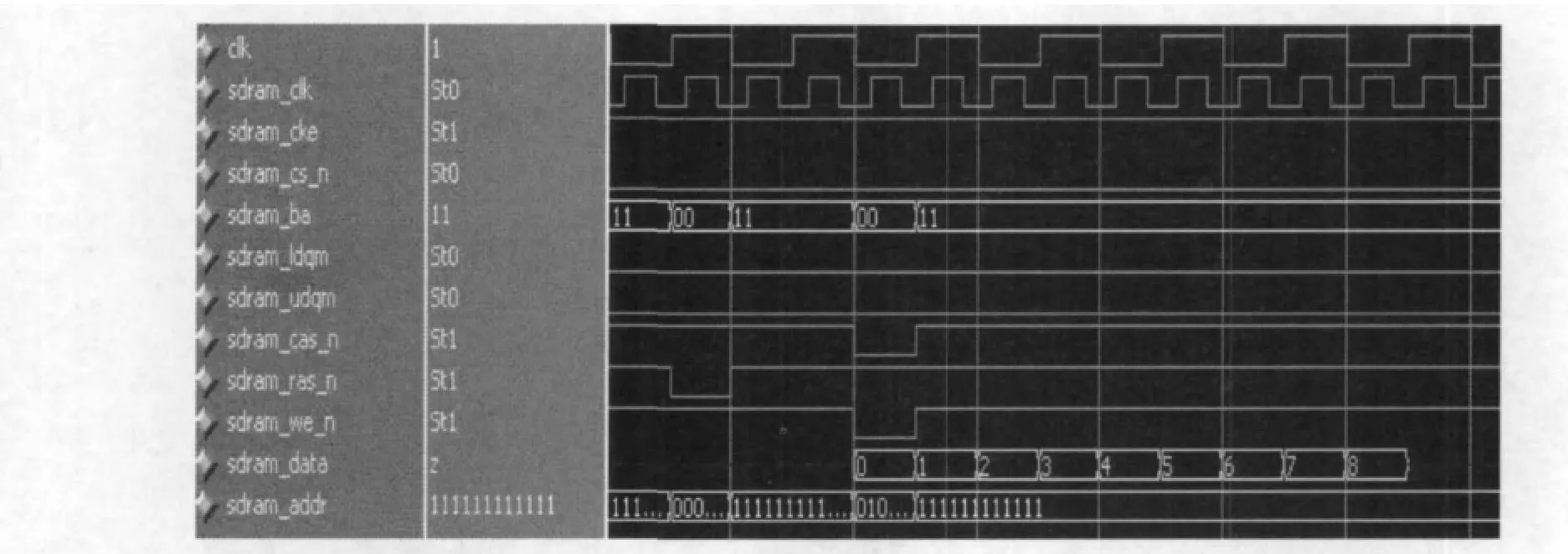

SDRAM 在上電時,首先要進行初始化,包括200μs的輸入穩定期,L-Bank預充電,8次自刷新,模式寄存器設置。初始化完成后進入工作狀態,其工作時序為空閑狀態→行有效狀態→行有效等待狀態→讀/寫數據準備狀態→讀等待潛伏期→讀/寫數據狀態→讀/寫完后預充電等待狀態→空閑狀態[7]。用ModelSim 對其讀/寫時序進行仿真,讀操作與寫操作的仿真圖如圖5和圖6所示。

圖5 SDRAM 讀操作時序圖Fig.5 The timing diagram of SDRAM read

圖6 SDRAM 寫操作時序圖Fig.6 The timing diagram of SDRAM write

4 實時顯示系統設計

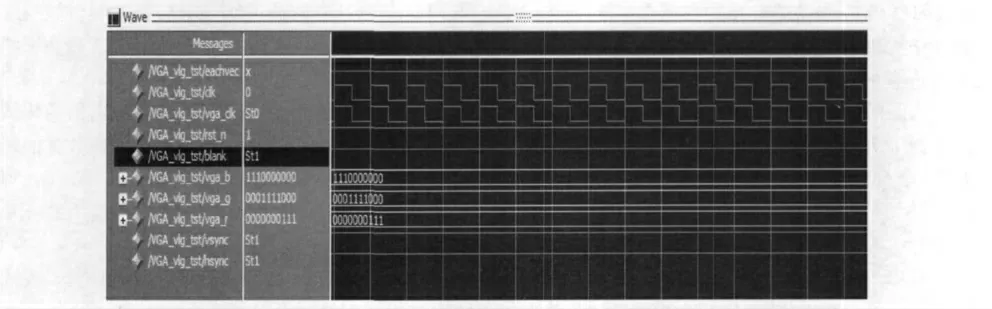

VGA 時序控制模塊的作用是將緩存于SDRAM 中的圖像數據在VGA 顯示器上實時顯示。VGA 工作時采用逐行掃描的方式,掃描從屏幕的左上方開始,從左到右,從上到下,逐行掃描。每掃完一行,用行同步信號進行行同步,電子束對顯示器進行消隱,并使其回到屏幕下一行的起始位置。當掃描完所有行時,用場同步信號進行場同步,使掃描回到屏幕左上方掃描起始位置。同時進行場消隱,并預備下一幀的掃描[8-9],圖7所示為用ModelSim 所做的VGA 顯示時序仿真圖。

圖7 VGA 顯示時序仿真圖Fig.7 The timing simulation of VGA display

在此時序圖中,有VGA 時鐘vga_clk,行有效信號hsync和幀有效信號vsync,在其都為高電平并且在VGA 時鐘的上升沿輸出圖像顏色信息vga_r,vga_g,vga_b。

5 系統測試

為了驗證系統設計的正確性,依據總體設計方案制作了采集、記錄與顯示電路,設計了采集軟件,對運動目標進行實際拍攝。

在滿分辨率條件下對靜態物體(花盆)進行實時圖像采集與顯示,如圖8所示,能夠很清晰地將物體圖像顯示在顯示器上。

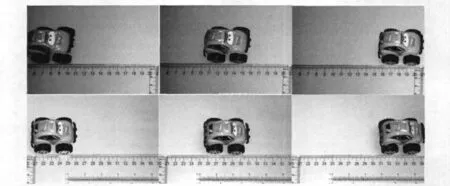

以電動小車為目標,移動速度約為4.5km/h,在一段時間內對小車的移動過程進行拍攝,選取其中連續的6幅圖像進行分析,如圖9所示。通過圖9可以看出,本文所論述的500fps圖像采集及實時顯示系統能夠完成對高速運動的目標進行高速的圖像采集并實時顯示,滿足現場實時性的需求。

圖8 靜態圖像采集Fig.8 Stationary image acquisition

圖9 連續圖像采集Fig.9 Continuous image acquisition

6 結 論

本文對分辨率為1 024×1 280的500fps高幀頻圖像采集及實時顯示的關鍵技術進行了研究,提出了實現該技術的基本方案。在設計過程中對各模塊進行仿真,驗證其可行性,最終設計完成后對整個系統進行性能測試,實現了對視頻圖像的實時采集、緩存與顯示,滿足國防與科研試驗中對高速視頻采集與記錄顯示的需求。

[1] 杜 鵑.基于FPGA 的高幀頻CMOS相機數據傳輸系統設計[D].西安:西安工業大學,2011:2-3.

[2] 楊莉珺,劉鐵根,朱均超,等.基于CMOS圖像傳感器的嵌入式圖像采集與格式轉化[J].電子產品世界,2008(6):96-98.

[3] 侯宏錄,杜 鵑.基于乒乓操作的千兆MAC中的FIFO 設計[J].光學儀器,2011,33(1):36-42.

[4] 楊會偉.高幀頻CMOS相機圖像采集系統研究[D].西安:西安工業大學,2009:10-13.

[5] 郭文豹.高速CMOS智能相機研究[D].長春:長春光學精密機械與物理研究所,2010:13-21.

[6] 張 濤.高幀頻CMOS相機實時壓縮與傳輸關鍵技術究[D].西安:西安工業大學,2012:24-25.

[7] 張文芳.基于FPGA 的SDRAM 控制器設計方案[J].兵工自動化,2012,31(2):57-60.

[8] 孫 艷,孫愛良,王紫婷.基于FPGA 的VGA 顯示控制器的實現[J].自動化與儀器儀表,2008,6(7):106-107.

[9] 董 兵,朱齊丹,文 睿.基于FPGA 的VGA 圖像控制器的設計與實現[J].應用科技,2006,33(10):42-45.