基于NIOSⅡ便攜式信號(hào)發(fā)生器設(shè)計(jì)

王學(xué)力,任全會(huì)

(鄭州鐵路職業(yè)技術(shù)學(xué)院電氣工程系,鄭州450052)

基于NIOSⅡ便攜式信號(hào)發(fā)生器設(shè)計(jì)

王學(xué)力*,任全會(huì)

(鄭州鐵路職業(yè)技術(shù)學(xué)院電氣工程系,鄭州450052)

設(shè)計(jì)了一種基于SOPC技術(shù)便攜式信號(hào)發(fā)生器。該系統(tǒng)利用DDS的理論,以NIOSⅡ嵌入式微處理器為核心的SOPC系統(tǒng)作為信號(hào)發(fā)生器的信號(hào)處理和控制的核心。測試結(jié)果表明此信號(hào)發(fā)生器能輸出標(biāo)準(zhǔn)的正弦波、三角波、方波和鋸齒波,不但波形的頻率和幅度可調(diào),而且根據(jù)實(shí)際需要可現(xiàn)場編程。此系統(tǒng)具有攜帶方便、輸出頻率穩(wěn)定、波形標(biāo)準(zhǔn)、控制靈活和輸出頻率范圍寬的優(yōu)點(diǎn)。

SOPC;信號(hào)發(fā)生器;NIOSⅡ;DDS

信號(hào)發(fā)生器是電路測試和設(shè)備檢測過程中不可缺少的電子儀器,在通信、測量、教學(xué)、科研等領(lǐng)域有著廣泛的應(yīng)用。傳統(tǒng)的信號(hào)發(fā)生器大多都是臺(tái)式機(jī),而且大部分都是采用專用芯片或單片機(jī)作為控制核心,具有攜帶不方便、成本高、控制方式不靈活、不便于升級(jí)的缺點(diǎn)[1]。本系統(tǒng)采用DDS(直接數(shù)字頻率合成)技術(shù)通過SOPC系統(tǒng)在一個(gè)FPGA芯片上實(shí)現(xiàn)了一種頻率可調(diào)的信號(hào)發(fā)生器,能輸出標(biāo)準(zhǔn)的正弦波、三角波、方波和鋸齒波。具有攜帶方便、成本低、性能穩(wěn)定、系統(tǒng)靈活、精度高、便于升級(jí)的優(yōu)點(diǎn)。

1 DDS原理

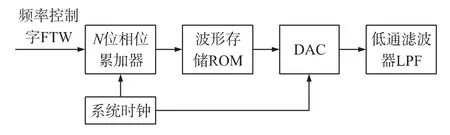

DDS(直接數(shù)字頻率合成)技術(shù)就是利用累加器原理直接合成所需要的波形,DDS模型主要包括相位累加器、波形存儲(chǔ)器、DAC和低通濾波器組成等4部分,DDS電路的數(shù)字部分主要由相位累加器,波形存儲(chǔ)器ROM查表完成[2]。DDS的原理框圖如圖1所示。

圖1 DDS原理框圖

系統(tǒng)時(shí)鐘是一個(gè)穩(wěn)定的晶體振蕩器,用它來同步合成器的各組成部分。相位累加器在每一個(gè)系統(tǒng)時(shí)鐘輸入的時(shí)候,相位增量就累加一次,相位增量由頻率控制字(FTW)決定。如果計(jì)數(shù)大于N,就會(huì)自動(dòng)溢出,此時(shí)把后面的N位數(shù)字保留在累加器中。相位累加器輸出的相位值到正弦幅度值的轉(zhuǎn)換由正弦查詢表實(shí)現(xiàn)。正弦幅度值的數(shù)字量通過DAC轉(zhuǎn)換為模擬量,最后濾波器進(jìn)一步平滑近似正弦波的鋸齒階梯,從而得到一個(gè)很純凈的正弦波信號(hào)[3]。

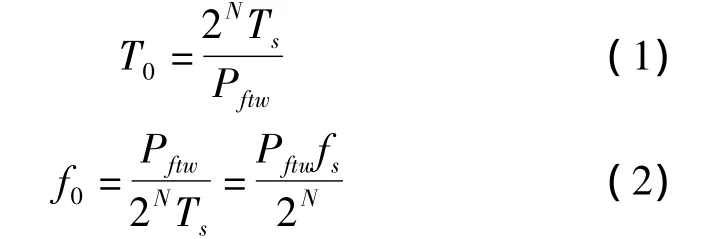

輸出波形的周期T0和頻率f0分別為:

其中Ts是系統(tǒng)時(shí)鐘周期,fs是系統(tǒng)時(shí)鐘頻率,Pftw是頻率控制字的值[4]。

頻率合成器的分辨率通常用頻率增量表示,由式(2)可得到DDS的分辨率:

最低的合成頻率就是這個(gè)增量,奈奎斯持抽樣定理限制了最高的基波合成頻率(至少每周抽樣兩次才能重構(gòu)模型)所以有:

在實(shí)際的應(yīng)用當(dāng)中,最大的輸出頻率是系統(tǒng)時(shí)鐘頻率的40%。信號(hào)發(fā)生器采用DDS技術(shù)很容易實(shí)現(xiàn)[5]。

2 系統(tǒng)硬件設(shè)計(jì)

2.1 系統(tǒng)整體硬件設(shè)計(jì)

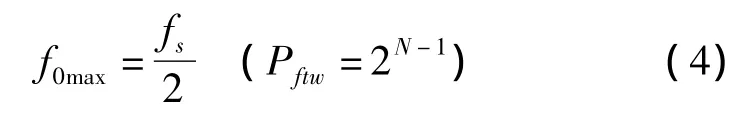

本設(shè)計(jì)是基于NIOSⅡ系統(tǒng)實(shí)現(xiàn)的。整體框圖如圖2所示,包括:時(shí)鐘電路、AD電路、在FPGA上實(shí)現(xiàn)的NIOSⅡ系統(tǒng)、FLASH芯片、SDRAM芯片、EPCS16、鍵盤。FPGA選用Altera公司的cycloneⅣGX型FPGA。系統(tǒng)的控制和數(shù)據(jù)處理由NIOSⅡ系統(tǒng)完成,所得數(shù)據(jù)通過D/A轉(zhuǎn)換和濾波送入示波器或者PC機(jī)進(jìn)行顯示。使用SOPC Builder開發(fā)平臺(tái)完成NIOSⅡ系統(tǒng)的定制[6]。

圖2 系統(tǒng)總體框圖

2.2 DDS模塊設(shè)計(jì)

DDS模塊用軟件實(shí)現(xiàn),以正弦波為例,輸出波形Sout為:

式(5)中時(shí)間t是連續(xù)的,用系統(tǒng)時(shí)鐘對t進(jìn)行抽樣,設(shè)正弦波的相位θ=2πfoutt0,此時(shí)在一個(gè)時(shí)鐘周期內(nèi)θ的變化量是:

把一個(gè)周期切割成2N份,每個(gè)時(shí)鐘周期相位增量的可用量化值BΔθ為:

正弦波的當(dāng)前相位值可以通過相位的量化值進(jìn)行累加運(yùn)算得到。累加的相位增量量化值決定了信號(hào)的輸出頻率。

使用DDS實(shí)現(xiàn)三角波、方波和鋸齒波就更容易了,只需改變相位增量的“0”,“1”值就能得到相應(yīng)的方波、三角波和鋸齒波[7]。

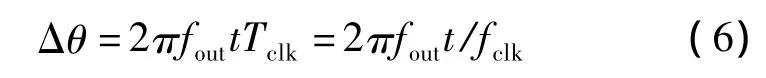

該模塊使用Verilog HDL語言直接編程,能完成頻率控制字的相位累加器和截?cái)噍敵觯@樣就能實(shí)現(xiàn)波形數(shù)據(jù)的輸出和頻率調(diào)制,是系統(tǒng)的核心模塊。其頂層設(shè)計(jì)圖如圖3所示。

圖3 DDS模塊頂層設(shè)計(jì)圖

系統(tǒng)時(shí)鐘取樣的32 bit相位寄存器和32 bit二進(jìn)制加法器組成了子模塊“xwljq”是32 bit相位累加器。改變時(shí)鐘脈沖可以改變頻率控制字,也就是能輸出頻率。子模塊“l(fā)om_room0”通過QuartusⅡ定制而成的正弦查詢表,通過Matlab軟件生成正弦數(shù)據(jù),這些數(shù)據(jù)以mif的格式存儲(chǔ),并將這些數(shù)據(jù)加載到lom_room0模塊中。輸入為10 bit地址,通過系統(tǒng)時(shí)鐘可以輸出存儲(chǔ)的正弦數(shù)據(jù)。“outs”子模塊是波形輸出模塊,sel是波形選擇端,選擇端分別是0、1、2、3的時(shí)候,通過時(shí)鐘就能分別輸出正弦波、三角波、方波和鋸齒波。本設(shè)計(jì)使用D/A轉(zhuǎn)換是8 bit,輸出端qout只需要接前8 bit即可。

2.3 濾波電路設(shè)計(jì)

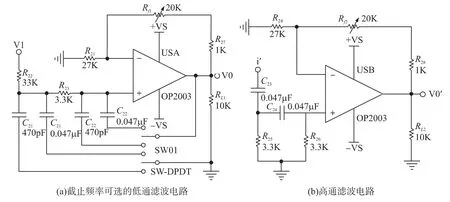

本設(shè)計(jì)中最大頻率為100 kHz,濾波器類型的選擇由輸出頻率決定。圖4(a)是低通濾波電路,F(xiàn)PGA通過控制繼電器SW01來選擇不同的截止頻率。低通濾波電路在輸出頻率低于1 kHz時(shí)使用,假設(shè)C21=C22,可以得出C21=C22=1/(2πR22fs)≈0.048μF,取C21=C22標(biāo)稱值為0.047μF,可以計(jì)算出截止頻率把低通濾波電路和高通濾波電路級(jí)聯(lián)[8],選擇電容為:C21=C22=470 pF,C23=C24=0.047μF。

圖4 濾波電路

3 誤差分析

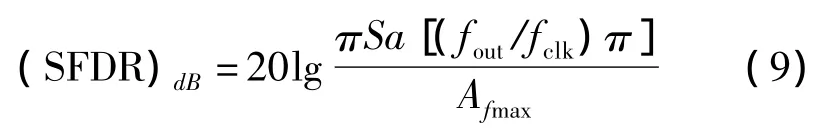

系統(tǒng)頻率分辨率達(dá)到0.015 Hz,硬件設(shè)計(jì)采用了50 MHz晶振。為了得到較高的頻率分辨率,在DDS設(shè)計(jì)中 N的取值需要比較大(本系系統(tǒng)取32)。只用高A位尋址能大大節(jié)省FPGA內(nèi)部資,此時(shí)因?yàn)樯崛サ臀籅位就會(huì)產(chǎn)生相位截?cái)嗾`差。DDS的雜亂動(dòng)態(tài)范圍可以表示為:

其中

式(11)中Sa(x)表示為Sa(x)=sin(x)/x,變量x最接近x的取整運(yùn)算用int(x)表示,變量x,y的最小值用min(x,y)表示。<x>y=x-int(x/y)×y,B=N-A。由式(9)可以算出(SFDR)dB≥6.02(N-B)。N和B分別取值為32和22,就能算出無雜亂動(dòng)態(tài)范圍大于60.2 dB。DAC908、OPA2300和OPA51技術(shù)指標(biāo)的誤差分別為0.05%、0.1%和0.1%,所以系統(tǒng)的最大幅度誤差可以計(jì)算出來:(0.052+0.12+0.12)1/2=0.15(%)。D/A轉(zhuǎn)換芯片和運(yùn)放性能的好壞決定系統(tǒng)的誤差的大小[9]。

4 測試結(jié)果和結(jié)論

4.1 測試結(jié)果

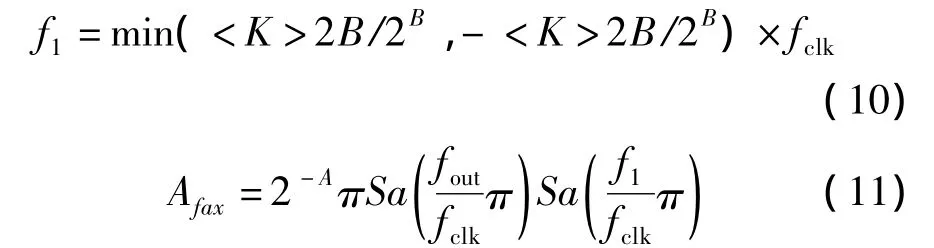

使用示波器測試結(jié)果如下圖5所示。

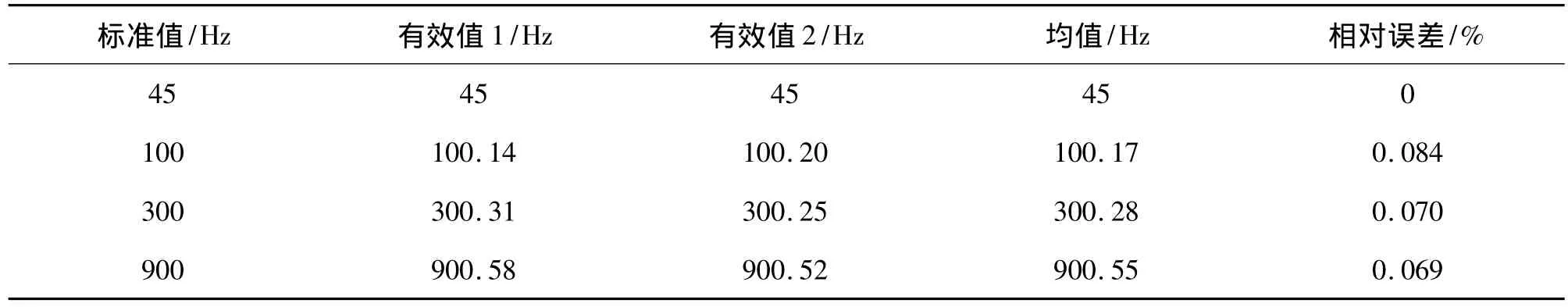

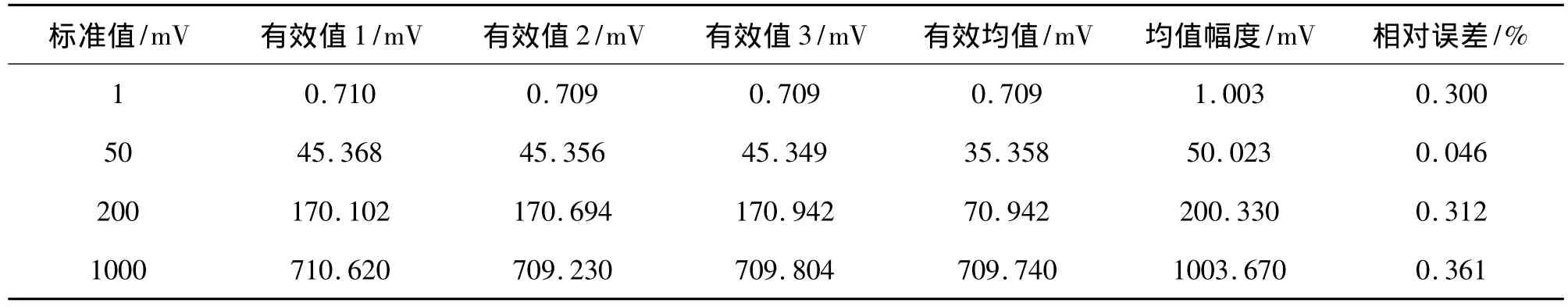

使用測量范圍為0.1 Hz~100 MHz,分辨率為0.001 Hz高精度頻率計(jì)對波形頻率進(jìn)行檢測,以正弦波為例測量結(jié)果如表1所示。使用萬能表來對其幅值進(jìn)行性能測試,測試結(jié)果如表2所示。測試結(jié)果表明,信號(hào)發(fā)生器波形質(zhì)量和幅值等各項(xiàng)指標(biāo)都在理論誤差范圍之內(nèi)。

圖5 示波器測試結(jié)果

表1 頻率性能測試

表2 幅值性能測試

4.2 結(jié)論

本系統(tǒng)通過使用基于NIOSⅡ的嵌入式處理SOPC技術(shù)不但減小了系統(tǒng)的PCB面積(降低系統(tǒng)的功耗,使系統(tǒng)體積大大減小,攜帶方便),外圍硬件電路的復(fù)雜性也大大降低,這樣電路結(jié)構(gòu)更加簡潔,而且系統(tǒng)波形顯示清晰、工作穩(wěn)定。該系統(tǒng)可由于FPGA具有可編程特性,改變控制方式或更換波形數(shù)據(jù)都非常方便,易于系統(tǒng)升級(jí),有很高的性價(jià)比和市場應(yīng)用空間。

[1]陳亞軍,陳隆道.基于Verilog HDL的信號(hào)發(fā)生器的設(shè)計(jì)[J].電子器件,2011,34(5):525-528.

[2]鄧騰,吳校生,周曉玲,等.基于DSP和DDS技術(shù)相位及頻率嚴(yán)格可調(diào)的多路同步信號(hào)發(fā)生器[J].電子器件,2012,35(2): 163-167.

[3]常高嘉,馮全源.基于FPGA的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[J].電子器件,2012.22(6):217-220.

[4]郭偉然,劉耀,湯勇明.基FPGA的頻率特性測試儀的設(shè)計(jì)[J].南京:電子器件,2011,34(6):713-717.

[5]楊春玲,彭立章.基NIOS邊界掃描測試平臺(tái)的開發(fā)[J].電子器件,2007,30(6):2129-2132.

[6]馮偉昌,林玉池,何冬.基于FPGA的雙通道實(shí)時(shí)圖像處理系統(tǒng)[J].傳感技術(shù)學(xué)報(bào),2010,23(8):1118-1122.

[7]王丹,李平,文玉梅,等.采用DDS頻率合成的虛擬信號(hào)發(fā)生器研究[J].傳感技術(shù)學(xué)報(bào),2007,20(3):586-591.

[8]杜斌峰,王智敏,孫躍.基于FPGA的數(shù)字混沌序列的實(shí)現(xiàn)及性能分析[J].電子器件,2011,34(4):477-485.

[9]王力,張雄.小波濾波與AR模型在腦電信號(hào)處理的應(yīng)用[J].電子器件,2012,35(4):461-464.

Design of Portable Signal Generator Based on NIOSⅡ

WANG Xueli*,REN Quanhui

(Department of Electrical Engineering,Zhengzhou Railway Vocational and Technical College,Zhengzhou450052,China)

A portable signal generator is designed on the basis of SOPC technology.The system uses the theory of the DDS,taking the SOPC technology based on embedded processor of NIOSⅡas the core of signal generator for signal processing and control.The test results show that this signal generator can output sine waveforms,triangle waveforms,square waveforms and sawtooth waveforms.Itswave form frequency and amplitude are adjustable,and the system can be field programmable according to the actual needs.The system has advantages such as easy to carry,stable output frequency,standard waveforms,easy control and wide bandwidth.

SOPC;signal generator;NIOSⅡ;DDS

10.3969/j.issn.1005-9490.2013.04.011

TH741 文獻(xiàn)標(biāo)識(shí)碼:A 文章編號(hào):1005-9490(2013)04-0478-04

2012-12-25修改日期:2013-01-29

EEACC:1230

王學(xué)力(1963-),男,漢,河南信陽人,鄭州鐵路職業(yè)技術(shù)學(xué)院,講師,碩士,研究方向?yàn)锳RM、通信技術(shù)及電子技術(shù)研究,wangxueli1963@163.com。