一種用于時鐘數據恢復的寬帶鎖相環設計

(1.華虹NEC電子有限公司,上海201206;2.東南大學軟件學院,南京210096)

(1.華虹NEC電子有限公司,上海201206;2.東南大學軟件學院,南京210096)

鎖相環廣泛應用于電信、光收發器、數據存儲局域網以及無線產品中,提出了一種新穎的應用于時鐘數據恢復的鎖相環設計,包括鑒頻鑒相器、電荷泵、環路濾波器、換擋電路、壓控振蕩器以及環路狀態檢測電路的設計,采取的方案是對環路濾波器的模擬電壓進行實時監控動態調整鎖相環系統的環路參數,該結構能夠很好的應用于輸入數據流變化范圍極寬(20 Mbit/s~2.5 Gbit/s)的時鐘數據恢復系統。設計采用了一種單供電電壓的0.18μm CMOS工藝,并給出Cadence環境下仿真結果。

鎖相環;時鐘數據恢復;寬帶;多相位

隨著集成電路的發展,時鐘與數據恢復電路(CDR)的應用越加廣泛,無論是在長距離光纖通信還是在短距離并行I/O接口通信中CDR電路都是一個關鍵的電路模塊[1],而基于鎖相環的CDR設計又是很熱門的方案,作為其核心部分的鎖相環直接決定了CDR系統的性能。

電源和襯底噪聲對鎖相環有較大影響,由傳遞函數可看出環路對噪聲來說是個低通濾波器,因此可知環路帶寬越窄,抖動越小[2]。考慮到面積方面,由于單片集成的要求使得環路濾波器的電容無法做到很大。穩定性方面的要求則限制著帶寬的拓展。環路濾波器的截止帶寬與電荷泵充放電電流的大小及壓控振蕩器的增益對PLL帶寬有著直接的影響。本設計采取的方案是對環路濾波器的模擬電壓進行實時監控,以動態改變鎖相環的電荷泵電流、環路濾波器的電阻值和壓控振蕩器的增益來調整鎖相環系統的環路參數,從而使鎖相環能夠較穩定地跟蹤速率變化極寬的數據流[3-8]。

目前有很多基于鎖相環的CDR電路設計與討論,但很少有專門應用于輸入數據流變化極寬的CDR系統的鎖相環設計。本設計的目的在于提供可以工作于輸入數據流變化范圍10 Mbit/s~2.5 Gbit/s的時鐘數據恢復核心部分的鎖相環前端電路設計。

1 電路模塊設計

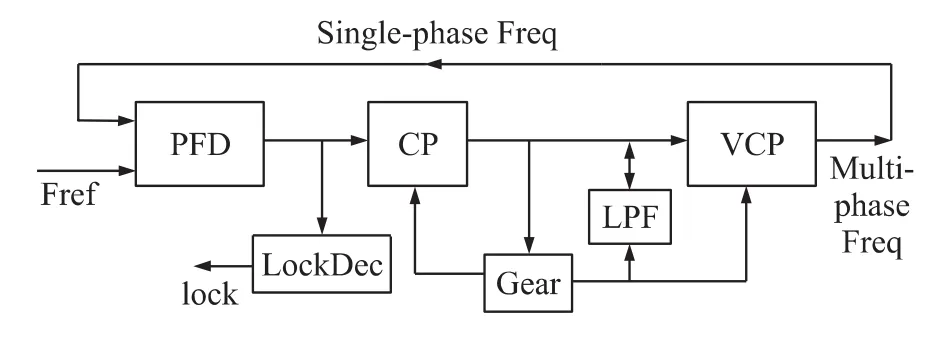

圖1為應用于CDR系統的核心部分鎖相環信號鏈路框圖。其中包括鑒頻鑒相器(PFD)模塊、電荷泵(CP)模塊、環路濾波器(LPF)模塊、壓控振蕩器(VCO)模塊、換擋電路(Gear)模塊、鎖定指示器(LockDec)模塊。

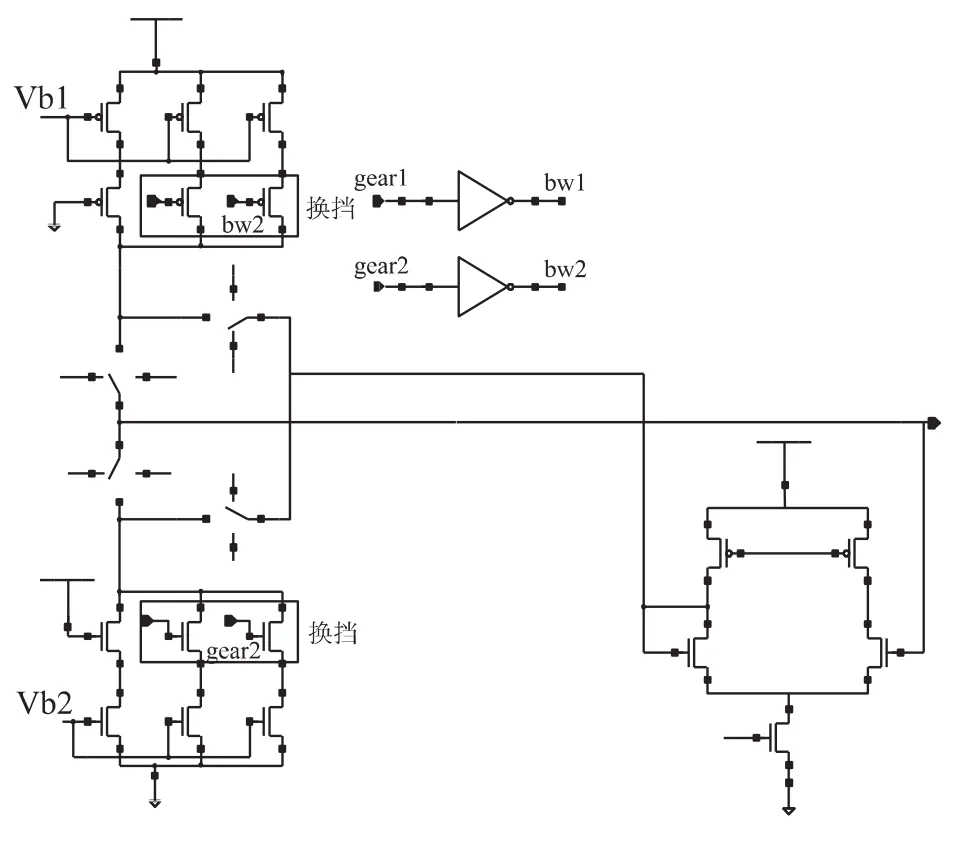

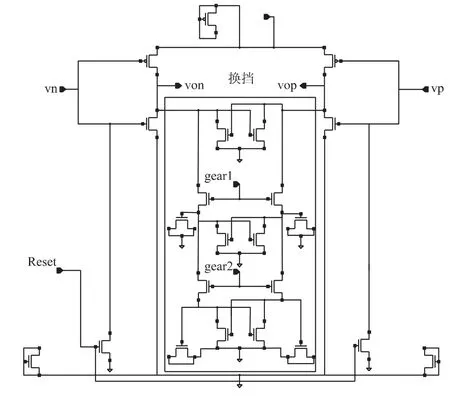

與經典鎖相環結構相比此設計中的亮點就是增加了換擋電路模塊與狀態檢測電路模塊,結合環路特點可以將變化范圍較大的輸入參考頻率Fref分為高、中、低三個區間,從而在每個區間優化環路參數,使鎖相環性能達到最佳狀態,換擋電路如圖2所示,具體過程是由換擋電路模塊監測LPF的模擬電壓大小來調換檔位gear1、gear2,也即同步調整CP充放電流、LPF電阻值、VCO振蕩頻率。鎖定指示器模塊主要是對up(上)、dn(下)信號的處理從而來判斷環路是否鎖住[9]。

圖1 多相位鎖相環電路框圖

圖2 換擋電路原理圖

下面分模塊介紹具體電路設計:

1.1 鑒頻鑒相器(PFD)模塊

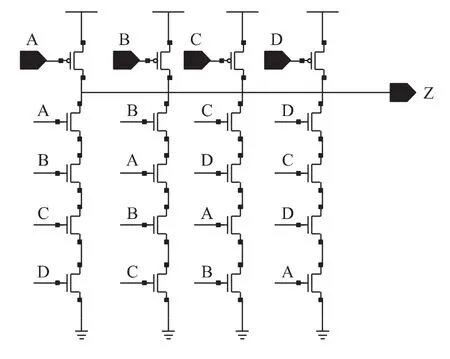

傳統的鑒頻鑒相器存在“死區”與信號延遲時間不同等問題,都會造成VCO的不必要的抖動。因此我們對傳統PFD做了如下改進:第1,在傳統鑒頻鑒相器中的四輸人與非門后增加延遲電路,推遲復位信號,從而使輸出的up、dn信號的脈沖寬度變寬解決“死區”問題[10],電路如圖3所示。第2,四輸入與非門采用如圖4所示電路設計,此設計使得任意輸入為低時都可以很快傳遞到輸出端,解決信號延遲不同問題。

圖3 改進型PFD原理圖

1.2 電荷泵(CP)模塊

傳統電荷泵中主要存在的不理想特性主要包括: (1)電流失配;(2)電荷注入;(3)時鐘饋通;(4)電荷分享。電流失配一般主要是由電荷泵中的電流鏡不匹配引起,在設計時可以通過加強對版圖規劃與增加管子的寬度來削弱其影響。電荷注入、時鐘饋通引入的誤差一般可以通過將控制信號的輸入管盡量遠離電容來減小。同時為了調節環路的穩定性,本設計創新的引入了gear1、gear2兩個輔助“換擋”控制信號,貫穿于電荷泵、環路濾波器、壓控振蕩器的調節。gear1、gear2提供了3個可選檔位,如表1所示。圖5為本設計所采用的可控電流型電荷泵原理圖,通過自舉的方式有效消除了電荷共享的影響。

圖4 四輸入與非門原理圖

表1 檔位表

圖5 CP原理圖

1.3 環路濾波器(LPF)模塊

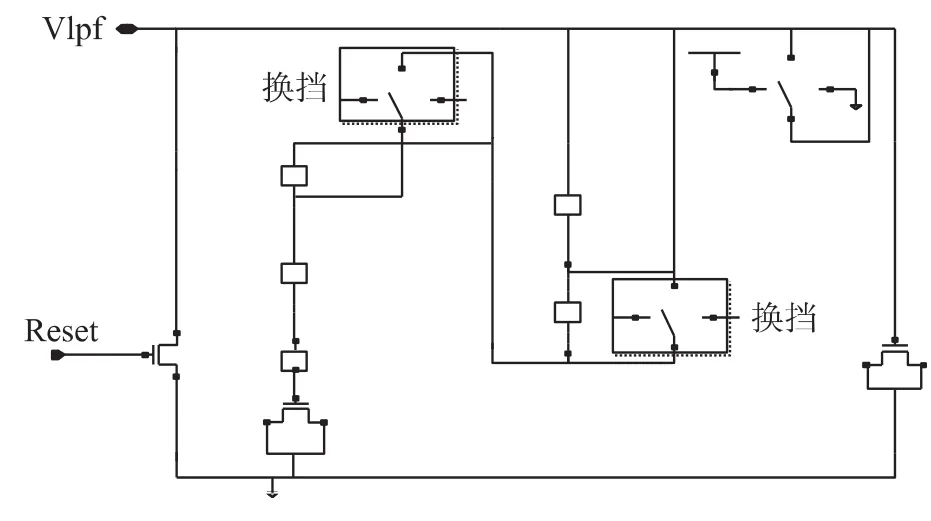

傳統一階環路濾波器存在穩定性問題,會對控制電壓產生影響從而產生嚴重的相位噪聲和雜散分量,為了使電壓穩定,可以在一階無源環路濾波器的基礎上并連一個小電容,雖然使得鎖相環變成三階而產生穩定性困難,但是只要并聯電容為原來電容的1/5到1/10,閉環的時間和響應就相對保持不變。同樣的為配合環路參數的優化,環路濾波器采用分檔制,如圖6所示,控制信號gear1、gear2控制著濾波器中電阻的大小,由此來調節LPF的帶寬,優化環路。

圖6 LPF原理圖

1.4 壓控振蕩器(VCO)模塊

壓控振蕩器則是鎖相環中最核心的部件,一方面它的工作頻率范圍決定了電荷泵鎖相環的捕獲范圍,另一方面它的噪聲抑制能力決定了鎖相環的噪聲性能。因此,它的性能好壞直接關系到整個鎖相環的性能的優劣[11-12]。本設計由于采用十級Buffer的延遲,振蕩器在較低頻率上工作,而引入的兩個控制信號gear1、gear2可以有效的調節VCO的振蕩頻率,使得頻率在感興趣的范圍內具有良好的線性度。由噪聲傳遞函數可以看出輸出頻率中的噪聲正比于VCO的增益,所以要使噪聲效應減到最小,其增益必須最小,這與調節的范圍是直接矛盾的,所以本設計根據調節gear1、gear2控制信號較好的減小了這種矛盾。如圖6所示,在輸出端增加了飽和增益級電路從而保證了全擺幅的輸出信號,圖8為延時級單元電路,電路中gear1、gear2控制信號的產生由監測LPF濾波后的電壓來調整。

圖7 VCO原理圖

圖8 延時級原理圖

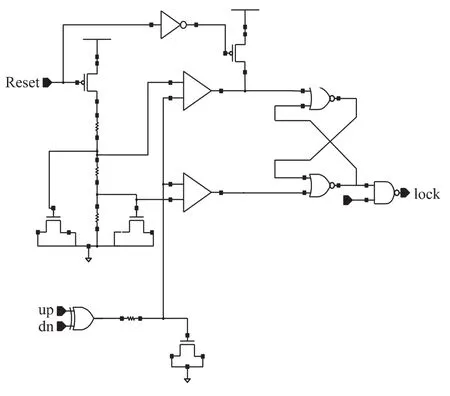

本設計還增加了一個特色功能:鎖定指示器。如圖9所示,當環路進入鎖定狀態后,輸出端Lock信號將輸出高電平做出指示,由此可以很直觀的判斷電路的工作狀態。

圖9 鎖定指示器

2 仿真結果及分析

設計采用一種3.3 V的單供電電壓0.18μm CMOS工藝進行仿真,輸入參考頻率分別采用2 MHz、50 MHz、250 MHz連續變化的方波,Cadence環境下鎖相環仿真結果如圖10所示,結果表明此鎖相環可以工作于頻率變化為2 MHz~250 MHz的情形下,換擋信號gear1、gear2有效地控制了環路參數的變化,由仿真結果圖可以明顯看出在換擋信號切換的時候環路濾波器的電壓有著明顯的變化趨勢。

在不同狀態轉換所需時間上電路有著良好的相應性能,如圖11所示,電路由初始態到穩定到低頻段2 MHz用時53μs,在低頻段轉換到中頻段即2 MHz~50 MHz切換用時為22μs,在中頻段向高頻段切換時即50 MHz~250 MHz也僅僅用了32μs,可以看出電路的響應性能是相當良好的。

圖10 仿真結果

圖11 穩定時間

在電路穩定工作后其噪聲所產生的抖動也是比較小的,如圖12所示,在低頻段2MHz時抖動幅值為0.26 mV,在中頻段50 MHz時抖動幅值為0.29 mV,在高頻段250 MHz時抖動幅值也僅為0.68 mV,所以電路在抑制噪聲抖動方面也有著不錯的表現。

圖12 抖動幅值

3 結論

本文設計了一種應用于CDR系統的多相位鎖相環電路,該電路采用3.3 V單供電電壓0.18μm CMOS工藝設計,仿真結果表明該電路可以很好的工作于數據流變化極廣的應用中,由于此設計是十相位輸出,因此CDR可處理數據流變化范圍為10 *Freq(20 Mbit/s~2.5 Gbit/s),與一般鎖相環相比有著覆蓋速率范圍廣、高穩定性、響應速度快等優點,該電路采用了新穎的設計思路,通過對濾波器模擬電壓的監控從而動態改變環路參數使得鎖相環性能達到最佳狀態,相信該設計經過工藝的進一步優化和版圖設計,其IP核將完美的服務于寬速率CDR系統。

[1]張長春,王志功,吳軍,等.5 Gb/s 0.18μm CMOS半速率時鐘與數據恢復電路設計[J].微電子學,2012,42(3):17-21.

[2]Behzad Razavi.模擬CMOS集成電路設計[M].陳貴燦,程軍,張瑞智,等譯.西安:西安交通大學出版社,2003.

[3]Savoj J,Razavi B.A 10-Gb/s CMOSClock and Data Recovery Circuitwith a Half-Rate Linear Phase Detector[J].IEEE Journal of Solid-State Circuits,2001,36(5):761-767.

[4]Jin Kyu Kwon,Tae Kwan Heo,Sang-Bock Cho,et al.A 5-Gbp/s 1/8-Rate Cmos Clock and Data Recovery Circuit[C]//Iscas 2004:IV-294-296.

[5]Seedher A,Sobelman G E.Fractional Rate Phase Detectors for Clock and Data Recovery[C]//IEEE 2003:313-316.

[6]Beshara M.Design Considerations for High Speed Clock and Data Recovery Circuits[C]//A Thesis for the Degree of Master of Applied Science,Ottawa-Carleton Institute for Electrical Engineering,Carleton University 2002:23-24

[7]李義慧,馮軍,王遠卓,等.10 Gb/s時鐘恢復與數據判決單片集成電路的設計[C]//全國第十三次光纖通信即第十四屆集成光學學術論文集.2012:6.

[8]白冰,郭玉彬,趙曉暉.多速率接收及時鐘數據恢復光纖激光傳輸實驗研究[J].半導體光電,2012,33(2):47-52.

[9]張長春,王志功.高速時鐘與數據恢復電路技術研究[J].電路與系統學報,2012,17(3):67-71.

[10]陳一輝.高速低噪聲鎖相時鐘發生器的設計[D].上海:復旦大學,2008.

[11]王勇.高速時鐘恢復系統的研究[D].上海:復旦大學,2009.

[12]葉君青.用于1.25 Gb/s千兆以太網的時鐘數據恢復電路的設計[D].上海交通大學,2008.

一種用于時鐘數據恢復的寬帶鎖相環設計*

王 旭1,2,朱紅衛1

A W ide-Band PLL Circuit Design Applied in CDR*

WANG Xu1,2,ZHU Hongwei1

(1.Huahong NEC Electronics Co.Ltd.,Shanghai201206,China;2.Software College,Southeast University,Nanjing210096,China)

PLL has been widely used in the area of communications.A new type of PLL applied in CDR was proposed which including six parts(phase frequency detector,charge pump,loop filter,voltage controlled oscillator,gear generation,lock detector),and adopting theway ofmonitoring the voltage of LPF to dynamically adjust system parameters.It can meetwell the demand that the input data vary from 10 Mbit/s to 2.5 Gbit/s in CDR.Detail simulation was given at the Cadence design environmentwith a 3.3 V single voltage 0.18μm CMOS process.

PLL;CDR;wide band;multi-phase

10.3969/j.issn.1005-9490.2013.06.017

TN761 文獻標識碼:A 文章編號:1005-9490(2013)06-0828-05

項目來源:國家集成電路項目(2009ZX02303)

2013-03-20修改日期:2013-04-09

EEACC:1250;1265E

王 旭(1987-),男,江蘇省沛縣,漢族,現于東南大學攻讀碩士學位,主要研究方向為模擬集成電路設計。目前任于上海華虹NEC電子有限公司設計開發部實習工程師。參與國家集成電路項目《0.18微米/0.13微米鍺硅BiCMOS成套工藝技術》,wangxu@hhnec.com,wangxu1988wo@163.com;

朱紅衛(1968-),男,1997年畢業于上海交通大學微電子所,獲博士學位,現任上海華虹NEC設計主管,同時被聘為上海交通大學微納技術學院兼職教授,長期從事模擬和射頻電路設計,在國內外發表論文三十余篇,獲專利授權10項,申請20多項。