高分辨率測距雷達系統寬帶調制解調器*

張仁民 ,錢瑩晶,伍 清

(懷化學院物理與信息工程系,湖南 懷化418008)

測距分辨率是衡量隨機碼脈沖編碼連續波相位調制雷達的主要參數指標之一,也是高分辨率成像雷達發展的核心問題[1]。根據雷達測距原理,要提高分辨率必須提高隨機碼的碼速率——如想獲得5 m 的分辨率必須將碼速率設定在30 MHz,目前國內大多數該體制的雷達只能達到這一指標,而如想獲得1 m 的分辨率必須將碼速率提至150 MHz。

但150 MHz 速率的隨機碼脈沖編碼雷達在設計和實現上具有一定的技術難度:其一,這個速率的碼產生和傳輸均屬于高速數字電路設計的范疇,會存在信號完整性問題SI;其二,為保證信號處理子系統在進行脈沖壓縮時有足夠的信噪比需要保證脈沖信號具有陡峭的動態時間和調制解調器的帶寬。本文主要討論第2 個問題,即高速隨機碼的傳輸和射頻寬帶調制解調器設計。

1 系統組成

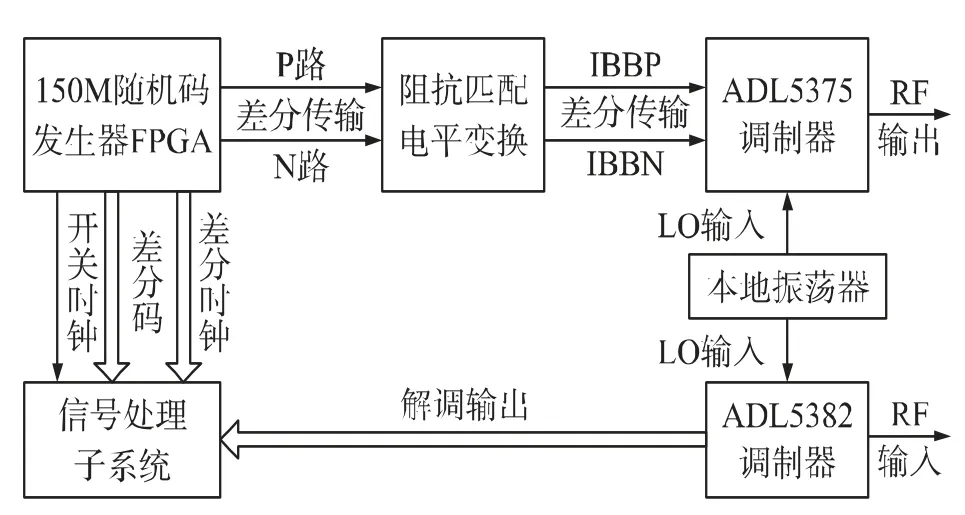

如圖1 所示,本系統主要由基帶信號發生器(碼發生器)、射頻調制和射頻解調器組成。

圖1 系統組成框圖

(1)基帶信號發生器:該部分用于根據隨機碼產生算法產生兩路同源的150 MHz 的隨機碼序列、150 MHz 時鐘和相關的開關時鐘;需要說明的是為保證信號處理子系統進行脈壓后有較好的信噪比,產生的隨機碼需要具有陡峭的邊沿動態特性[1]。該部分電路的設計完全屬于高速電路設計,需要考慮信號的完整性問題。

(2)射頻調制模塊:用于將150 MHz 的寬帶隨機碼字調制到2.4 GHz/900 MHz 的正弦載波上,以適應無線信道的傳輸,同時可以將天線的尺寸控制在一定范圍內;該部分應該還包括一些信號的變換和匹配電路。

(3)射頻解調模塊:將調制時的同頻同相本振載波LO 與接收的射頻RF 信號相乘進行相干解調解調出150 M 的數字隨機碼,并進行適當的整形和放大處理以適應后續電路(采樣和信號處理電路)的處理要求,進而得到雷達所需要的距離(基于相關原理)和速度信息(基于多普勒頻移)[2-3]。

2 寬帶調制解調器設計

為了適合無線信道傳輸和減少天線尺寸,需要將隨機碼調制到射頻載波上,接收時再進行相應的解調。同時考慮到后續信號處理子系統在脈沖壓縮時能有足夠的信噪比,此處的調制解調器必須考慮150M 帶寬的高速基帶信號所必須具有的調制解調帶寬,此處的載波選擇為2.4 G/900 M。選用的調制解調芯片分別是ADI 公司的ADL5375 和ADL5382[4]。

2.1 寬帶調制器設計

(1)寬帶BPSK 調制原理及頻譜

①BPSK 調制原理

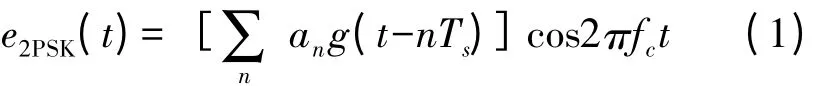

BPSK 的時域表達式通常可以表為:

該式中的an為隨機碼,g(t)為單個隨機碼對應的基帶脈沖波形,cos2πfct 為正弦載波。在本文中更具體的參數含義如下:an=+1 概率為P;an=-1 概率為1-P。即信碼取雙極性信號,g(t)取矩形脈沖。

②BPSK 頻譜

通過式(1)不難看出,BPSK 調制和2ASK 調制非常類似,可以認為兩路2ASK 的合成,所以其頻譜分析方法及結論和2ASK 非常雷同。只是兩路不同在于an的取值,故可用求2ASK 功率譜密度方法求出[5]。

由該式看出,BPSK 的頻譜事實上是將脈沖的頻譜搬移至載頻處。由于脈沖g(t)頻譜為其有效帶寬約為1/Ts。因此必須考慮帶寬150 MHz隨機碼基帶信號下載頻的選擇和調制解調芯片的帶寬,否則勢必會影響調制解調的結果。此處隨機碼的有效帶寬為150 MHz,載頻選擇2.4 G(fc/(1/Ts)=2.4 G/150 M=16)。

(2)LVDS 標準與調制芯片接口

為適應高分辨率測距的需要,150 MHz 的隨機碼序列由FPGA 芯片產生并采用差分低電壓標準輸出(也只有采用該標準才能保證低功耗和信號傳輸的完整性)。差分低壓LVDS 標準具有一定的電特性:1.25 V 左右的直流偏置和約700 mV 的差分擺幅(每個管腳上350 mV)[6-7],而正交調制器ADL5375 要想獲得優越的調制性能,要求在輸入的基帶信號上外加500 mV 的直流偏置(ADL5375-05)[8]。因此,需要將碼發生器送過來的差分信號經過電平變換電路將之變為適合調制器工作的電平形式。這就需要設計LVDS 與射頻RF 調制器之間的接口。

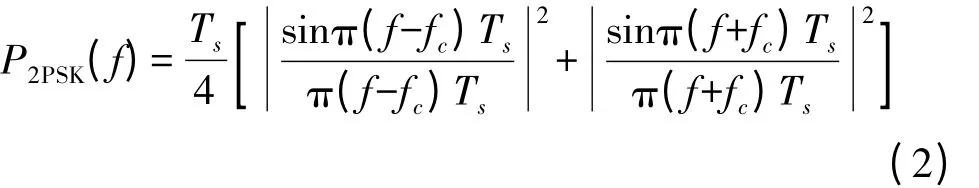

這樣的轉換電路有2 種設計思路,一是利用有源電路實現,這樣可以在不犧牲交流增益的前提下實現直流偏置的變化,但電路較為復雜;二是利用無源的電阻網絡實現直流偏置的移動。考慮到后級有放大電路,在此采用方案2。具體電路如圖2 中上下兩路對稱部分電路所示。

圖2 調制器電路圖

該電路上下兩路完全對稱部分分別形成兩路基帶信號的直流偏置。在這里取其中上邊一路分析:由于基帶信號發生板送來的LVDS 信號具有1.25 V的直流偏置,而送去ADL5375 的信號應為500 mV直流偏置,因此信號的偏置由LVDS2.5 的獨立電源提供,采用R2、R4和R6組成無源分壓網絡,R4和R6連接點處的信號即具有ADL5375 所需要的500 mV直流偏置。但需要說明的是該電路會犧牲一定的交流增益。

(3)調制電路

如圖2 所示的調制器電路原理圖中ADL5375相關連接是調制器設計的核心部分:該芯片的連接主要包括電源、基帶輸入、本地載波、射頻輸出、使能等引腳的連接[7]。

電源和地:VPS1 和VPS2 連接5 V 電源,COM腳(10 個)通過低阻路徑連接到相同的地層。每個電源引腳都應就近連上100 pF 和0.1 μF 電容退耦到地。在芯片封裝下露出的焊盤應該通過低阻連接到地層。

基帶輸入:基帶輸入應該用差分形式驅動,ADL5375 的標準的驅動電壓是差分700 mV p-p(350 mV p-p 每個引腳)。而且ADL5375-05 所有基帶輸入都必須有500 mV 直流偏置。

LO 輸入:本振輸入設計成為單端源驅動。本地振蕩器信號通過串聯電容以交流耦合的形式加到LO 引腳同相端(LOIP),此時反相端(LOIN)通過電容交流耦合到地。ADL5375 本振信號的典型驅動電壓為0 dBm。

RF 輸出端:射頻輸出在RFOUT 引腳(Pin16)上,可以驅動50 Ω 負載。在大多數情況下,RFOUT腳必須交流耦合到負載。

輸出使能端:ADL5375 具有輸出無效引腳功能,它通過關斷輸出放大器以隔離調制器和負載。當DSOP 引腳電壓超過2 V 時輸出無效。當該腳接地或者懸空時,輸出有效。利用DSOP 可以減少LO 射頻泄露和降低芯片的寬帶噪聲到KT 噪聲值。也可以將ADL5375 的供電電流從200 mA 減少到131 mA。從DSOP 引腳由高變低(輸出由無效到有效)到輸出重建需要大約200 ns,從DSOP 引腳由低到高(輸出由有效到無效)到輸出關斷需要在100 ns 左右。

2.2 寬帶解調器設計

(1)解調器硬件設計

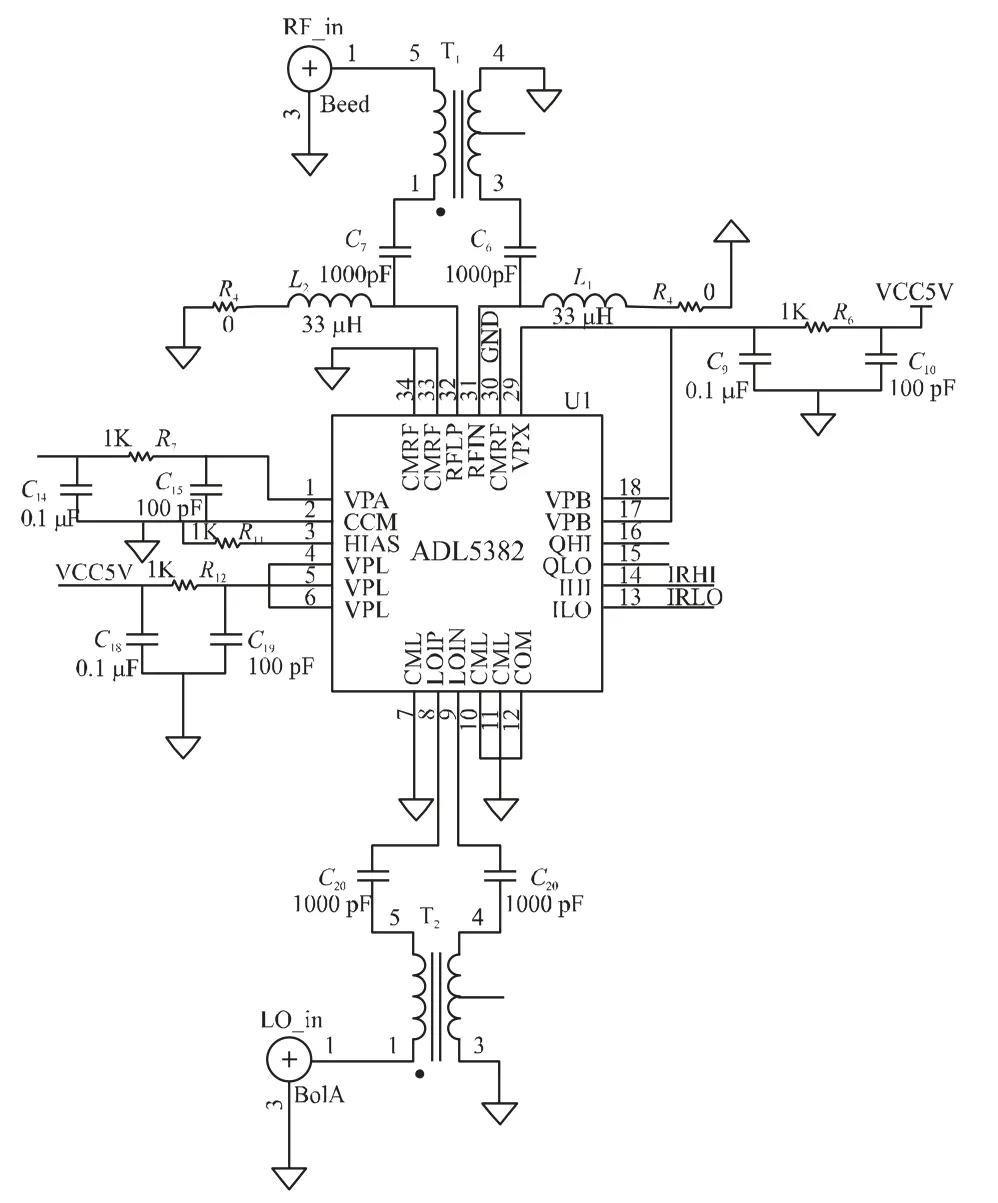

圖3 為ADL5382 解調器原理圖。在該圖中,LO 本振單端輸入的信號通過非平衡變壓器轉換成平衡的差分輸入之后,經過電容交流耦合到解調芯片的LOIP 和LOIN 兩個差分本振輸入端。射頻RF 的輸入模式和LO 的輸入非常類似,至少在進入解調芯片射頻輸入端RFIP 和RFIN 差分輸入端之前通過33 nF 的扼流電感下地。其余輸入端多為電源供電,在每個電源管腳附近都并聯了大小不一的兩個退藕電容[9]。

圖3 解調器原理圖

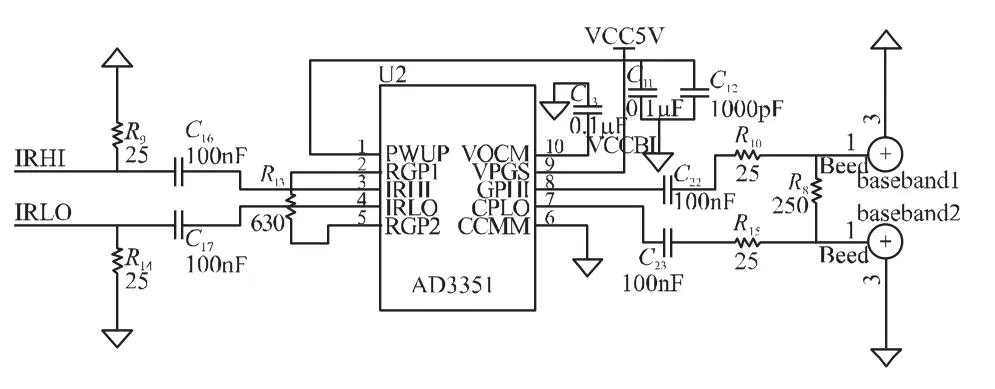

(2)視頻放大器及與信號處理系統ADC 的接口設計

ADL5382 解調器的輸出不滿足LVDS 的電特性標準,需要進行幅度調整和直流偏置變換,同時也為了方便和后級ADC 接口,所以需要加入放大器。由于解調輸出是150M 的高速基帶解調信號,故需要采用高性能的寬帶放大器AD8351。圖4 給出了視頻放大器的原理圖[10]。

圖4 視頻放大器原理圖

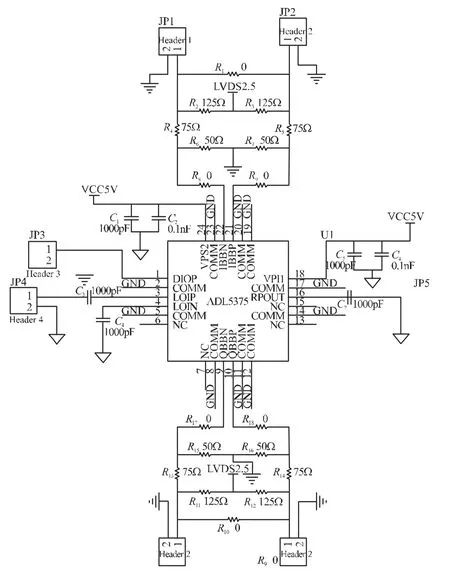

2.3 射頻PCB 板設計

本系統的基帶信號帶寬為150 MHz,射頻載波RF中心頻率2.4 GHz/900 MHz,因此電路設計屬于射頻電路的范疇,射頻電路的設計方法與普通的中低頻和數字電路在制作PCB 的時候有很大的區別。一些在低頻數字電路中對電路影響不大的因素在射頻電路中則可能直接導致設計的成敗,特別是信號節點的阻抗匹配問題。因為阻抗不匹配會引起反射和極大的衰耗[11]。

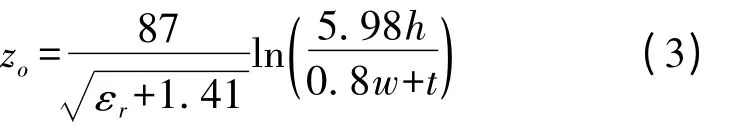

在射頻電路中,信號線需要按照傳輸線的理論分析和設計,必須保證信號線的特性阻抗和信號源及負載的阻抗匹配,這些特性阻抗通常為50 Ω。因此在設計PCB 的時候需要對板材的介電常數、板厚、信號線寬度進行嚴格的計算,確保信號線的特性阻抗正確。通常,可以用如下公式計算[12]:

其中,zo表示為信號線的特性阻抗,εr表示為板材介電常數,h 表示為板材厚度,w 表示PCB 線寬,t 為PCB 導線厚度。

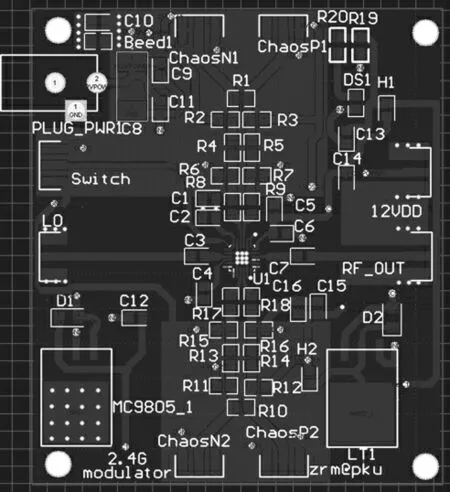

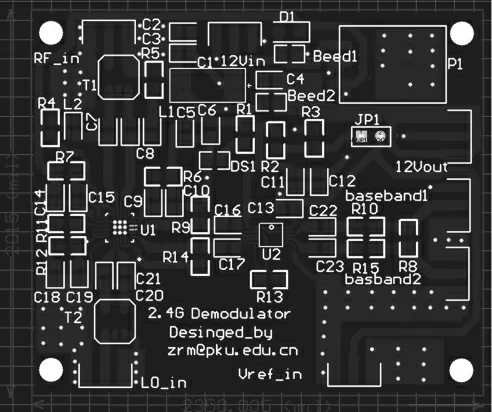

出于對PCB 制作成本的考慮,生產廠家會大批采購某一種介電常數的板材,采用這樣的板材設計PCB 時會節約一定的成本。經過和廠家的交流,我們得知廠家最常用的高頻PCB 板材介電常數εr為2.55,導線厚度t 為35 μm。根據公式,當特性阻抗一定時,導線的寬度隨著板厚增加而變寬,為了布線方便,這里采用最小板厚h 為0.5 mm。根據公式計算,可得到線寬w 為48 mil。圖5 和圖6 分別給出了調制器和解調器的PCB 圖。

圖5 調制器PCB 圖

圖6 解調器PCB

3 系統測試

3.1 測試方案及測試設備

根據項目的設計指標和系統的信號流程,本地載波信號由安捷倫射頻信號源N9310A 提供,該信號源頻率范圍可以從3 kHz 到3 GHz 可調,射頻輸出幅度/功率也是可調的;輸出的波形采用泰克公司的MSO4104 示波器進行測量,其3 dB 帶寬為1 GHz,采樣率為5 G,探頭采用有源探頭TAP1500,其帶寬為1.5 GHz。

該測試環境中,由碼發生器產生150 MHz 的隨機碼送給調制器,和射頻信號源送來經二功分器的射頻2.4 GHz/900 MHz 本振進行BPSK 的調制;已調信號和二功分器的另一路本振2.4 GHz/900 MHz信號進入解調器進行BPSK 的解調。中間的各點信號均可以用示波器進行測量。

3.2 測試結果

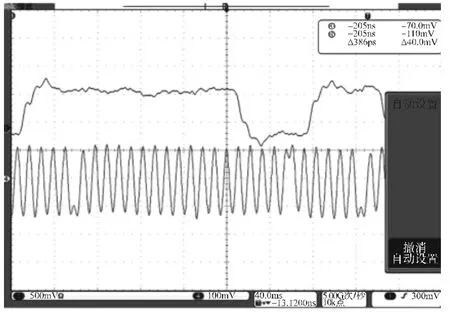

圖7 給出了基帶信號與已調信號的對應關系,該圖表明:①在基帶信號跳變時已調信號相位發生翻轉,完全符合BPSK 調制原理;②是已調波形與基帶信號有一定的延時;③每個碼片寬度內剛好對應的是6 個載波寬度,符合基帶信號和射頻信號的頻率比。

圖7 基帶碼發生器輸出VS 調制器輸出

圖8 基帶碼發生器輸出VS 解調器輸出1

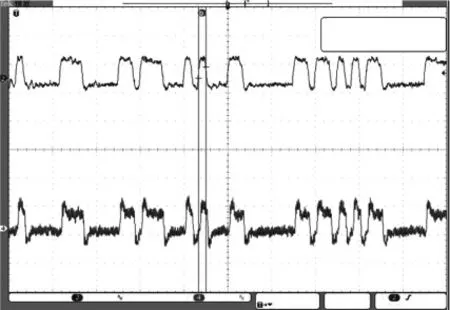

圖8給出了基帶碼發生器輸出和解調器輸出的對應關系,即收發碼元的對應關系。可以看到:一是接收碼和發送的碼對應關系沒有出錯;二是接收恢復的碼不僅幅度變小了很多,而且有一定的畸變(需要說明的是該圖中的波形均采用普通探頭而非差分有源探頭測得)。

圖9 與圖8 類似,給出了基帶碼發生器輸出和解調器輸出的對應關系。但此時采用的是2.4 GHz 載波。顯然,此時的解調的效果優于載波為900 MHz。

圖9 基帶碼發生器輸出VS 解調器輸出2

4 結束語

實驗測試結果表明:采用本文以ADI 公司的調制解調芯片ADL ADL5375 和ADL5382 作為核心的調制解調器,可以正確的對150 M 高速隨機碼進行調制和解調。將該調制解調器用于隨機碼脈沖編碼雷達中可以實現1 m 的測距分辨率和相應的測速功能。同時由于采用的載波是900 M,解調器輸出的波形有一定的畸變將會對脈沖壓縮的信噪比產生一定的影響,可以通過提高載波頻率至2.4 G 得以改善。

[1] Merrill I Skolnik. Radar Handbook[M]. 3rd ed. New York:McGraw-Hill,2008:386-410.

[2] 張世登.面向混沌碼雷達引信的單步預測其研究[D]. 北京:北京大學,2008:1

[3] 章新春.面向混沌碼雷達引信的Burg 算法應用研究[D]. 北京:北京大學,2008:5.

[4] 孟杲杲,朱曉華. BPSK 寬帶調制解調技術研究[D]. 南京:南京理工大學,2009:51-52.

[5] 周炯槃,龐沁華.通信原理[M].3 版.北京:北京郵電大學出版社,2008:188-189.

[6] 雷銘,鄒雪城,陳軍.高性能CMOS LVDS I/O 接口單元的設計研究[J].華中科技大學學報:自然科學版,2003,31(4):76-78.

[7] Jeff Waters.National Semiconductor’s LVDS Offers High-Speed Interface with FPGA/CPLD.Component Markets,2006.1.

[8] Analog Devices. ADL5375 Device Datasheet[DB/OL]. http://www.analog.com,2007:1-30.

[9] Analog Devices. ADL5382 Device Datasheet[DB/OL]. http://www.analog.com,2008:1-2.

[10] Analog Devices. AD8351 Device Datasheet[DB/OL]. http://www.analog.com,2004:1-16.

[11] 張仁民. 高速混沌碼發生器設計及寬帶調制解調技術研究[D].北京:北京大學,2011:44-46.

[12] 郭海鵬. 二次諧波雷達的設計與實現[D]. 北京:北京大學,2010:17-18.