基于FPGA 的高速CCD 工業相機系統設計*

沙 濤 ,劉棟鋮,汪海洋,孫寧建

(1.南京理工大學電子工程與光電技術學院,南京210094;2.東南大學電子科學與工程學院先進光子學中心,南京210096)

CCD 是一種集光電轉換、電荷存儲、電荷轉移為一體的半導體傳感器件,具有壽命長、重量輕、體積小、性能穩定、響應速度快、分辨率高、抗電磁干擾性好等優點[1-2]。因此CCD 在工業現場檢測有著廣泛的應用。目前,國內已開展CCD 相機系統的研究。例如《基于CPLD 的μPD3575D 線陣CCD 驅動電路設計》[3]一文中主要介紹了基于CPLD 的CCD驅動時序設計,對CCD 相機系統的設計做出了較高價值的鋪墊。在前人基礎上,本文給出了CCD 相機系統設計的具體結構;詳細介紹了CCD 外圍電路的設計;為使相機輸出圖像具有邊緣特征,便于檢測,本文還研究了基于FPGA 的圖像校正與處理方法。

1 硬件電路設計

1.1 系統硬件結構及分析

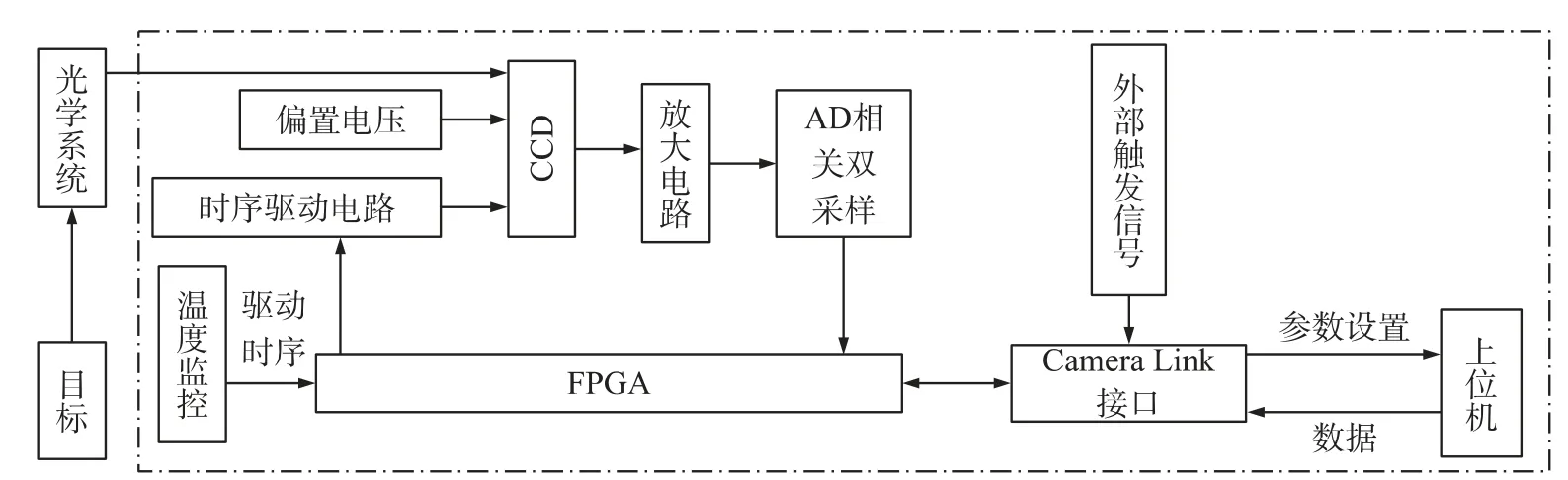

典型的CCD 相機系統主要包括CCD 驅動電路、信號處理電路、數據傳輸接口電路以及光學機械接口部分[4]。CCD 驅動電路一般由時序電路和偏置電壓電路構成,主要實現CCD 的驅動時序信號以及CCD的偏置電壓供電。信號處理電路主要完成CCD 輸出信號的A/D 轉換,轉換后的數據采樣,以及采樣后的數據處理等功能。數據傳輸接口電路主要實現相機與外部通信,完成圖像數據傳輸以及相機的外部控制等功能。光學機械接口是CCD 相機的輔助設備,提供與各種光學設備的輔助連接,從而實現光學系統與CCD 的耦合。本系統遵循典型CCD 相機結構的一般組成部分,結構框圖如圖1 所示。

檢測物在光源照射下經光學鏡頭被CCD 拍攝,CCD 在偏置電壓與驅動時序作用下產生像素輸出信號OS,OS 信號經放大電路放大后再由AD 采樣,AD 采樣后得到的并行數據送入FPGA。FPGA 即可實現圖像的噪聲校正及預處理,并將處理好的數據轉換成滿足CameraLink 接口通信的圖像數據。最終,圖像經CameraLink 接口發給上位機圖像采集卡,接受進一步處理。溫度監控模塊可實時監控相機溫度,外部觸發信號可實現相機曝光外同步。

圖1 本系統結構框圖

1.2 芯片選型

本文的相機系統主要用于工業流水線現場檢測,如大蒜等,要求相機具有高靈敏度,采樣速度快:約8 kHz 的線掃描行頻,分辨率至少1 024 像素等性能,因此選用加拿大Dalsa 公司的一款高速CCD 芯片IL-P3-B。IL-P3-B 器件具有速度快,信噪比高,光積分時間可調等優點,廣泛應用在高速運動圖像掃描成像與計算機圖像數據采集中。IL-P3-B的有效像素為2 048,像元尺寸為14 μm×14 μm,100%填充因子,單通道輸出,還具有高響應度和高藍光響應特性,而且動態范圍高達1 820 ∶1。IL-P3-B 最高驅動頻率為40 MHz,在有效像素為2 048 的情況下最高掃描行頻為19 kHz,滿足工業現場流水線檢測的高實時性應用要求。IL-P3-B 需要6 路時序驅動和10 路偏置電壓供電才能正常工作[5]。

主處理芯片選用Altera 公司的EP3C16F484 FPGA 器件。EP3C16F484 是Altera 公司的Cyclone3系列器件,具有低功耗、低成本、高邏輯資源等特點。和Cyclone2 系列器件相比,Cyclone3 器件密度提高1.7 倍,邏輯單元(LE)達到120 000,嵌入式存儲容量提高3.5 倍,達到4 Mbit[6]。因此,Cyclone3 器件EP3C16F484 是本系統較為理想的選擇。

1.3 IL-P3-B 外圍電路設計

線型CCD IL-P3-B 的偏置電壓都為固定的直流電壓,其中VPR 為光積分場效應管的漏極電源電壓,一般將其設置為14 V;VSTOR為存儲勢阱電壓,一般為2 V 左右;VSET為輸出柵上的偏置電壓,常為1.2 V 左右;VBB為輸出檢測二極管的P 區偏置電壓,常為-2 V 左右;VOD為輸出復位場效應管的漏極電源電壓[5]。對于偏置電壓電路的設計可以使用線性穩壓電源芯片LDO 和一些高精度的放大器輸出直接供電,只要滿足其電壓值大小即可。

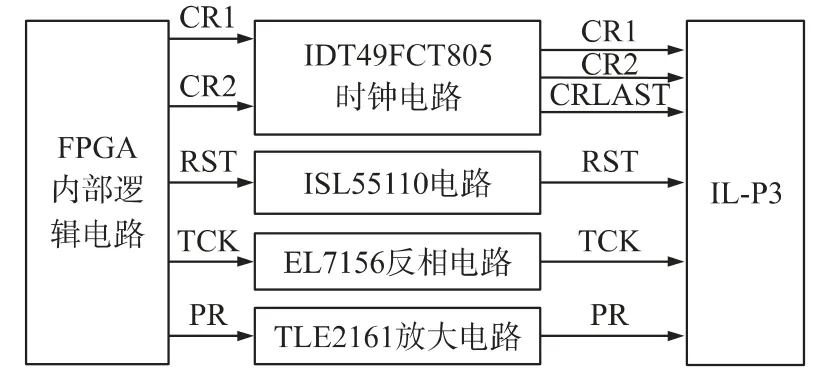

IL-P3-B 能否準確輸出像素,最關鍵的是6 路時鐘驅動信號(CR1、CR2、CRLAST、TCK、PR 與RST)的設計,且這6 路時鐘驅動信號的幅值不都是常見幅值(如RST 信號的高電平為7 V,TCK 的低電平為-3.5 V,PR 的高電平為4 V[5])。因此需要選用一些專用的驅動芯片驅動,這些驅動芯片則由FPGA 內部邏輯電路提供時鐘和控制信號,如圖2 所示。

圖2 IL-P3-B 驅動結構框圖

CR2 與CR1 信號同頻反相,CRLAST 與CR1 同頻同相,因此采用一款快速COMS 時鐘驅動芯片IDT49FCT805 同 時 驅 動 CR1、CR2 和 CRLAST。IDT49FCT805 有兩塊獨立的時鐘輸出,每塊有4 個輸出引腳,其中一塊用于CRLAST 與CR1,另一塊用于CR2,但要注意此芯片會將信號反相。RST 信號則由ISL55110 MOSFET 芯片驅動,ISL55110 是一款專業CCD 驅動芯片,可以達到9 V 左右的驅動電壓。TCK信號則由EL7156 驅動,但此芯片也會使信號反相。PR是用于積分時間(曝光)控制的信號,數據手冊中對PR信號的要求較為嚴格:PR 應是一組平滑的脈沖,如果PR 信號變化的太快,OS 信號的均勻性會因PR 信號的時鐘饋通效應而受到影響。因為電流驅動的PR 信號產生的時鐘饋通效應會比電壓驅動產生的要小[5],因此可以采用基于TLE2161 放大電路驅動。

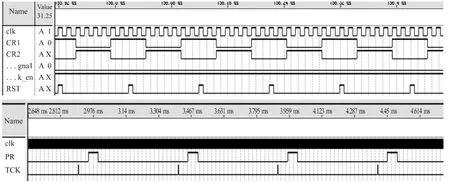

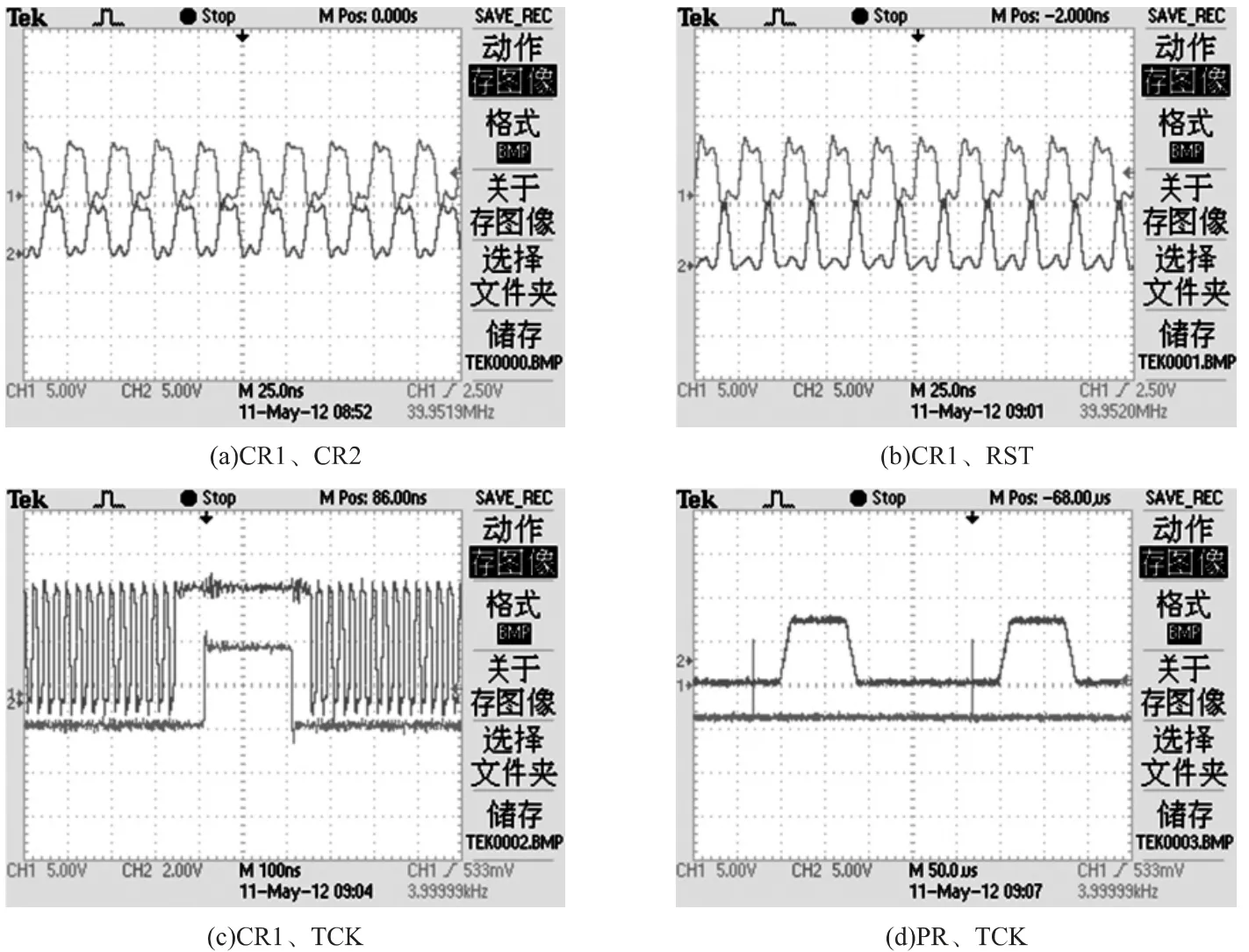

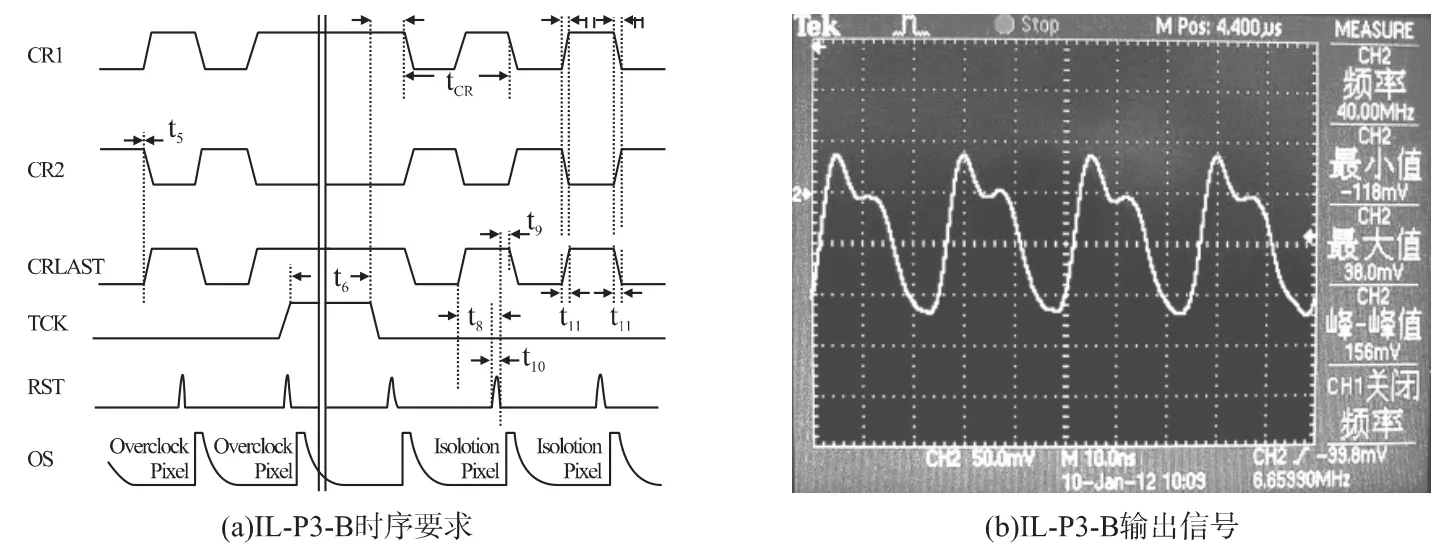

FPGA 由外部80 MHz 晶振提供時鐘,利用FPGA內部鎖相環(PLL)可以分頻得到40 MHz 的時鐘。CR1 為40 MHz,占空比1 ∶2的信號,CR2 與CR1 同頻反相,則可將CR1 取反得到CR2,CRLAST 與CR1 同頻同相,可以使用同一個信號驅動。RST 與CR1 同頻且其占空比為1 ∶4,可將80 MHz 的外部時鐘取反后與CR1 相與得到RST 信號。圖3 為FPGA 內部邏輯電路輸出的QuartusⅡ仿真結果。圖4 則為經過時序驅動電路后到達CCD 器件引腳的示波器(Tektronix 的TDS1012C-SC 型號,帶寬100 MHz)實測結果,可以看出結果滿足圖5(a)中IL-P3-B 的時序要求,并且PR 信號(圖4(d))的變化沿較為平滑,因而得到了較好的CCD 輸出信號(圖5(b))。

CCD 輸出的信號幅度較小,而AD 采樣需要的模數轉換量化位數又高[7],例如對輸出為1 V 的CCD 信號進行12 bit 的量化,那么量化的最低位只有244 μV。因此CCD 的輸出信號OS 需要采用放大電路放大。放大電路采用大帶寬的運算放大器MAX4224,帶寬600 M,增益調至為2。另外CCD 的輸出信號是交流信號,因此放大電路的輸入端需采用電容耦合方式,隔去直流信號。

圖3 FPGA 內部邏輯電路產生CCD 驅動信號的仿真波形

圖4 到達IL-P3-B 引腳的驅動信號實測波形

圖5 IL-P3-B 時序要求與其輸出信號的實測波形

2 系統噪聲分析與校正算法研究

2.1 系統噪聲分析

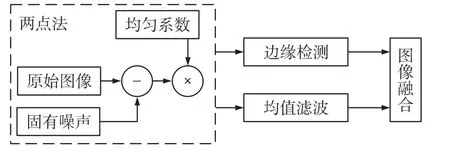

噪聲是決定圖像質量的重要因素。CCD 圖像傳感器的輸出信號是空間采樣的離散模擬信號,其中夾雜著各種噪聲和干擾,而噪聲會影響CCD 成像器件探測微弱光的能力。從微觀上講,CCD 相機噪聲主要有散粒噪聲、暗電流噪聲、轉移噪聲、復位噪聲、輸出放大噪聲等[8]。而且這些噪聲產生原因較為復雜,不利于在FPGA 的邏輯電路上建立模型,因而只能從宏觀上分析。宏觀上講,CCD 相機噪聲主要分為非均勻性噪聲(PRNU)與固定模式噪聲(FPN)。非均勻性[9]噪聲主要是由傳感器的光電響應不一致性產生的,固定噪聲是系統固有的噪聲。基于這一劃分,可以采用一種兩點法的實時校正方式加以校正。在深讀其他文獻[10-11]的實驗結果的基礎上發現兩點法雖可以校正上述兩種噪聲,但也會帶來一些影響,如兩點法中減去的固有的噪聲是固定的系數,但實際固有噪聲值并不固定,其次兩點法會使得圖像的一些邊緣信息弱化。對應用于工業檢測的本相機系統并不能完全適用,針對這一問題,本文利用FPGA 邏輯電路的并行特性加入了一種兩點法、邊緣檢測、均值濾波及圖像融合相結合的實時校正算法原理,使得校正后的圖像帶有邊緣信息,更加利于工業檢測。

2.2 并行校正算法原理及硬件實現

利用可編程邏輯器件FPGA 與Verilog HDL 語言的并行特點,實現如圖6 所示的算法流程。

圖6 并行校正算法原理框圖

算法流程分為3 個階段,第1 階段實現兩點法中減法與乘法運算。接著將第1 階段得到的圖像分別送到第2 階段的邊緣檢測與均值濾波模塊中,并行處理,并將得到的圖像在第3 階段中進行融合得到校正后的圖像。

兩點法采用適用于FPGA 邏輯電路的線性兩點法[10]:yi=(xi-bi)×ai。yi=輸出數據,xi=相機原始數據,bi=從原始數據中減去的固有噪聲值,ai=數據均勻校正系數。對于系數ai不為整數的運算可以使用定點法[11]實現,即定義一個6 bit 的寄存器型數據,高2 位表示整數部分,低4 位則表示小數部分。

邊緣檢測采用Sobel 邊緣檢測算子計算,Sobel邊緣檢測算子是一個3×3 的固定矩陣,很容易在空間上實現。Sobel 邊緣檢測不但產生較好的邊緣檢測效果,而且受噪聲的影響也比較小[12]。但由于本相機系統是線掃描的,每次曝光只能輸出一行像素值,所以需要FPGA 片內RAM 緩存3 行像素,從而形成動態的3 行流水線處理。均值濾波是求3×3窗口內像素的平均值,也需要3 行像素的RAM 緩存,但均值濾波最大的缺點是模糊了細節[13],因此需要與邊緣檢測相結合。

最后將對應的邊緣圖像與圖像融合模塊中設定的閥值作比較,邊緣圖像像素值大于閾值的像素點置為指定值(如最大值),反之則取對應像素點均值濾波后的像素值。在FPGA 實現上述算法流程后,所得的實驗結果見系統測試與結果分析一節。

3 系統測試及結果分析

系統由兩塊6 層印刷電路板PCB 組成,在測試相機之前,需確定相機的硬件部分無任何設計性錯誤和工藝故障,且各元器件均能正常工作。測試的主要目的是為了驗證系統的功能是否能實現以及系統性能是否達到要求。

試驗方法與步驟:

(1)因為CCD 是極易受靜電損壞的模擬器件,因而必須采用防靜電操作。

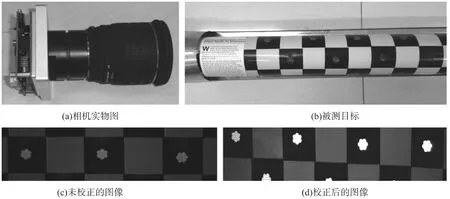

(2)將樣機(圖7(a))接上CameraLink 電纜并同時接到上位機圖像采集板卡。

(3)將樣機對準被測物體(圖7(b)),被測物是裝有日光燈的滾筒,用于模擬工業流水線現場。

(4)打開總電源,調節鏡頭光圈與焦距直到觀察到清晰圖像(圖7(c)、7(d))。

在上位機采用Dalsa 的X64-CL 采集卡并使用軟件CamExpet,對所設計的相機系統進行數據采集,形成二維圖像,實驗結果如圖7(c)、7(d)。圖7(c)為未加入校正算法采集到的圖像,圖7(d)為加入校正算法后采集到的圖像。可以看出,圖7(d)得到了較清晰的圖像,并且在實現了校正算法后得到了更加清晰及帶有邊緣信息的圖像,滿足項目中工業現場檢測的特殊要求。但在實驗結果中,我們也不難發現圖像中夾雜著有規律的條紋信息(圖7(d)),這主要是由測試光源使用的交流光源導致的,交流光源是50 Hz 的交流供電,與圖像中的50 Hz 的條紋信息剛好吻合。因此,在工業檢測中應使用隔離過的直流光源作為系統光源,這樣就不會產生條紋信息。本文在經過多個版本的電路測試后,發現電路設計的不同會對系統的噪聲有一定的影響,而相機的主要性能決定于CCD 器件。

圖7 實驗測試與實驗結果

4 結束語

本文對用于工業現場檢測的CCD 線陣相機進行了研制,給出了系統結構框圖、驅動結構圖及仿真與實測波形,設計的系統具有通用的CCD 相機功能,能結合上位機板卡采集完整圖像。另外用FPGA 實現了時序驅動和相機校正與處理功能。為今后設計具有FPGA 檢測處理功能的CCD 相機系統提供參考。

[1] 米本和也,陳榕庭,彭美桂. CCD/CMOS 圖像傳感器基礎與應用[M].北京:北京科學出版社,2006.

[2] 王祖軍,張勇,唐本奇.TCD132D 線陣CCD 總劑量效應的實驗分析[J].電子器件,2010,33(1):18.

[3] 陳赟,何惠陽.基于CPLD 的μPD3575D 線陣CCD 驅動電路設計[J].傳感技術學報,2006,19(6):2527-2528.

[4] 李麗莎,佟首峰,王雪松.基于雙線陣的CCD 的數據采集系統設計[J].儀器儀表用戶,2010,17(2):24-25.

[5] Dalsa.IL-P3-B Line Scan Sensors Datasheet[S].2000:1-8.

[6] Altera.Cyclone ⅢDevice Datasheet[S].2010:1-6.

[7] Analog.Complete 12-Bit 40 MHz CCD Signal Processor AD9945 Datasheet[S].2000:1-5.

[8] 許秀真,李自田,薛利軍. CCD 噪聲分析及處理技術[J]. 紅外與激光工程,2004,33(4):344.

[9] 張之江,鄒賓,陳迎娟.CCD 亞像素細分中的像素響應不均勻性補償技術[J].傳感技術學報,2005,18(1):57-58.

[10] 李玉玨.基于兩點法的實用FPA 非均勻性校正系統[J]. 激光與紅外,2007,37(8):754-755.

[11] 趙登超,胡君紅,鐘勝. 基于FPGA 的兩點非均勻校正模塊的設計與實現[J].微計算機信息,2006,22(29):4.

[12] 吳術路. 基于Sobel 算子圖像邊緣檢測的MATLAB 實現[J].電腦知識與技術,2010,6(19):5314.

[13] 李秀峰,蘇蘭海,榮慧芳.改進均值濾波算法及應用研究[J].微計算機信息,2008,24(1):235.