DICE加固結構觸發器的重離子實驗研究*

張筱穎,田海燕,于宗光*

(1.江南大學物聯網工程學院,江蘇無錫214122;2.中國電子科技集團公司58所,江蘇無錫214035)

重離子會導致航天器系統中的半導體器件發生單粒子效應SEE(Single Event Effect),隨著電路工藝尺寸的降低和集成度的提高,SEE對電子器件的影響已愈發嚴重,其中的單粒子翻轉SEU(Single E-vent Upset)作為導致集成電路出現故障的主要輻射原因已成為現今抗輻照加固研究的熱點[1-3]。

D觸發器作為CMOS集成電路中使用很廣泛的單元,是很容易發生SEE的,當觸發器電路受到重離子的干擾,單元中存儲的數據會發生錯誤,并且存儲的錯誤數據會一直保留到該單元下一次被改寫,這會影響電路的正常工作[4],因此觸發器單元抗輻照能力的強弱會直接影響整個電路的抗輻照性能[5-7]。

實驗主要是對DICE加固結構觸發器進行重粒子研究,分別選用氯(Cl)、鍺(Ge)、碘(I)這3種不同的重粒子在不同頻率、不同驅動能力、不同版圖結構、不同電壓這4種情況下對電路進行單粒子輻照試驗,分析電路翻轉的次數及翻轉閾值,以此來驗證電路抗SEU性能的有效性。

1 單粒子效應產生機制

單粒子效應SEE(Single Event Effect)是指高能粒子入射到半導體器件內部時會在穿透路徑上發生電離,此時電路中的結點會因為吸收電離所產生的電子或空穴而改變原來自身的電位[8-9],導致電路出現故障,影響器件的可靠性。

作為單粒子效應中的主要內容,單粒子翻轉SEU(Single Event Upset)大多發生在存儲器件和邏輯電路中,表現為電路中觸發器和存儲單元的翻轉、邏輯錯誤等[4,10]。它的產生是因為入射的高能粒子對集成電路的敏感結點撞擊從而導致硅材料電離,并在重離子運動徑跡周圍形成大量的電荷,當結點上積淀的電荷達到臨界狀態時,就會產生瞬態電流來觸發邏輯電路,導致邏輯狀態發生改變,錯誤的邏輯電平會導致電路發生“軟”失效[11-12]。

2 DICE加固結構觸發器

文獻[13]和文獻[14]中提到,在 0.18 μm 的工藝條件下,雙互鎖存儲單元DICE(Double Interlocked Storage Cell)結構具有好的抗SEU的效果,該電路不但具有高速、低功耗等特點,而且當電路中有單個結點發生電位擾動時,電路不會發生翻轉,同時還避免了基于鎖存復制和反饋結構的抗SEE單元的缺點。

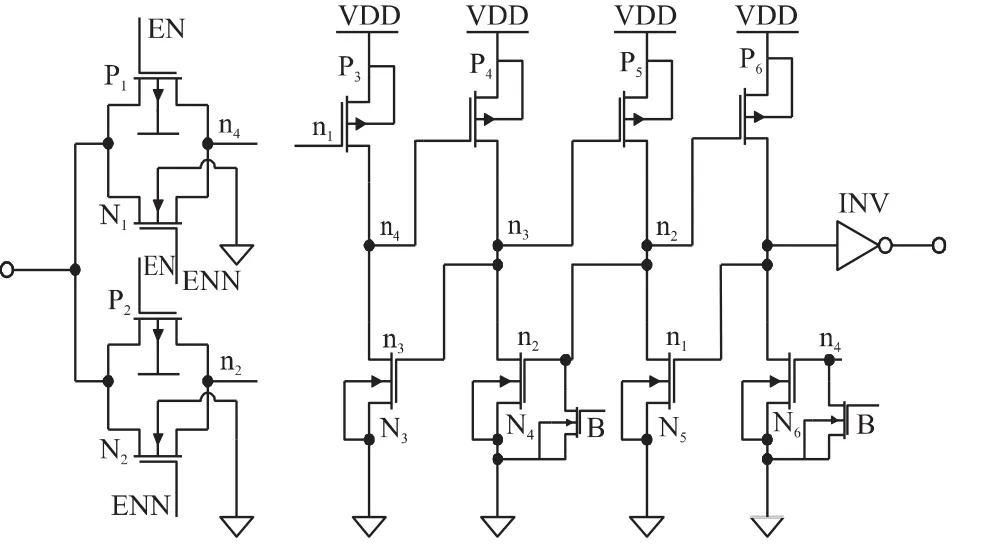

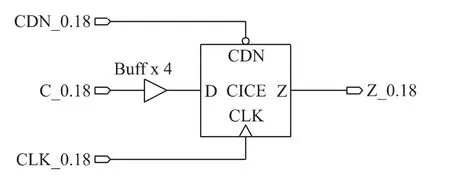

DICE單元結構組成的觸發器如圖1所示,P型晶體管 P3,P4,P5,P6和 N 型晶體管 N3,N4,N5,N6反向構成反饋環,形成4個互鎖的反相器級聯,該結構單元中有4個背靠背連接的帶有反相器的存儲結點:n1、n2、n3、n4用來儲存兩對互補的數據,其中n2和n4,n3和n1是成對的結點。與傳統互鎖電路不同的是該電路中每一級的P管、N管柵極分別由前一級和后一級的輸出觸發,這樣一來每個存儲結點的狀態都由與其相鄰的存儲結點控制,并且相鄰的儲存結點間相互獨立。當電路中只有一個存儲結點的電壓發生改變時,受其他結點反饋的影響,DICE內存儲的狀態不會發生改變。在對DICE結構進行寫入時,會要求成對的2個結點的電壓同時發生改變,當對4個存儲結點同時進行寫入時,寫入的時間會縮短[15]。

此外,在圖1所示的觸發器電路中采用了附加晶體管冗余鎖存結構,當鎖存器不工作時,會強制N管的柵極接地,提高觸發器電路的抗SEE的能力,減輕了SEU效應的影響[16]。

圖1 DICE核心部分結構圖

3 實驗方案

3.1 實驗裝置

本次實驗是利用中國科學院串列加速器核物理國家實驗室的串列加速器實驗靶站對測試芯片進行單粒子實驗。實驗時,經過加速器加速的離子會通過束運線進入輻照終端的真空靶室內,穿過注量探測器后,均勻地照射在被測器件上,被測器件的電路板放置在一個可以自由上、下移動和旋轉的圓盤上,被輻照時,芯片會處于動態偏置的狀態。

3.2 實驗測試系統

電路單粒子翻轉效應的檢測系統包括硬件系統和軟件系統2個部分。

3.2.1 硬件測試系統

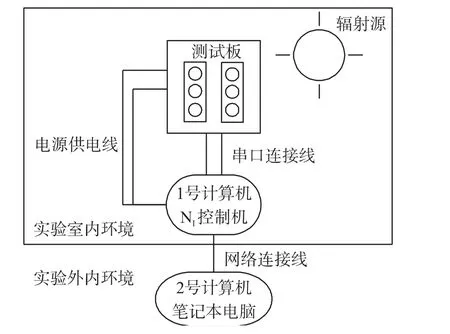

硬件測試系統主要包括:1號計算機NI控制機、2號計算機和實驗測試板這3個部分,硬件測試系統的工作原理如圖2所示。

圖2 硬件測試系統

(1)1號計算機

NI控制機的功能有3個:

①作為實驗板的上位控制機:單粒子效應實驗的上位機程序會在NI控制機平臺上運行,通過串口與實驗板進行通訊。

②作為單粒子翻轉檢測平臺:負責收集實驗測試板發來的單粒子翻轉的情況,并記錄翻轉的次數和翻轉閾值。

③作為單粒子鎖定檢測及電流控制平臺:負責顯示實驗測試板的電流值,并控制測試板的上電和掉電的情況。

(2)2號計算機

單粒子效應的實驗環境惡劣,為了保證實驗在可控和安全的條件下完成,另需一臺電腦做遠程監控,該電腦通過網口連接到NI控制機上。

(3)試驗測試板

在輻照時,實驗測試板共有2種方式:正常工作模式和測試模式。

3.2.2 軟件測試系統

測試系統的軟件測試部分是由實驗測試板上控制芯片內的下位機控制程序和上位機程序這2個部分。

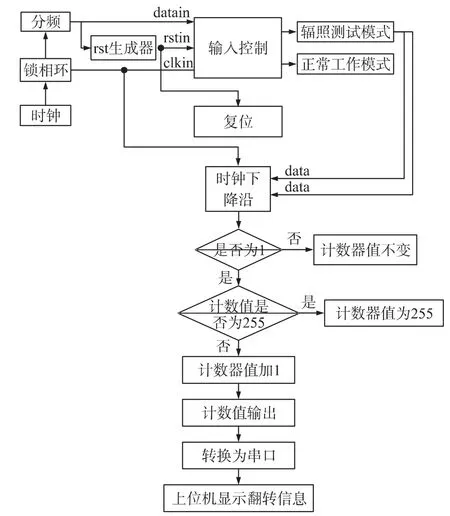

(1)下位機控制程序

控制程序的功能是控制被測芯片與標準芯片的輸出復位、信號加載、輸出結果傳送、并將兩者的輸出結果進行比較等,其工作流程如圖3所示。下位機程序在測試芯片上進行上電復位、時鐘信號與數據信號的加載,讀出輸出信號,通過與標準芯片的對比,將檢測結果通過串口發送給上位機。

圖3 下位機翻轉檢測流程圖

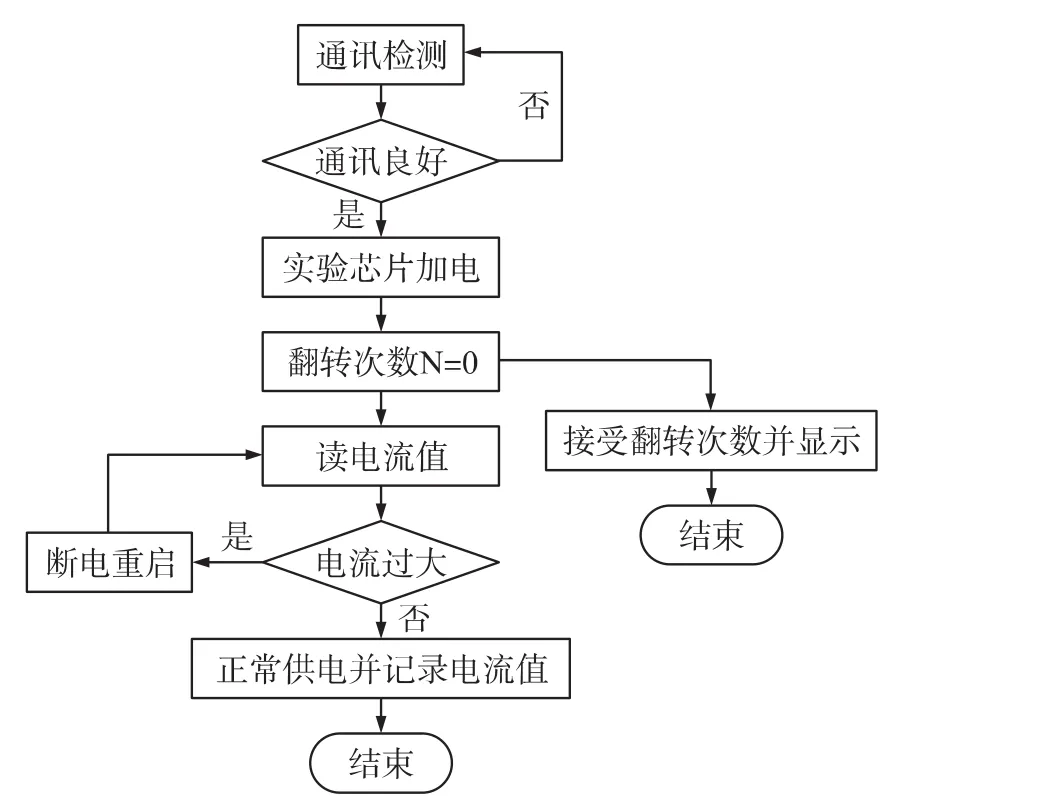

(2)上位機控制程序

上位機程序在NI測試系統中可通過串口對單粒子效應板進行數據讀取,通過NI的供電板卡對輻照實驗板供電,并采集電源電流大小。如果電流值超過設定的電流閾值,由系統控制被測芯片的電源通斷,同時實時顯示電流值及翻轉次數,其工作流程如圖4所示。

3.2.3 測試系統的SEU檢測原理

將被輻照的芯片上每一條DFF鏈的輸出與標準芯片的輸出進行比較,翻轉一次就累計計數一次,出現翻轉就記為出錯,出錯數通過串口發送到上位機顯示。

實驗時,束流時間為2 h~10 h,針對SEU指標,采用3種離子氯(Cl)、鍺(Ge)、碘(I)分別入射實驗電路,累計注量達到107n/cm2,記錄單粒子翻轉效應是否發生和發生的次數。

圖4 上位機如軟件操作流程圖

4 實驗內容

4.1 實驗內容

在3.3 V和1.8 V兩種電壓的情況下對DICE加固結構觸發器鏈進行輻照試驗,來測試其抗SEE的能力。

圖5 DICE單元電路原理圖

DICE電路結構如圖5所示,每條鏈的區別是內部關鍵結點n2和n4在版圖上的間距不同,圖中的n2-n4,n3-n1,n8-n6,n7-n5都是成對的結點。在設計電路版圖時,會將上面這4對結點的間距分開,避免造成結點的同時翻轉,因為在DICE結構中,如果相鄰的兩個結點同時發生翻轉,那么輸出也會翻轉。

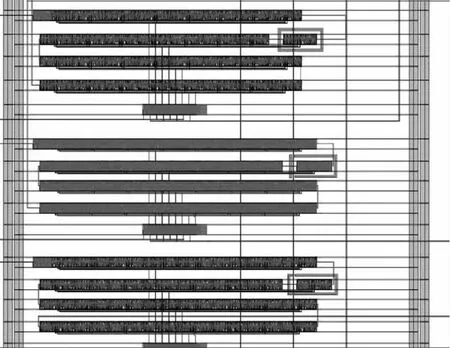

實驗中會對整個觸發器鏈進行輻照,我們將對不同工作頻率、不同結點驅動能力、不同電源電壓的觸發器進行討論,DICE單元結構如圖6所示,DFF鏈由32級的觸發器級聯形成,DFF觸發器鏈的電路圖如圖7所示。

圖6 DICE電路框圖

圖7 DICE觸發器鏈

我們還會對不同版圖結構的觸發器進行討論,此處的不同版圖結構主要是指DICE觸發器關鍵結點之間不同的間距,通過不同的間距可以比較相鄰結點的干擾以及電荷分享機理對DICE觸發器的影響,不同間距的觸發器版圖如圖8所示。

圖8 DICE觸發器版圖結構

間距分類情況如表1所示。

表1 版圖間距分類情況

2倍驅動=3 =4

5 實驗結果與討論

5.1 實驗結果

5.1.1 不同的頻率

其他條件相同的情況下,在頻率分別為25 MHz和50 MHz時進行單粒子實驗,得到的SEU情況如表2、表3所示。

表2 頻率為25 MHz時的翻轉情況

表3 頻率為50 MHz時的翻轉情況

根據表2和表3的實驗結果,我們可以看出:相同電壓條件下,隨著頻率的增加,電路的翻轉次數增加,翻轉閾值會隨之降低。此現象可能是由于單粒子瞬態擾動引起的,觸發器在工作時,讀入了受擾動的數據,導致輸出數據出錯。

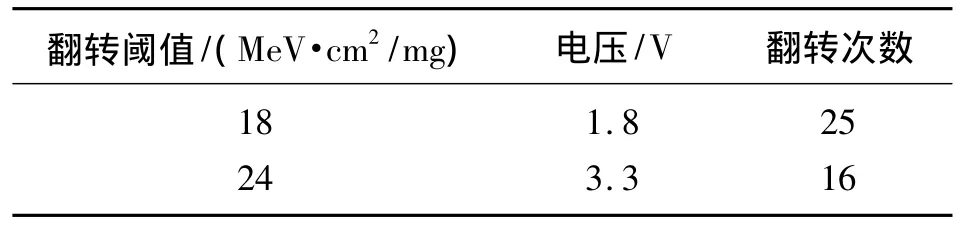

5.1.2 不同的驅動能力

我們將觸發器內部采用一倍驅動和兩倍驅動能力的電路進行比較,此時電路工作在25MHz,翻轉情況如表4、表5所示。

表4 一倍驅動時的翻轉情況

表5 兩倍驅動時的翻轉情況

根據表4和表5的實驗結果,我們可以看出:相同電壓條件下,隨著結點驅動能力的增加,電路的翻轉數減小,翻轉閾值也會有所提高,此現象是由于結點驅動電流能抵消一部分單粒子擾動對電路的影響,驅動能力越強,抵抗單粒子效應的能力就越強。但盲目的增加結點驅動能力會給電路帶來版圖和功耗的問題。因此,在提升電路抗輻照能力的同時,還需要折中考慮電路其他方面的性能。

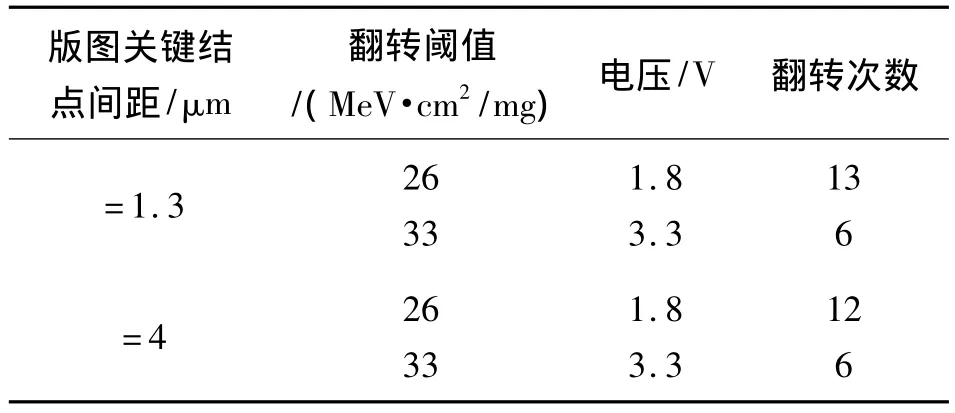

5.1.3 不同的版圖結構

對于不同間距的版圖結構,測試電路的翻轉情況如表6、表7所示。

從表6可以看出,當關鍵結點之間的距離減小時,會因為相鄰結點的擾動以及電荷分享機制的存在,導致觸發器抗單粒子效應的能力降低。但增加了關鍵結點之間的距離后,會提升抗單粒子效應的能力,當間距足夠大之后,利用保護環提高單粒子效應能力也不是很明顯。所以,增加關鍵結點的間距對提升觸發器抗單粒子效應是有益的。

表7 兩倍驅動能力時的翻轉情況

兩倍驅動能力的電路本身就有較好的抗單粒子效應的能力,此時再利用增加關鍵結點的間距對提升抗單粒子效應的能力已經不明顯。

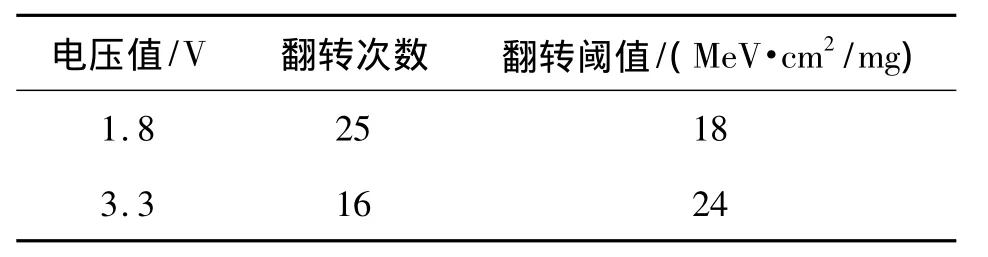

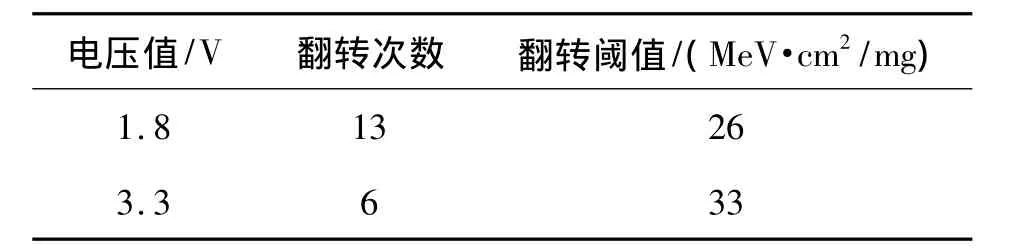

5.1.4 不同的電壓

一倍驅動能力的觸發器,工作在25 MHz的條件下,1.8 V和3.3 V兩種工作電壓的觸發器翻轉閾值數據如表8所示。

表8 電壓不同時的翻轉情況

在實驗中,隨著電源電壓的降低,出現錯誤的翻轉閾值也隨之降低,錯誤數增加。這是因為隨著電源電壓的降低,關鍵結點存儲的電荷減少,而單粒子脈沖擾動產生的擾動電荷并沒有減小,所以,擾動對電路的影響隨之增大。

5.2 實驗結果分析

針對DICE結構的觸發器,在不同工作頻率、不同驅動能力、不同版圖結構以及不同電壓的條件下進行輻照實驗,觀測到以下幾種現象:

①隨著工作頻率的增加,DICE結構觸發器抗單粒子效應的能力隨之降低。

②隨著結點驅動能力的增強,DICE結構觸發器抗單粒子效應的能力隨之增加。

③隨著工作電壓的降低,DICE結構觸發器抗單粒子效應的能力隨之減小。

④通過改變關鍵結點之間的間距,可以改善DICE結構觸發器的抗單粒子效應的能力。但大于一定距離后,抗輻射能力則不再變化。

產生現象①的原因是:隨著工作頻率的增加,SEE對DICE觸發器的擾動不僅只有SEU,還增加了單粒子瞬態擾動效應,錯誤的數據會從輸入端存入觸發器中。隨著頻率的不斷增加,單粒子瞬態擾動效應對電路的影響也會越來越嚴重,最終會超出單粒子翻轉效應,成為單粒子效應對電路產生影響的主導因素。

產生現象②的原因是:通過增加結點的驅動能力,可以抵消一部分單粒子效應對電路的影響,當結點受到擾動時,大的驅動能力會迅速補償關鍵結點受到的擾動,降低了結點翻轉的概率,但盲目的增加結點驅動能力會給電路帶來版圖和功耗的問題。所以,在提升電路抗輻照能力的同時,需要折中考慮電路其他方面的性能。

產生現象③的原因是:隨著電源電壓的降低、工藝的改進,關鍵結點的電容也隨之降低,結點存儲的電荷減少,但單粒子脈沖擾動產生的擾動電荷并沒有減少。所以,單粒子效應對電路的影響會隨著工藝關鍵尺寸和電源電壓的減小而增加。

產生現象④的原因是:當某結點發生單粒子效應,其電離的電子-空穴對有一定概率會被相鄰結點收集,對相鄰結點的狀態產生擾動,并且如果粒子大角度入射,會導致電荷分享及單粒子多結點擾動機制的發生,從而導致觸發器抗單粒子效應的能力降低。但通過增加關鍵結點之間的距離或加入保護環則可以降低電荷被相鄰結點收集的概率,降低電荷分享及單粒子多結點擾動機制的發生,從而提高抗單粒子效應的能力。

6 結論

基于0.18μm工藝平臺,對DICE觸發器加固結構進行輻照試驗,驗證SEU對體硅CMOS工藝器件及電路的影響。通過對實驗數據的分析與總結,可以得出:在實際工作中合理考慮各種參數的大小,可有效地提高DICE結構抗SEE的能力,滿足航空航天應用的需求。

[1]趙洪辰,海潮和,韓鄭生,等.一種抗總劑量輻照的NMOSFETs[J].電子器件,2004,27(4):578-580.

[2]李飛,安海華.0.18 μm NMOS的重離子單粒子瞬態脈沖的仿真模擬[J].電子器件,2011,34(5):558-561.

[3]Maru A,Shindou H,Ebihara T,et al.DICE-Based Flip-Flop with SET Pulse Discriminator on a 90 nm Bulk CMOS Process[J].IEEE Trans on Nucl Sci,2010,57(6):3602-3608.

[4]張英武,袁國順.一種抗單粒子全加固D觸發器的設計[J].固體電子學研究與進展,2009,29(3):404-406.

[5]Baze M P,Buchner S P.Attenuation of Single Event Induced Pluses in CMOS Combinational Logic[J].IEEE Trans on Nucl Sci,1997,44(6):2217-2223.

[6]Ya V,Stenin I,Cherkasov G,et al.Memory-Cell Layout as a Factor in the Single-Event-Upset Susceptibility of Submicron DICE CMOS SRAM[J].Russian Microelectronics,2011,40(3):170-175.

[7]Tsai C H,Wu M H,Chang C F.Quasi-Planar Bulk CMOS Technology for Improved SRAM Scalability[J].Solid-State Electronics,2011,65(184):3551-3561.

[8]沈鳴杰,戴忠東,俞軍.一種新型的抗單粒子翻轉的D觸發器[J].復旦學報(自然科學版),2006,4(4):475-479.

[9]Schwank J R,Dodd.Total Ionizing Dose and Single Event Effects Hardness Assurance Qualification Issues for Microelectronics[J].IEEE Trans on Nucl Sci,2008,55(4):- .

[10]Bhuva B L,Black J D,Massengill L W.RHBD Techniques for Mitigating Effects of Single-Event Hits Using Guard Gates[J].IEEE Trans on Nucl Sci,2005,52(6):2531-2535.

[11]Favrat P.High-Efficiency CMOS Voltage Doubler[J].IEEE J of Solid-State Circuits,1998,33(3):410-416.

[12]沈鳴杰.CMOS工藝集成電路抗輻射加固設計研究[D].上海:復旦大學,2006.

[13]趙金薇,沈鳴杰,程君俠.改進型抗單粒子效應D觸發器[J].上海:半導體技術,2007,32(1):26-28.

[14]李鵬,孫永節,陳建軍,等.基于Muller_C單元和DICE單元的抗輻照D觸發器設計[J].計算機工程與科學,2012,34(3):35-40.

[15]劉真.標準單元抗單粒子瞬態效應版圖加固技術與驗證方法研究[D].國防科學技術大學,2011.

[16]章凌宇,賈宇明,李磊,等.基于DICE結構的抗輻射SRAM設計[J].微電子學,2011,41(1):107-110.

[17]郭天雷,韓鄭生,海潮和,等.PDSOI靜態隨機存儲器的總劑量輻照加固[J].電子器件,2007,30(3):794-798.