利用CPLD提高FPGA加載速度

李春雨,張麗霞

(1.浙江機電職業技術學院電氣電子工程學院,杭州310053;2.諾基亞西門子通信有限公司,杭州310053)

現場可編程門陣列FPGA常用來進行大數據量的處理,并且可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中使用越來越廣泛[1]。FPGA是基于SRAM結構的,每次上電時都需要重新加載程序,且隨著FPGA規模的升級,加載程序的容量也越來越大,因此提高其加載速度是產品設計必須妥善解決的一個問題。本文介紹了通過CPLD對FPGA的加載方式的串行改進方式,滿足通信系統的加載速度快,占用資源少的要求。并用Verilog HDL實現,在Modelsim中進行仿真和驗證結果,在自行設計的時鐘板上驗證通過,而且可以擴展到所有類似系統中[2]。

1 配置方式介紹

FPGA的加載配置,大部分是將配置數據存放在FPGA組成系統的存儲器件上,系統上電時由控制器讀出配置數據再傳送給FPGA進行配置[3]。

FPGA的配置方式最常用的有JTAG,從并,從串[4]3種,不同廠家叫法不同,但實現方式基本都是一樣的。單板調試階段常用JTAG模式,單板正式工作時通常采用從串或者從并方式。從并和從串模式各有優點,從并加載模式一個DCLK傳送一個字節(8 bit),因此速度快,但是占用FPGA管腳多,以Altera公司CycloneⅢ系列為例,從并模式(FPP)占用23個FPGA專用管腳,且這些管腳在不同的邏輯Bank內,當各Bank之間接口電平不同時,即連接到控制器的23個管腳電平就要各不相同,對控制器來說通常是難以實現的,在這種情況下從串就成為唯一的選擇。

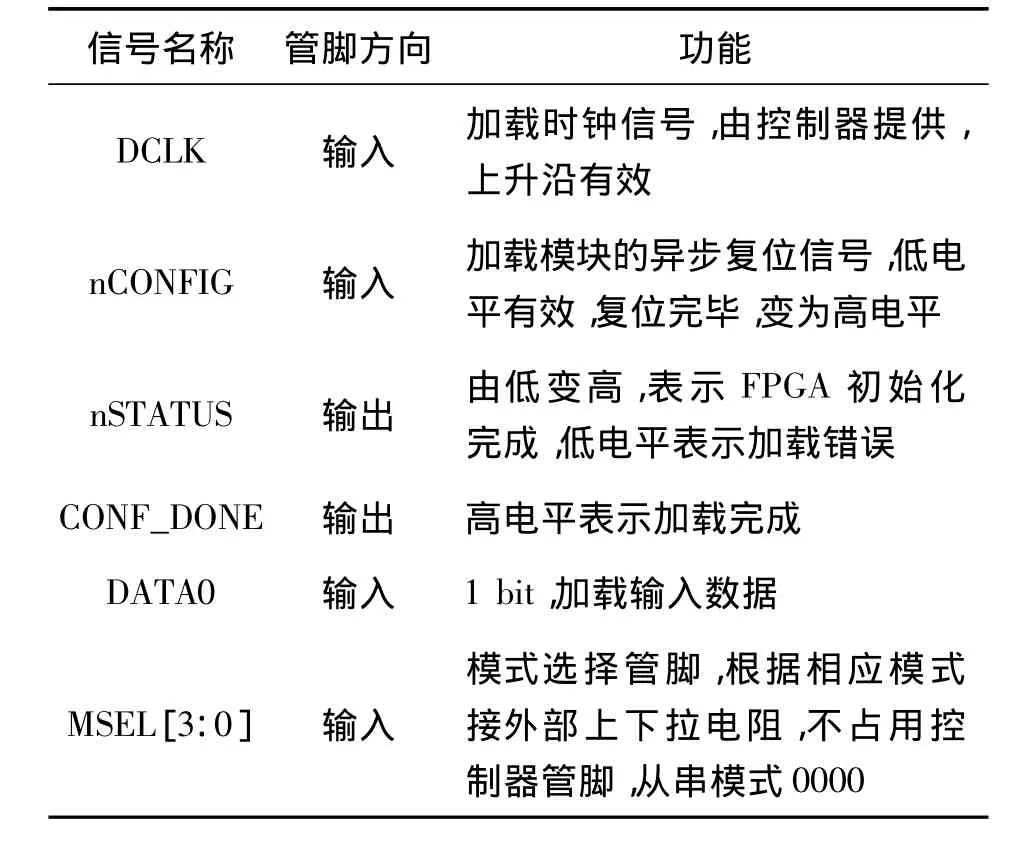

以Altera公司CycloneⅢ系列FPGA為例,與從串加載相關的管腳見表1[5]。

表1

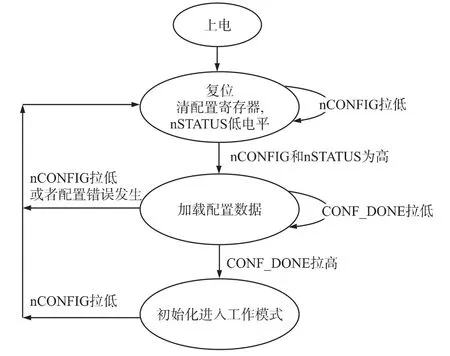

加載流程圖如圖1所示。

圖1 CycloneⅢ從串加載流程

各種型號的FPGA從串加載英文名稱雖然有些差異,但是加載流程基本如圖1,每種型號的FPGA配置文件大小是固定的,和使用的邏輯資源多少無關,以CycloneⅢ系列的EP3C120為例,其大小是14.3 Mbit[5]。

2 從串加載方式的實現

2.1 以CPU作為FPGA加載控制器

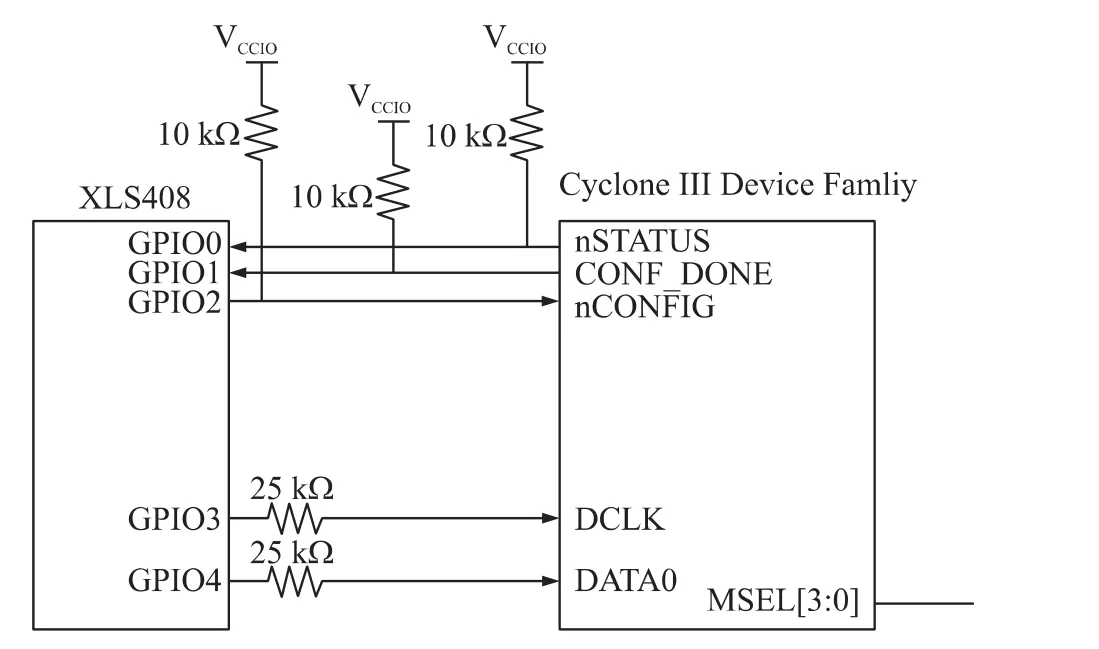

CPU可以采用嵌入式微處理器[6]的GPIO口和FPGA的加載配置接口連接,框圖如圖2所示。

其缺點是DCLK也要由CPU GPIO口模擬,GPIO口的速度較慢,以RMI公司的XLS408為例,GPIO口模擬最大時鐘2 MHz,如前面說EP3C120配置文件14.3 Mbit,加載時間為7.15 s。如果基于主頻較低的ARM7處理器,對于CycloneⅡ系列中的EP2C35,配置文件大小 1.16 Mbyte,加載時間需要 1.5 min 30 s[7],對于時間比較敏感的通信產品來說,用戶的體驗就會很差,通常該加載時間要求小于2 s。

圖2 XLS408從串加載流程

3 基于CPLD作為FPGA加載控制器的改進方案

3.1 改進方案介紹

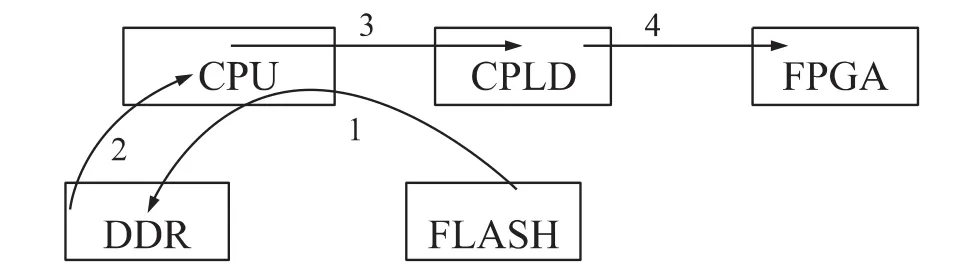

采用基于DDR顆粒的CPLD作為控制器的方案,CPLD的IO管腳都可以約束到時鐘信號上,只要CPLD內部的布線資源足夠,輸出的加載時鐘可以跑到上百兆,寫入CPLD的數據采用并行接口,大大提高FPGA加載速度。加載方案如下:

圖3 基于CPLD加載數據流向圖

本方案中CPU采用RMI公司的XLS408,CPLD采用 Lattice公司的 LCMXO1200,FPGA采用ALTERA公司的 CycloneⅢ EP3C120,DDR采用9片Hynix DDR2顆粒。

1號線表示,CPU通過16 bit localbus總線讀取存儲在Flash里的FPGA文件,并搬運到DDR里,這一步可以在加載前先做,不占用加載時間。

2號線表示,CPU讀取DDR數據搬移到CPU內部緩存中,DDR接口速度較快,DDR2時鐘266 MHz,數據位寬64 bit,幾乎不占用加載時間。

3號線表示,CPU通過8 bit localbus總線寫到CPLD內部寄存器,而localbus總線是異歩并行總線,以MIPS系列CPU XLS408為例,XLS408工作時鐘66.7 MHz,寫總線周期最快需要10個工作時鐘周期,即6.67 MHz,這一步受localbus總線速度限制。

4號線表示通過CPLD和FPGA之間的串行接口,寫加載配置數據到FPGA中,寫FPGA的速度決定于串行接口的DCLK頻率。

本方案的優點,1,2兩條路徑可以在加載之前處理,且運行速度快,不占用加載時間。加載時間只受3,4步限制,3步是并行總線,位寬8 bit,速度相對串行總線已經大為提高,4步受限點是CPLD輸出的DCLK頻率限制,CPLD輸出時鐘可以高達上百兆,加載時間會大為縮短。

3.2 程序實現

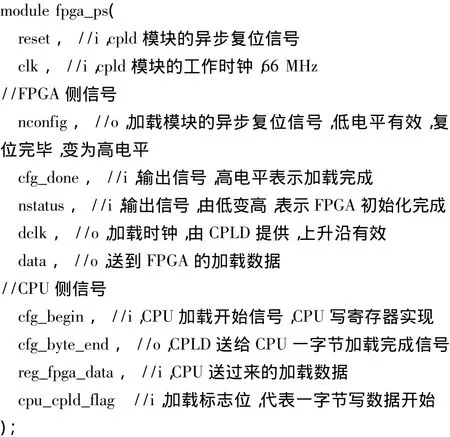

CPLD 程序采用 Verilog[8]語言實現,該加載模塊接口定義如下:

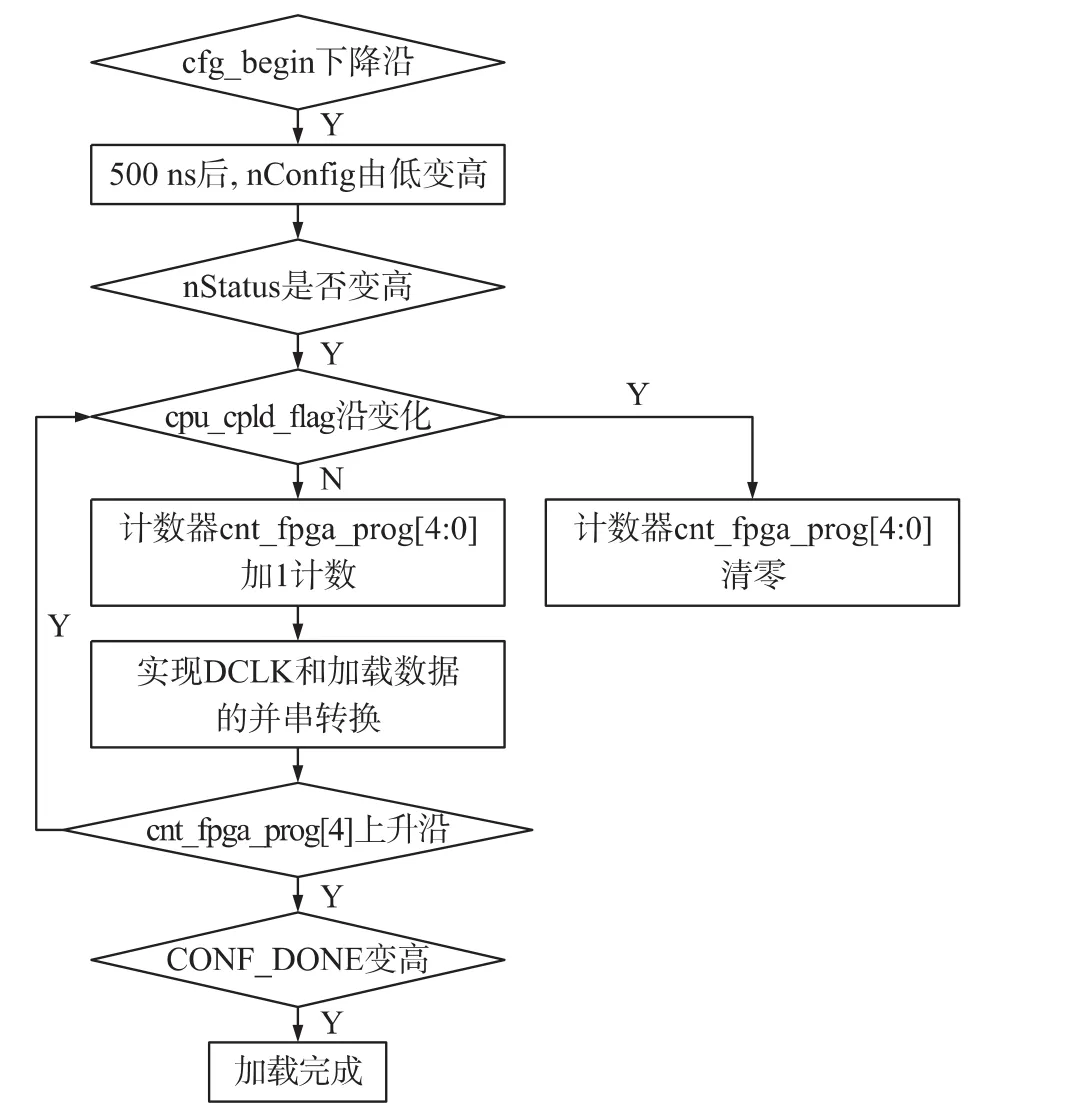

程序實現流圖如圖4所示。

DCLK和FPGA加載串行數據輸出部分代碼如下:

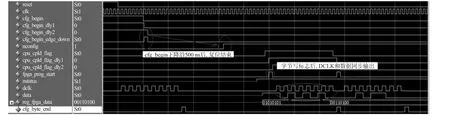

在FPGA加載環節,CPU通過8 bit的Localbus總線先是寫CPLD數據寄存器,一字節寫完后,CPU會將標志寄存器cpu_cpld_flag翻轉,CPLD檢測到寄存器cpu_cpld_flag的雙沿變化后,計數器cnt_fpga_prog[4:0]開始計數,其中 cnt_fpga_prog[0]是 CPLD工作時鐘的二分頻,該時鐘送給FPGA加載接口,做為DCLK,利用cnt_fpga_prog[3:1]的變化范圍實現并行數據到數據的變化,因為都是通過同一計數器實現,因此能方便的實現數據和DCLK的同步,當cnt_fpga_prog[4]計數到1 后,cnt_fpga_prog[4]上升沿有效,代表一字節數據已經成功加載到FPGA,CPU就開始通過localbus總線寫下一字節數據。

圖4 基于CPLD從串加載FPGA的程序流程圖

圖5 程序仿真波形

4 仿真及改進結果分析

基于modelsim 6.5SE仿真波形如圖5所示。

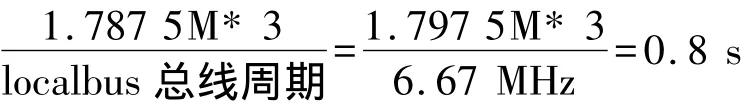

由上面波形可以看出CPU每加載一字節數據需要寫兩次CPLD寄存器,一次寫加載數據,一次寫標志寄存器,讀一次CPLD寄存器,讀cnt_fpga_prog[4]上升沿,共3個localbus總線周期,localbus頻率最快6.67 MHz。因此 CPU加載 14.3 Mbit,亦即1.787 5 Mbyte數據到CPLD共需時間:

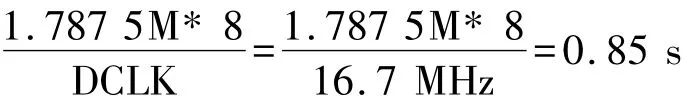

CPLD需要8個DCLK周期寫一字節數據到FPGA,CPLD工作時鐘33M時,DCLK 16.7 MHz,因此加載14.3 Mbit數據到FPGA,共需時間:

因此當FPGA使用EP3C120時,采用基于CPLD的從串加載方式,共需要加載時間1.65 s,滿足通信產品FPGA加載時間小于2 s的要求。

從上述分析可以得出結論,如果提高CPLD的工作時鐘,CPLD加載FPGA的時間就會進一步縮短,當CPLD工作時鐘100 MHz時,DCLK達到50 MHz,CPLD加載配置數據到FPGA時間可以縮短到0.29 s,加載速度會更快。

5 結束語

使用基于 CPLD的 FPGA加載方案,相對于CPU直接加載方案,加載時間只有原先的十分之一,且有進一步提高空間,滿足通信系統快速啟動的要求,且該方案并不局限于本文所提到的器件,可以應用于各廠家的FPGA中,具有很高的實用價值。

[1]關珊珊,周潔敏.基于Xilinx FPGA的SPI Flash控制器設計與驗證[J].電子器件,2012,35(2):216-220.

[2]王小峰,周吉鵬.一種FPGA在線配置Flash的方法[J].電子器件,2006,29(3):902-904.

[3]董宏成,魏楊.基于ARM和NAND Flash的FPGA加載配置在TD—LTE 中的實現[J].電子技術應用,2012,38(07):26-30.

[4]Xilinx,Spartan3e,Xapp502,Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode[S].2009.

[5]Altera,cyclone Ⅲ,Configuration altera FPGAs[S].2010.

[6]葛立明,范多旺,陳光武.基于ARM的FPGA加載配置實現[J].微計算機信息,2007,1(2):244-245.

[7]胡啟道,張福洪,戴紹港.基于MCU的FPGA在線配置[J].電子器件,2007,30(3):1049-1056.

[8]王靜霞.FPGA/CPLD應用技術(Verilog語言版)[M].北京:電子工業出版社,2011.