一種基于雙口RAM的冗余系統通信方法

徐 軍 張 磊 孫軍峰

應用于軌道信號系統的車載信號設備,主要用于采集狀態數據和輸出控制指令,在運行過程中通信數據量大,而且通信過程必須具備極高的安全性和可靠性。

車載信號設備開發過程中,需要考慮多種提高可靠性的設計方案,目前比較通用的方法就是進行冗余容錯設計。本文以某型車載信號系統預研為背景,利用雙口RAM接口電路簡單、數據交互量大、傳輸速度高等特點,設計了一種基于PowerPC和雙口RAM的冗余系統,并采用新穎的角色輪換和自檢技術,不僅保證了數據傳輸,而且也提高了系統的安全性。

1 系統總體交互方案

車載信號系統主要由主處理系統MPS、安全I/O設備GVIO(General Vital I/O)和外部設備組成。MPS主要通過GVIO進行數據收發,與外部設備進行通信,完成系統的狀態采集和控制功能。

GVIO作為通信接口模塊,支持多種接口與外部設備連接:通過RS-422與聯鎖設備連接;通過CAN接口與LKJ設備連接;通過RS-232與GPS信號連接;通過網口與無線傳輸模塊連接,并與軌旁控制系統進行通信;通過安全IO接口進行布爾量采集和輸出。

MPS和GVIO組成二取二的冗余系統架構,MPS由2個相同的處理模塊MCU1(1#CPU)和 MCU2(2#CPU)組成。MCU1和MCU2具有相關硬件和軟件,并且進行完全相同的邏輯運算處理,結構框圖如圖1。

GVIO主要從外部接收數據,并對2個MCU的數據進行一致性表決,表決通過后的數據,作為系統的最終輸出結果。

在MPS中,MCU1和MCU2包含微處理器MPC8248、RAM、Nor Flash、PCI控制器、雙口RAM;GVIO包含微處理器、RAM、PCI控制器和通信接口 (串口、CAN、以太網)。

MCU和GVIO分別與雙口RAM的兩端相連,GVIO系統通過PCI總線與雙口RAM連接,MCU系統通過local bus總線與雙口RAM連接,時鐘模塊分別與MCU系統、GVIO系統通過時鐘信號線相連。

圖1 系統模塊框圖

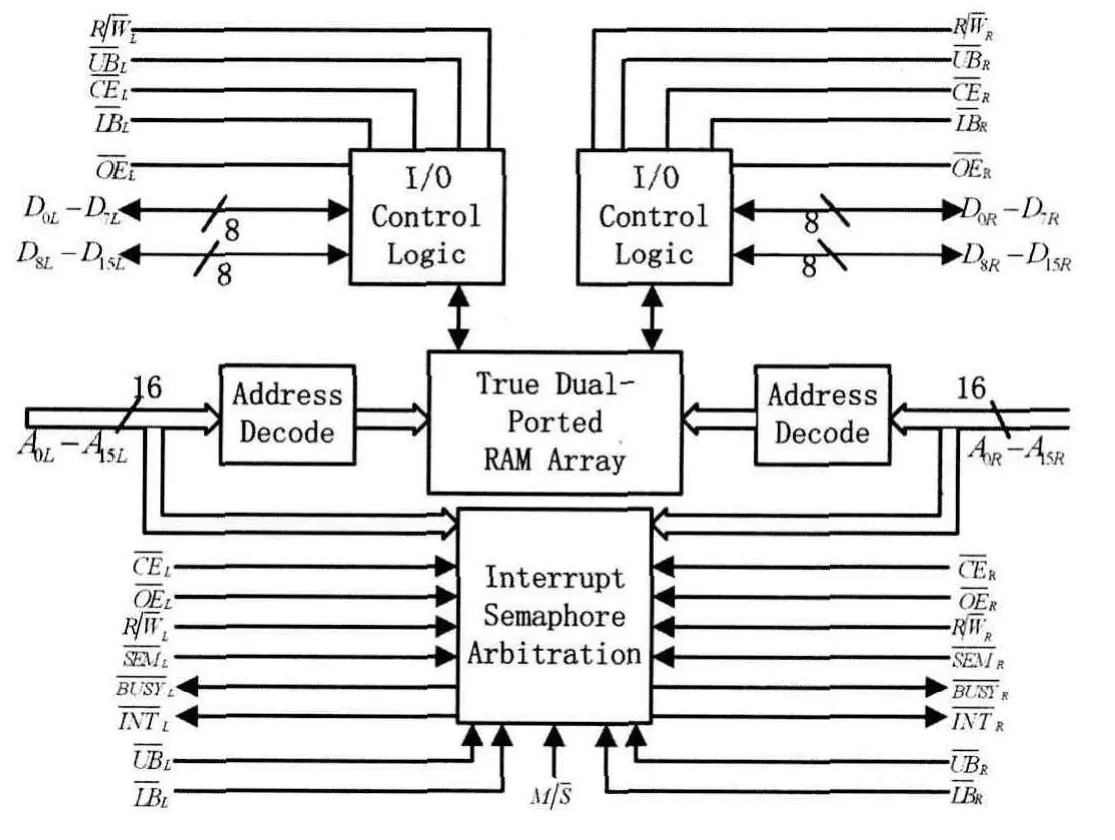

2 雙口RAM硬件結構

雙口RAM是雙端口SRAM芯片,本設計采用CY7C028V-15AXI,最高15 ns讀寫速度,數據容量為64K x 16 bit,雙口RAM具有2套完全獨立的數據線 (D0~D15)、地址線 (A0~A15)和控制信號線 (片選、讀、寫、中斷、忙等信號 )。CY7C028V-15AXI的邏輯模塊如圖2。

依據雙口RAM的工作原理,其兩端的CPU共享一個存儲器空間,允許MCU(MCU1/MCU2)和GVIO同時訪問雙口RAM中相異的數據存儲單元,可以快速交換數據,但是出現以下2種情況時,雙端口存取可能會出現沖突問題:①MCU和GVIO同時向同一地址單元寫入數據;②MCU和GVIO同時對同一個地址單元進行操作,MCU寫入數據,GVIO讀出數據,或者MCU讀出數據,GVIO寫入數據。

MPS和外部設備之間傳遞的通信數據,大部分都是安全相關數據,這些數據的可靠性極其重要,如果發生數據異常,可能引起難以預料的結果。

圖2 雙口RAM邏輯模塊框圖

3 數據通信方案

3.1 系統處理流程

MPS主要負責系統的邏輯處理與控制,GVIO主要負責數據的接收和發送,MPS和GVIO通過雙口RAM進行數據交互,整個系統處理流程如下:

1.GVIO通過 RS-232、RS-422、CAN、以太網等接口,接收外部設備發送過來的數據,并通過I/O接口采集相應設備的布爾量數據。

2.GVIO將接收到的數據,各拷貝一份相同的數據,寫入到雙口RAM中,傳遞給MCU。

3.MCU1/MCU2從雙口RAM讀出數據,并進行邏輯運算處理。

4.MCU1/MCU2將處理后的輸出數據放入雙口RAM。

5.GVIO分別從雙口RAM讀出MCU1和MCU2寫入的數據,通過 Safety-Coding-Arbitration進行數據一致性處理,將處理后的數據發送給對應的外部設備。

3.2 數據交換條件

MPS和GVIO進行數據交換的操作比較頻繁,而且數據交互過程需要滿足安全性、實時性和可靠性等要求。因此,MPS和GVIO雙口RAM進行數據通信時,必須滿足以下3個條件:①避免MCU和GVIO發生訪問沖突;②提高MCU和GVIO數據交互速度,不影響設備的數據通信量;③保證交互數據的完整性、正確性、可靠性。

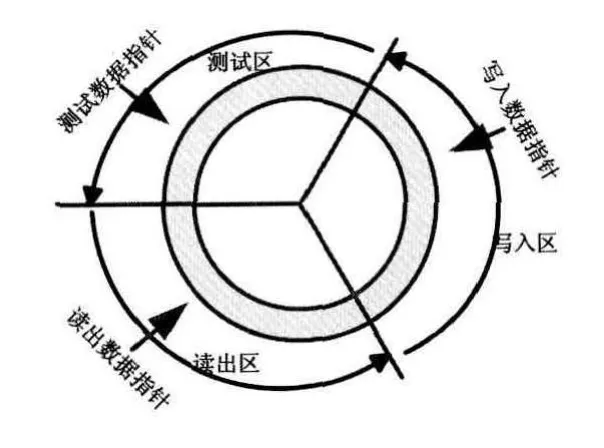

為了滿足條件①,避免MCU和GVIO同時對雙口RAM的同一個內存單元進行訪問,本設計沒有采用雙口RAM的中斷或者信號量等機制,而是采用了一種環形緩沖收發機制,將128KB的雙口RAM劃分為2個獨立環形緩沖區:發送環形緩沖區 (63KB)和接收環形緩沖區 (63KB)。

發送環形緩沖區負責將MCU傳遞給GVIO,最終發送給外部設備;環形緩沖區從GVIO接收到數據,并傳遞給MCU。環形緩沖區如圖3所示。

圖3 環形緩沖區示意圖

發送、接收環形緩沖區都再分為寫入、讀出和測試3個區塊,每個區塊的大小都為21KB。

MCU與GVIO通過相同的外部時鐘中斷來驅動數據處理軟件模塊的運行,MCU與GVIO在對雙口RAM進行訪問時可以做到同步、流水線作業。

在同一個處理周期內,發送或者接收環形緩沖區中任何一個區塊,都有明確固定的角色,MPU板和HCU板不會同時訪問操作相同區塊,只有一個板卡對特定區塊進行訪問,避免了雙口RAM的訪問沖突問題。

MPS的運行周期為600 ms,MPS按照周期進行數據接收、處理和輸出。其中,用于數據處理的時間為300 ms,MPS接收、發送數據超過300 ms,也會影響邏輯處理功能。在接收發送處理階段,300 ms中的280 ms被分為20個發送接收子周期,每一個子周期的時間為14 ms。

讀寫雙口RAM的數據速率為1 KB/ms,寫入區塊或者讀出區塊,有效交互時間280 ms內,可以交互高達280KB的數據,可以滿足系統的數據通信量。因此,通過該設計可以滿足條件②。

為了滿足條件③,保證在雙口RAM中傳輸數據的安全性和可靠性,采取2種安全數據處理措施:第一,通過Safety-Coding-Arbitration原理進行數據一致性處理;第二,對雙口RAM進行自檢,降低雙口RAM的硬件失效和功能性故障的風險。

3.3 安全數據處理措施

3.3.1 數據一致性處理

Safety-Coding-Arbitration處理過程如下。

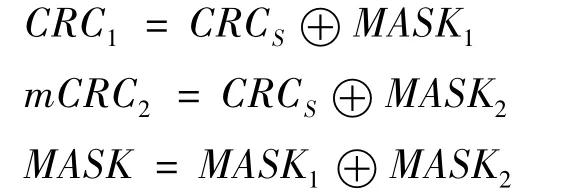

1.MCU1將要發送的數據Data1的CRCS進行掩碼處理 (mData1),MCU2也對要發送的數據Data2的CRCS進行掩碼處理 (mData2)。

2.GVIO從雙口RAM讀出經過掩碼數據mData1和mData2,對mData1和mData2進行一致性比較和合并處理。

CRCd=mCRC1⊕mCRC2⊕MASK

3.如果CRCS等于CRCd,則表示從MCU1和MCU2傳輸過來的數據是一致的,可以進行合并后輸出,否則丟棄。

3.3.2 對雙口RAM自檢

應用存儲器檢測算法對雙口RAM存儲功能性故障進行檢測和診斷,能夠及時發現和定位雙口RAM的功能故障和硬件失效。檢測步驟如下。

圖4 數據交互流程圖

其中,存儲器模塊M,有n個存儲器陣列單元Ui;表示單元的狀態處于狀態值ν,其中ν∈{0,1},∈{0,1},i=1…n;表示單元的寫入狀態值ν;表示從單元的讀出狀態的狀態值為ν;▽D表示單元地址按降序變化;i△Di表示單元地址按升序變化。

以上的多種措施,可以提高雙口RAM數據交互的速度,也可以保證數據交互的安全性和可靠性。

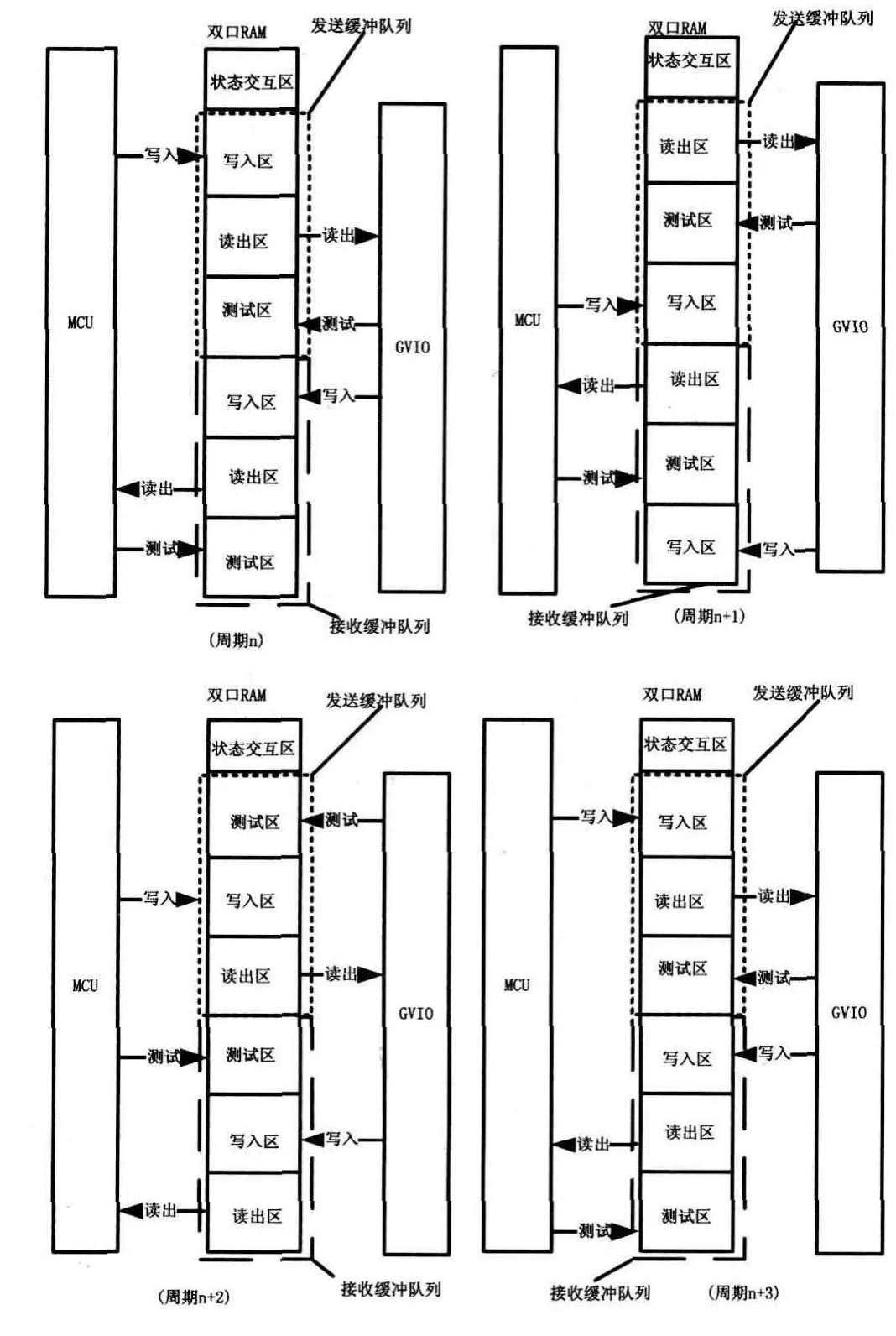

3.4 軟件設計

通過相應的軟件設計及周期性步驟,可以實現冗余系統的安全通信方案,周期性步驟如下。

1.讀出區塊內容是否讀完,如果讀完,將該區塊設置的標志變換為測試區塊,下個周期對該區塊進行測試。

2.寫入區塊內容是否寫完,如果寫完,將該區塊設置的標志變換為讀出區塊,下個周期對該區塊進行讀出。

3.測試區塊內容是否測試完,如果測試完,將該區塊設置的標志變換為寫入區塊,下個周期可以對該區塊進行寫入。

4.對測試區塊進行檢測,是否發現硬件隨機失效,若有,在狀態交互區中進行記錄狀態和告警信息。

在同一個周期,MCU和GVIO操作不同的區塊;通過周期輪轉,各個區塊進行角色輪換,如圖4所示。

4 結束語

分析冗余系統應用雙口RAM的性能和安全性要求,提出了多種措施來保證數據交互的實時性、安全性和可靠性,并在實際項目中應用,取得了良好的效果。

[1] 姜平,周榮根,肖紅升,等.基于雙口RAM的多機數據通信技術[J].儀表技術與傳感器,2005,15:105-107.

[2] 張遵偉,曹寶香,聶勝偉.基于雙口RAM的冗余架構同步技術研究[J].計算機工程,2012,38(18):221-224.

[3] 李震.一種基于雙口RAM的環形數據緩存系統[J].計算機技術與發展,2010,20(1):201-204.