低功耗恒定帶寬可編程增益放大器的設計

趙亮

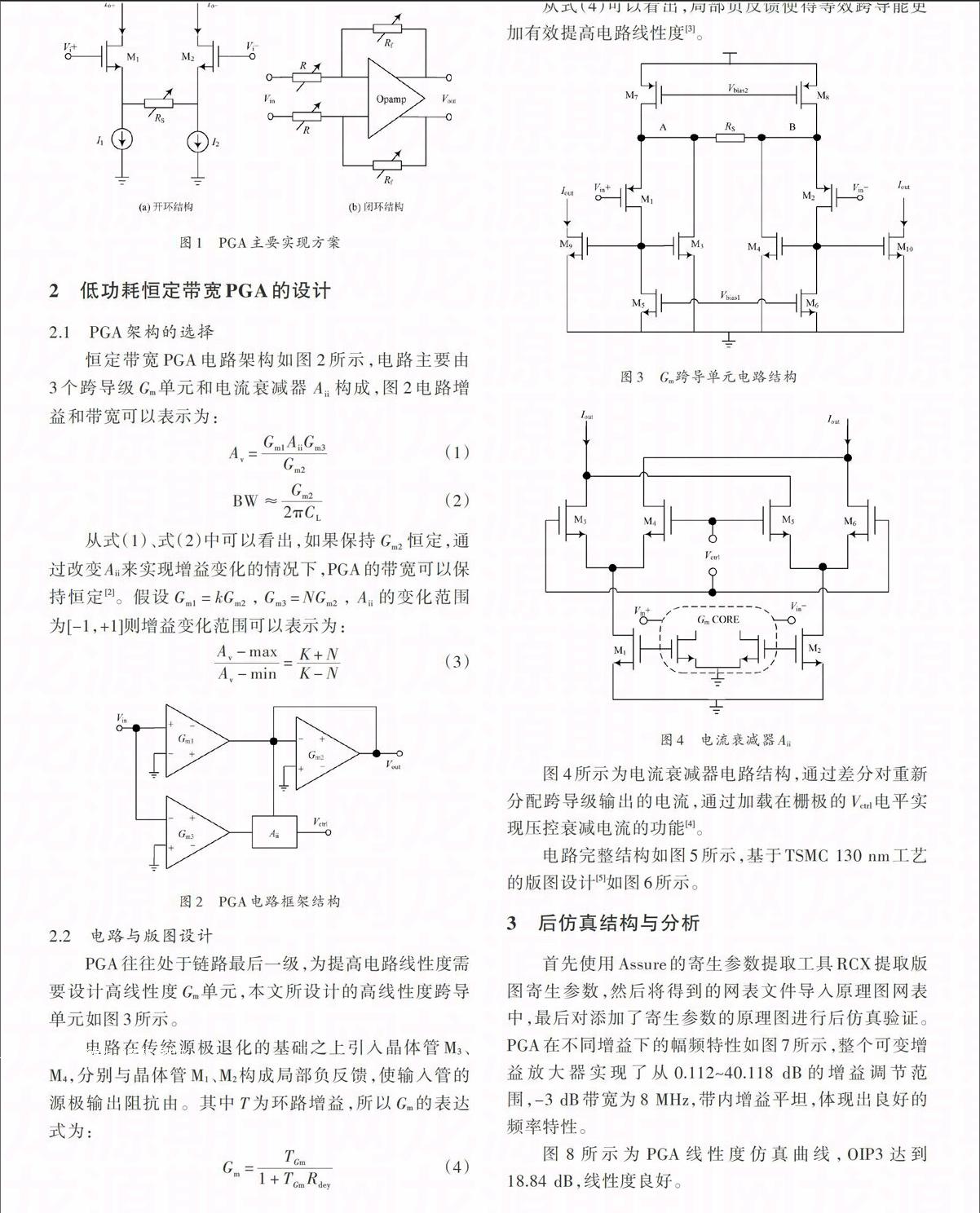

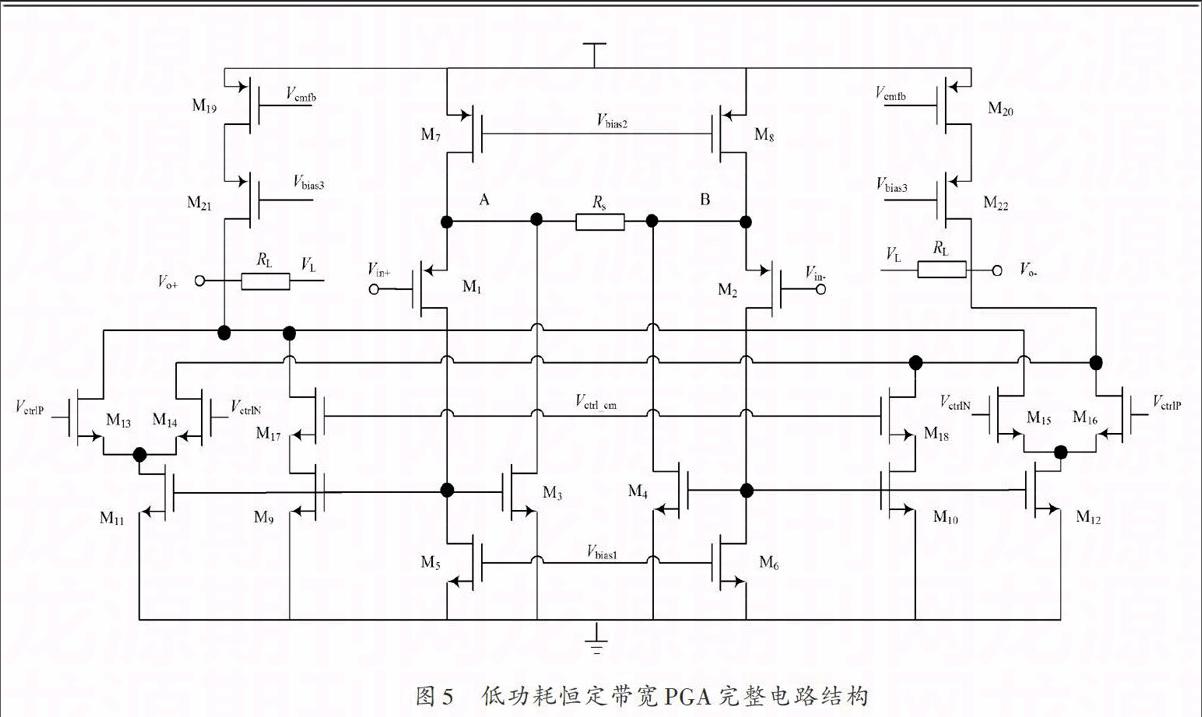

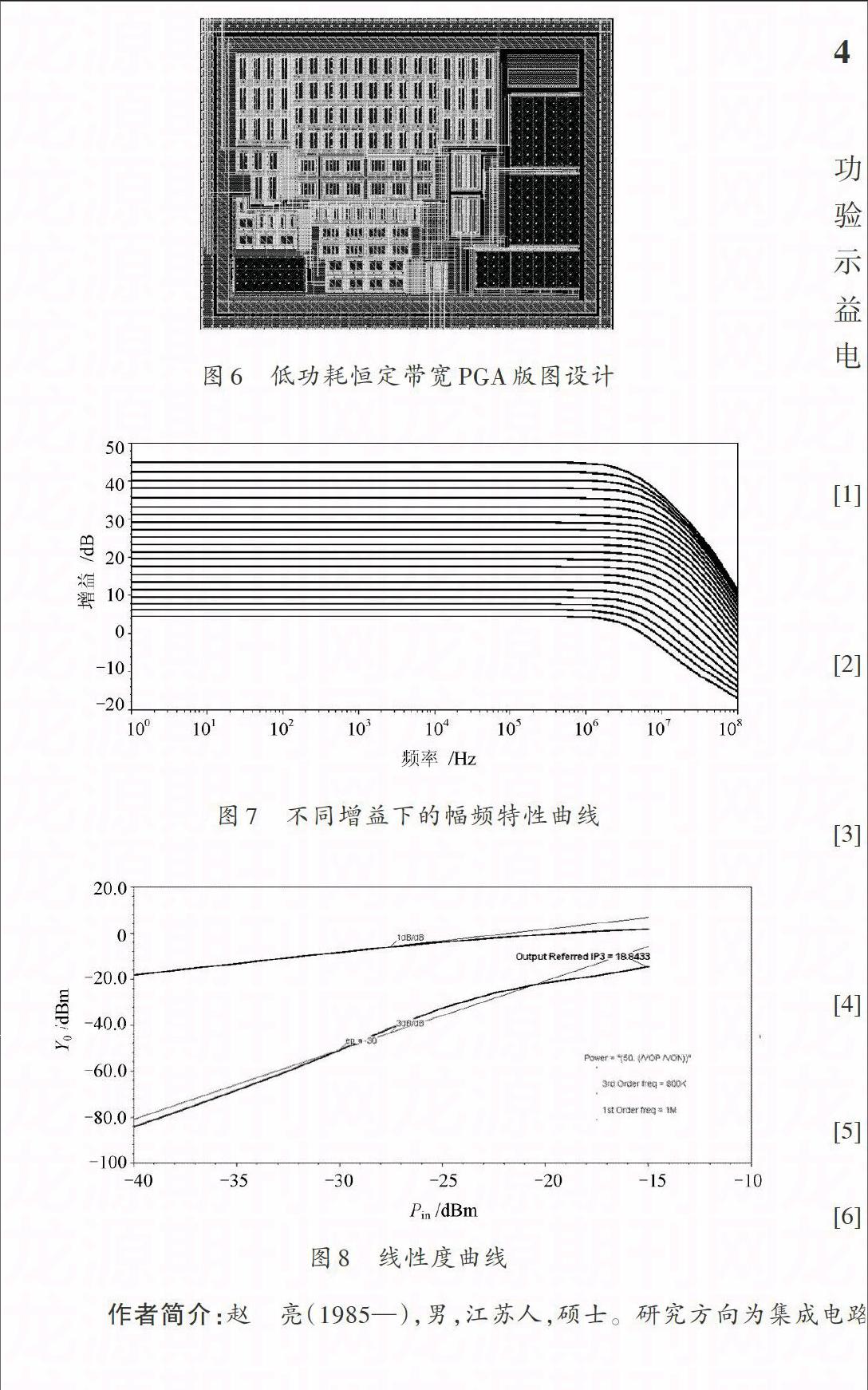

摘 要: 隨著無線智能終端功能的不斷豐富,可穿戴設備、無線傳感器網絡、無線手持終端等得到了快速發展,如何降低射頻收發機的功耗成為了越來越突出的問題。作為射頻收發機重要模塊的可變增益放大器,其電路設計的好壞往往直接決定了射頻接收機的總體性能,在此研究并設計一種低功耗恒定帶寬可編程增益放大器,該可編程增益放大器主要由2個Gm跨導單元、壓控電流衰減器以及電阻陣列構成。采用兩個高線性度Gm跨導單元有效減小芯片面積和功耗,并且增益變化不會導致帶寬變化。在TSMC 130 nm CMOS工藝下進行了后仿真驗證,實驗結果顯示該可編程增益放大器在1.2 V電源電壓下以400 μA的電流消耗實現了增益調節范圍0~40 dB,增益連續調節,線性度OIP3為18.84 dB,性能良好。

關鍵詞: 可編程增益放大器; 恒定帶寬; 低功耗; 射頻收發機

中圖分類號: TN710?34 文獻標識碼: A 文章編號: 1004?373X(2015)12?0126?03

0 引 言

可變增益放大器(VGA)作為一個重要的模擬電路模塊,在醫療設備、無線通信設備、助聽設備以及磁盤驅動等設備中有著廣泛應用[1]。可變增益放大器根據增益控制信號為模擬信號還是數字信號,可以分為模擬信號控制的可變增益放大器和數字可編程增益放大器(PGA)。隨著現代集成電路的發展,越來越注重于依靠數字電路高集成度、低功耗的特點來輔助設計模擬電路,所以PGA逐漸成為了可變增益放大器的主流研究方向。本文在介紹可變增益放大器工作原理的基礎之上,基于TSMC 130 nm CMOS工藝設計了一種低功耗可變增益放大器,并提取寄生參數進行了后仿真驗證,結果顯示該PGA在1.2 V電源電壓下消耗400 μA電流,實現增益調節范圍為0~40 dB,增益連續,線性度OIP3為18.84 dB,性能良好。

4 結 語

本文基于TSMC 130 nm CMOS工藝設計了一種低功耗恒定帶寬PGA電路,并進行了版圖設計和后仿真驗證,充分考慮了實際流片后存在的寄生問題,結果顯示本文所設計的可變增益放大器實現了0~40 dB的增益調節范圍,線性度良好,OIP3達到18.84 dB,在1.2 V電源電壓下,電流消耗僅為400 μA。

參考文獻

[1] CHEN Z, ZHENG Y, CHOONG F C, et al. A low?power variable?gain amplifier with improved linearity: analysis and design [J]. IEEE Transactions on Circuits and Systems I , 2012, 59(10): 2176?2185.

[2] ONET R, NEAG M, KOVACS I, et al. Compact Variable Gain Amplifier for a multistandard WLAN/WiMAX/LTE receiver [J]. IEEE Transactions on Circuits and Systems I, 2014, 61(1):247?257.

[3] MOSTAFA M A I, EMBABI S H K, ELMALA M. A 60 dB 246 MHz CMOS variable gain amplifier for subsampling GSM receivers [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2003, 11(5): 535?538.

[4] GUO Chun?bing, LUONG H C. A 70 MHz 70 dB?gain VGA with automatic continuous?time offset cancellation [J/OL]. [2009?09?25].http:// www. bbs.eetop.cn/threa...1?1.html.

[5] SAINT C, SAINT J.集成電路掩模設計:基礎版圖技術[M].北京:清華大學出版社,2006.

[6] 劉豐華.低噪聲放大器的兩種設計方法[J].現代電子技術,2011,34(4):129?131.