基于FPGA的視頻與通訊數據融合設計

韓紅霞,孫 航,張海波

(中國科學院長春光學精密機械與物理研究所,吉林長春130033)

基于FPGA的視頻與通訊數據融合設計

韓紅霞?,孫 航,張海波

(中國科學院長春光學精密機械與物理研究所,吉林長春130033)

為實現將時間值、方位值等串口通訊信息疊加進數字視頻圖像信號的某一固定行中,設計了基于FPGA的通訊數據與數字視頻數據的融合系統.采用FPGA程序設計實現串行數據接收與內置FIFO處理,并提取視頻數據的某一固定行,進行數據融合,使得通訊數據和視頻數據在場信號有效下組合輸出.基于FPGA的通訊數據與數字視頻數據的融合系統實現了通訊數據與視頻數據的融合,試驗中通訊數據波特率為230.4 kbit/s,視頻信號幀頻50 Hz,視頻數據與通訊數據幀頻相同,圖像像素為1 024×1 024,通訊數據正確的融合入一場圖像的最后一行中,系統工作穩定,工作狀態良好.基于FPGA的通訊數據與數字視頻數據的融合系統以最簡硬件系統實現了通訊數據與數字視頻數據的組合輸出,滿足圖像處理及顯示系統的要求,具有廣泛的工程意義.

視頻數據;通訊數據;融合;FPGA

1 引 言

針對圖像處理及圖像顯示等系統的要求,需要將通訊數據疊加進數字視頻信息的某一固定行中,設計基于FPGA的通訊數據與視頻數據融合系統.采用FPGA編程實現時間、角度值等通訊信息到視頻信息的疊加,疊加信息可以在一場圖像中指定的任意一行輸出,提供給后續的圖像處理、圖像顯示等系統.對通訊數據的接收以及通訊數據到視頻數據的融合完全采用基于FPGA的Verilog語言編程結合圖形編程實現,在FPGA內部構建通訊數據波特率匹配模塊、串行數據的接收模塊、行同步信號提取模塊以及通訊數據與視頻數據組合模塊等,實現通訊數據到視頻數據的融合功能.通訊數據到視頻數據的融合系統設計實現了需要的通訊信息到視頻數據的疊加顯示等功能,試驗證明:系統工作穩定,狀態良好[1-3].

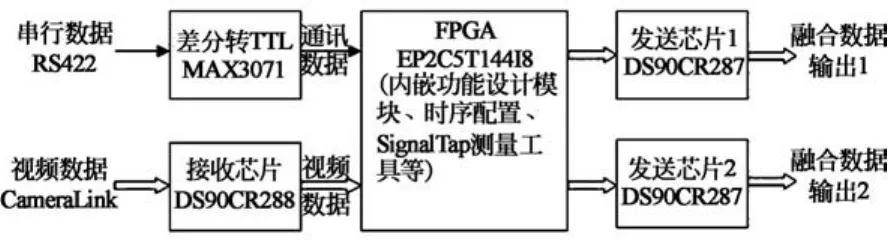

2 硬件設計

基于FPGA的通訊數據與視頻數據融合設計在硬件設計中包括:串行數據輸入、數字視頻數據輸入、FPGA及外圍電路、通訊與視頻數據融合輸出等部分,如圖1所示.

圖1 通訊數據與視頻數據融合硬件結構示意圖Fig.1 Hardware structure diagram of communication data and video data composition system

串行輸入數據是RS422格式,經差分轉TTL芯片MAX3071得到LVTTL格式信號,數字視頻輸入信號為Camera_Link格式,經Camera_ Link接收芯片DS90CR288得到并行的LVTTL信號,經轉換的通訊數據和視頻數據分別輸入FPGA,FPGA接收串行數據并將其融合入數字視頻信號的某一指定行中,實現通訊數據與視頻數據的融合,融合數據經Camera_Link發送芯片DS90CR287轉換為Camera_Link標準數據,進行輸出.

通訊數據與視頻數據融合設計的核心是FPGA,FPGA進行邏輯控制和時序配置,同時采用Verilog語言編程結合內嵌功能模塊以及Signal-Tap工具,可以實現各種邏輯及時序功能設計. FPGA通過為每個功能建立單獨的硬件來實現整個應用程序所需要的邏輯功能,因此具有并行處理的內在特點,程序速度快、運行靈活,并且FPGA內部采用流水結構,因此非常適合進行圖像及邏輯方面的相關設計.

通過對FPGA的編程實現了串行數據的接收、串行數據與視頻數據的融合以及所有外圍芯片的邏輯控制.FPGA內部主要包括4個功能模塊,分別是波特率產生模塊、串行數據接收模塊、行同步信號處理模塊和數據處理及融合模塊,其中波特率產生模塊,是根據已知的接收數據波特率,處理外部時鐘信號,產生與波特率相對應的數據接收時鐘信號[4-5];串行數據接收模塊負責按位接收串行通訊數據,并將有效位數據并行化;行同步信號處理模塊負責根據需要提取需要擬合通訊數據的行,或者在行消隱期做出可以擬合通訊數據的行信號,這部分根據工程設計的實際需要,本設計中根據要求將通訊數據擬合進一場數據中的最后一行;數據處理及融合模塊負責將視頻數據和通訊數據進行組合輸出,按時序要求提供給后續圖像處理、存儲等系統.

3 FPGA程序設計

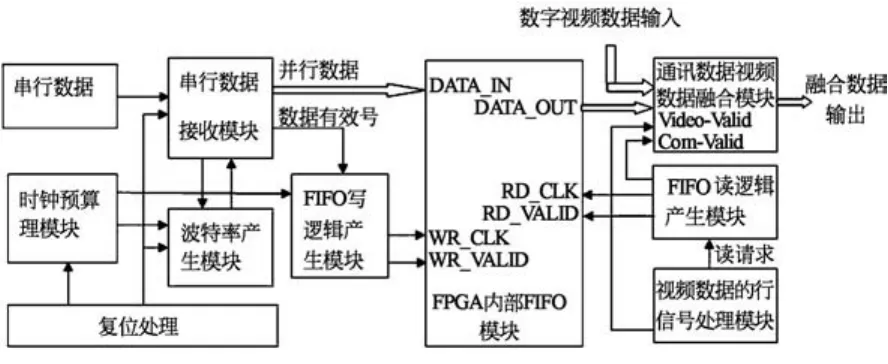

對FPGA編程主要采用Verilog語言結合內嵌功能模塊以及內部集成的Signal Tap測量工具實現,主要包括波特率產生模塊、串行數據接收模塊、行信號處理模塊以及通訊數據與視頻數據融合模塊等.圖2給出基于FPGA的通訊數據與視頻數據融合程序設計框圖.

如圖2所示,串行數據輸入后,FPGA首先要根據串行數據的波特率產生與輸入數據相匹配的接收時鐘,即由波特率產生模塊產生能夠采到每一位數據的有效時鐘信號.接著串行數據接收模塊根據波特率產生模塊提供的有效時鐘信號按位接收數據,將串行數據轉換為并行數據,并產生與每一個字節對應的數據有效信號[6-8].FIFO寫邏輯產生模塊根據串行數據接收模塊提供的數據有效信號以及時鐘預處理模塊提供的時鐘信號產生FIFO的寫時鐘信號WR_CLK和FIFO的寫有效信號WR_VALID.以上模塊均是對串行接收數據進行處理,接下來對數字視頻信號進行處理,以達到通訊數據與視頻數據融合的目的.視頻數據的行信號處理模塊負責從場信號包含的若干行信號中提取要發送通訊數據的行信號,并將這個行信號提供給FIFO讀邏輯產生模塊.讀邏輯產生模塊根據視頻信號的像素時鐘和行信號處理模塊提供的讀請求信號產生FIFO的讀時鐘信號RD_CLK和讀有效信號RD_VALID.FIFO根據讀寫邏輯,對并行化的串口接收數據進行緩存后輸出,得到與視頻數據時序相同的信號.最后通訊數據與視頻數據融合模塊在Video_Valid有效時輸出視頻信號,在Com_Valid有效時輸出通訊信號,并將兩者進行時序和數據的整合,得到一場既包含視頻信號又包含通訊信號的融合數據輸出[9-10].

圖2 FPGA實現通訊數據與視頻數據融合框圖Fig.2 FPGA design diagram of communication data and video data composition system

4 實 驗

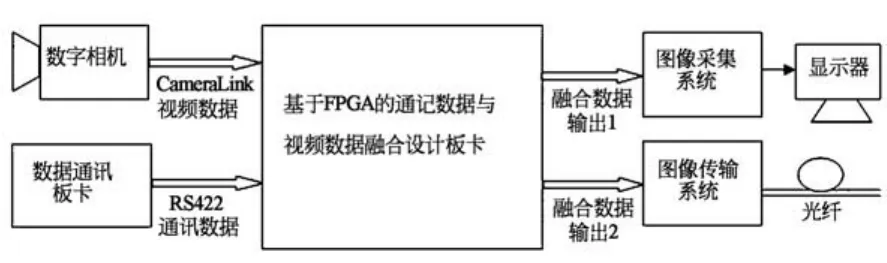

基于FPGA的通訊數據與視頻數據融合設計實驗中,采用1M30數字相機作為數字視頻輸出信號源,數據通訊板作為通訊數據的輸出信號源,圖3給出實驗結構圖.

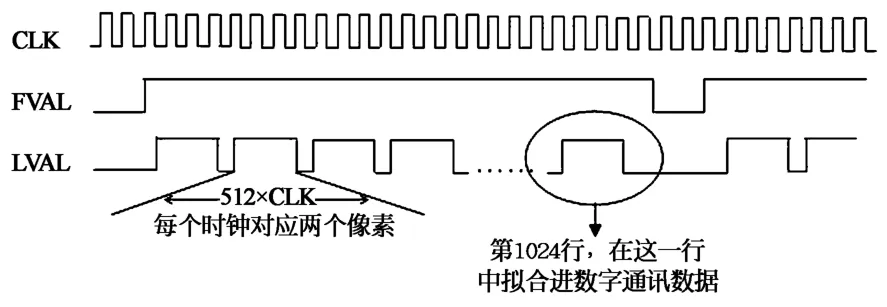

如圖3所示,實驗中,1M30相機作為視頻數據源為通訊數據與視頻數據融合設計板卡提供CameraLink格式的數字視頻信號,數據通訊板作為通訊數據源為通訊數據與視頻數據融合設計板卡提供RS422格式的通訊數據.基于FPGA的通訊數據與視頻數據融合設計板卡將輸入的視頻數據與通訊數據進行融合,得到將通訊數據擬合入視頻數據某一固定行中的融合輸出數據,分別輸出給圖像采集系統和圖像傳輸系統.實驗中視頻數據像素幀頻為50 Hz,像素時鐘為40 MHz,像元尺寸1 024×1 024,每個像素時鐘對應兩個12位的數據,將通訊數據擬合入視頻數據的最后一行,時序如圖4所示.

圖3 基于FPGA的通訊數據與視頻數據融合設計實驗結構圖Fig.3 Experiment diagram of the communication data and video data composition system

圖4 視頻數據時序簡圖Fig.4 Time sequence diagram of the video data

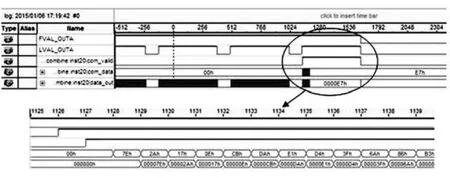

如圖4所示,視頻輸出信號的時序測量顯示場同步信號FVAL有效電平下包括1 024個行信號LVAL,行信號有效包括512個時鐘信號,而每個時鐘信號對應24位的數據輸出,表示兩個12位的像素值,因此一場圖像為1 024×1 024×12 bit,按照要求需要將通訊系統發送的數據擬合進一場圖像的最后一行中,基于FPGA的通訊數據與視頻數據融合設計實現了這一功能,圖5給出采用FPGA內嵌的Signal Tap工具進行測量,得到的數據擬合觀測圖.

如圖5所示,Signal Tap觀測圖顯示,輸出的場同步信號和行同步信號與原視頻輸入的場同步信號和行同步信號一致.在融合數據的最后一行,是通訊板發送的通訊數據,已知通訊板發送來的數據是以7E開頭E7結尾的一幀數據,波特率為230.4 kbit/s,圖5中顯示最后一行數據是融合的通訊數據,由于每個時鐘對應的視頻數據為24位,為與其保持一致,將通訊數據擴展為24位數據,可以看出融合的通訊數據與原通訊數據一致.圖像采集系統對融合數據進行了數據采集并顯示,圖6給出采集圖像顯示圖.

圖5 擬合數據Signal Tap觀測圖Fig.5 Composition data collected by the SignalTap tool

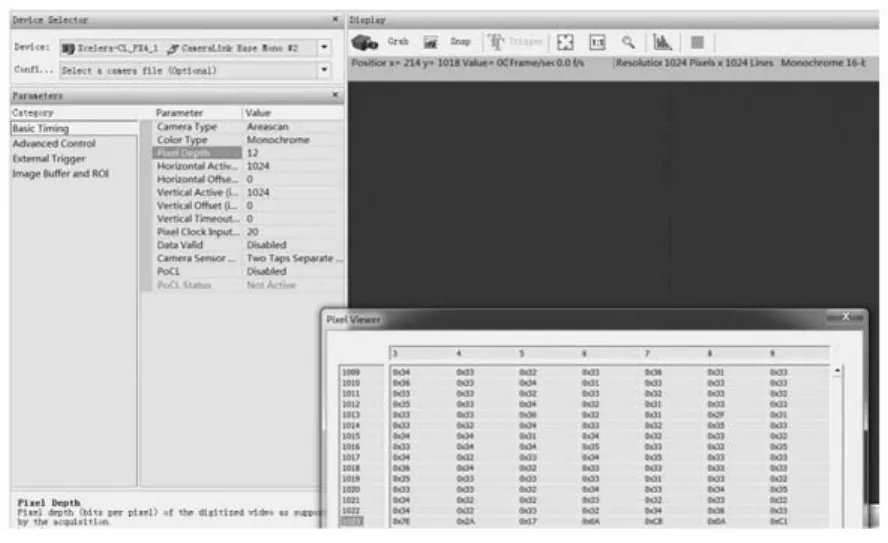

圖6 圖像采集及像素顯示示意圖Fig.6 Collected image and pixel value display diagram

圖6給出圖像采集示意圖,用PIXELVIEW工具可以看到指定區域的像素值,從圖中可以看出一場圖像的最后一行即圖中顯示的第1 023行的像素值是7E開頭E7結尾的通訊擬合數據.圖中對像素值的顯示說明:基于FPGA的通訊數據與視頻數據融合系統設計實現了視頻數據與通訊數據的融合,擬合的數據正確,系統工作穩定.

5 結 論

基于FPGA的通訊數據與視頻數據融合系統設計實現了將通訊數據擬合進視頻數據某一固定行中的功能,實驗中視頻數據為像素時鐘40 MHz,像元尺寸1 024×1 024,數據位12 bit的Camera_Link格式數據,通訊數據為7E開頭E7結尾的隨機數,實驗證明板卡實現了通訊數據到視頻數據的融合,融合進視頻數據最后一行的通訊數據完整、正確,滿足圖像采集系統、圖像顯示系統等后續系統的需求.目前板卡已應用于具體的工作項目中,工作穩定,性能良好.基于FPGA的通訊數據與視頻數據融合系統設計成功的將角度信息、時間信息等通訊數據擬合進視頻數據中,方便的數據的處理和顯示,具有廣泛的工程應用意義.

[1] 熊文彬,蔣泉,曲建軍,等.基于FPGA實現的視頻顯示系統[J].液晶與顯示,2011,26(1):92-93.

Xiong W B,Jiang Q,Qu J J,et al.Video display system based on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2011,26(1):92-93.(in Chinese)

[2] Levine P A,Saucer D J,Shallcross F V.High frame rata multi-port CCD image and camera[J].SPIE,1992,1952:257-267.

[3] Li X Z,Yu Z Y,Shang F.Multifunction image target generator[J].Experimental Technology and Management,2002,19(4):36-37.

[4] 王明富,楊世洪,吳欽章.大面陣CCD圖像實時顯示系統的設計[J].光學精密工程,2010,18(9):2053-2059.

Wang M F,Yang S H,Wu Q Z.Design of large-array CCD real time display system[J].Optics and Precision Engineering,2010,18(9):2053-2059.(in Chinese)

[5] 穆欣,胡君,宋啟昌,等.空間相機集成測試系統的時鐘同步[J].光學精密工程,2010,18(6):1436-1443.

Mu X,Hu J,Song Q C,et,al.Time synchronization of integrated testing system of space camera[J].Optics and Precision Engineering,2010,18(6):1436-1443.(in Chinese)

[6] 郭敬明,魏仲慧,何昕,等.CCD星圖模擬器的設計及驗證[J].中國光學與應用光學,2010,10(3):486-493.

Guo J M,Wei Z H,He X,et al.Design of CCD starmap simulator and its validation[J].Chinese Journal of Optics and Applied Optics,2010.10(3):486-493.(in Chinese)

[7] 劉妍妍,張新,張建萍.超分辨重建技術及其研究進展[J].中國光學與應用光學,2009,4(2):102-111.Liu Y Y,Zhang X,Zhang J P.Super resolved reconstruction technologies and recent evolution[J].Chinese Journal of Optics and Applied Optics,2009,4(2):102-111.(in Chinese)

[8] 陳娟,陳乾輝,師路歡,等.圖像跟蹤中的邊緣檢測技術[J].中國光學與應用光學,2009,2(2):46-53.

Chen J,Chen Q H,Shi L H,et al.Edge detection technology in imaging tracking[J].Chinese Journal of Optics and Applied Optics,2009,2(2):46-53.(in Chinese)

[9] 胡君,王棟,孫天宇.現代航天光學成像遙感器的應用與發展[J].中國光學與應用光學,2010,12(3):519-533.

Hu J,Wang D,Sun T Y.Application and development of recent space optical imaging remote sensors[J].Chinese Journal of Optics and Applied Optics,2010.12(3):519-533.(in Chinese)

[10] 楊為錦,孫強.中波紅外連續變焦系統設計[J].中國光學與應用光學,2010,4(3):164-169.

Yang W J,Sun Q.Design of middle infrared continuous zoom system[J].Chinese Journal of Optics and Applied Optics,2010,4(3):164-169.(in Chinese)

Composition design of communication data and video data based on FPGA

HAN Hong-xia?,SUN Hang,ZHANG Hai-bo

(Changchun Institute of Optics,Fine Mechanics and Physics,Chinese Acadeny of Sciences,Changchun 130033,China)

To realize the composition of the serial port information such as time and azimuth value on the fixed line of the digital video signal,the communication data and digital video signal composition system has been designed.Based on FPGA,the serial port data is received and processed by the FIFO module,and a fixed line signal is extracted.The communication data and video signal composition is realized,and the composition data is output under the frame valid signal.The communication data and digital video signal composition system based on FPGA realized the data composition function.In the experiment,the baud rate of the communication data is 230.4 kbit/s,frame rate of the video signal is 50 Hz,pixel size is 1 024×1 024,the communication data is composed in the last line of one frame video signal correctly,the system works stably and the work status is good.The communication data and digital video signal composition system based on FPGA realizes the data composition in the simplest hardware system,meets the requirements of the image processing and display system,has broad engineer meaning.

video data;communication data;composition;FPGA

TP331

A doi:10.3788/YJYXS20153006.0987

1007-2780(2015)06-0987-05

韓紅霞(1979-),女,河北宣化人,博士,副研究員,主要從事光纖通信及FPGA設計等作.E-mail:71828@sina.com

2015-02-23;

2015-06-08.

?通信聯系人,E-mail:mail:71828@sina.com