綜合背板與線束在雷達系統中的應用

張成剛,張德斌

(南京電子技術研究所, 南京210039)

0 引言

陣面綜合布線是雷達系統中的重要組成部分,它的作用是實現微波信號、控制信號、電信號、光信號的正常傳輸。傳統的雷達綜合布線大多只采用線纜互連方式,陣面走線復雜,交織穿插,故障率高,抗電磁干擾性差,排故困難。

隨著雷達技術的發展,對陣面綜合布線的要求越來越高,現代雷達產品電子設備量大、集成度高、兼容性強、高頻箱走線空間狹小、設備以及走線之間的信號干擾強烈,各類電源電纜、控制電纜、射頻電纜種類繁多。為使綜合布線線路清晰、抗電磁干擾能力強,本文討論了綜合背板與綜合線束相結合,對雷達陣面系統進行一體化集中式設計,使得雷達陣面體系脈路分明,抗電磁干擾能力強[1],大幅度增強陣面的可維護性,并利用EDA軟件進行仿真優化[2],使得設計一步到位,保證雷達系統的高可靠性。

1 設計原理

現以雷達綜合布線為例,陣面由若干機柜組成,機柜內含有T/R組件、數字單元、二級開關、發射電源、接收電源、濾波器、除濕機等電子設備,機柜背板與高頻箱體之間的間距狹小,綜合布線要在此夾層中完成。控制電纜分為五種:T/R控制電纜、發射電源監控電纜、接收電源監控電纜、二級開關控制電纜、一分九開關控制電纜。電源電纜分為八種:T/R接收電源供電電纜、T/R發射電源電纜、數字單元供電電纜、濾波器交流電輸入電纜與輸出電纜、接收電源交流電輸入電纜、二級開關供電電纜、一分九開關供電電纜、除濕機供電電纜。

1)主要電源信號流向如圖1所示。

圖1 電源供電示意圖

接收電源將5 V模擬電與數字電送入綜合走線背板,然后,經過綜合走線背板分配給10組T/R組件、數字單元、二次行饋組件、二級開關、一分九開關等。

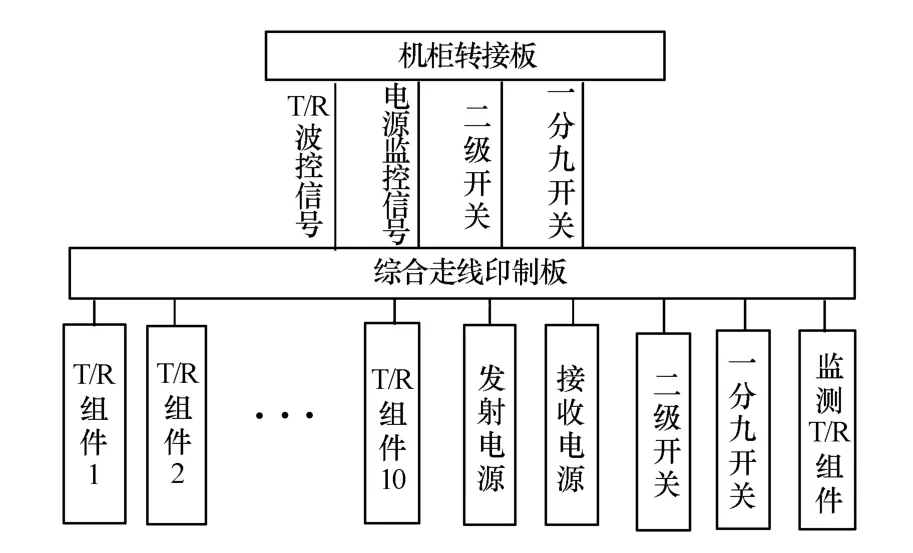

2)主要控制信號流向如圖2所示。

圖2 控制信號流向示意圖

T/R控制信號、發射電源監控信號、接收電源監控信號、二級開關控制信號、一分九開關控制信號經機柜轉接板送入綜合走線背板,然后,由綜合走線背板對相應設備進行控制。

2 綜合走線設計規則

2.1 電磁兼容

電磁兼容(EMC)[3]問題是一個非常重要的環節,并且貫穿設計流程的各個階段,綜合布線要考慮EMC,綜合背板與綜合線束的設計要符合EMC的要求。安全地、信號地、電源地要區分開來,否則,容易發生電磁干擾。

系統及各設備布線要求如下:(1)電線電纜布線設計,必須盡可能減少耦合;(2)對各種信號走線進行合理布局,對輸入的強弱信號要隔離;(3)盡量縮短各種引線,以減少干擾;(4)接地線,尤其是高頻電路接地線要短。

2.2 仿真技術

在設計綜合背板時,引入仿真技術,在設計前期對印制電路板(PCB)綜合板進行模擬分析,有針對性地加以改進,將很多的設計風險扼殺在萌芽狀態,從而能大大縮短設計周期和節省設計成本。

2.3 綜合線束的設計

1)控制電纜線束外面要套防波套,防波套要與連接器尾夾充分接觸,尾夾要接地且盡量選用扁平線纜接地。

2)如果控制電纜線束中含有干擾性強的信號導線,那么每條信號導線都需要外套防波套,線束里的每根導線屏蔽網最后引到一起接安全地。現在廠家會有現成的單根屏蔽線、雙絞屏蔽線可選。

3)控制電纜與電源電纜要分開走,防止發生干擾。電源電纜如果是由多根導線組成的線束,要考慮以下三點:線束中導線的根數、外界的溫度、所處的海拔高度。此三大因素會影響導線的載流量,線束里導線根數越多,外界溫度越高,海拔越高,導線的衰減系數越小,耐電流能力越小。

3 關鍵技術

3.1 綜合走線背板的設計

綜合走線背板長約1 m,寬6 cm,厚5.5 mm,該綜合板包含控制信號與電源供電信號[4]。L7、L8、L9、L10、L11、L12、L13 為信號層,TOP、BOTTOM、L6、L14層為安全地,L19 層為信號地,L2、L3、L4、L5、L15、L16、L17、L18 為電源層,銅皮厚度為0.2 mm。

機柜內電子設備需要數字電源和模擬電源,數字電源與模擬電源分開供給,以防止相互干擾,電源可分成四類:5 V/20 A(數字),5 V/30 A(數字),5 V/10 A(模擬),5 V/20 A(模擬)。電源層由于承載電流較大,銅層采用厚銅,厚為0.2 mm。

從EMC方面考慮:(1)信號層與電源層分別布在不同層中,減少相互之間干擾;(2)為防止外界與綜合走線板間的干擾,在背板四周均打上屏蔽孔,屏蔽孔與TOP、BOTTOM層的安全地連在一起,背板四周做側壁金屬化處理;(3)背板上電連接器結構固定孔金屬化,孔阻焊層要大于連接器固定螺釘帽,使得螺釘帽與TOP、BOTTOM層安全地充分接觸,從而與背板對插的控制信號電纜上的干擾信號通過防波套經電連接器殼體、背板安全地,最后經綜合走線背板流入機架安全地[5-6]。

從結構方面考慮,由于背板較長,電源層銅皮較厚,信號層、地層相對較薄,在安排疊層結構的時候,要注意電源層從上至下應對稱排布,以防止背板加工后由于張力原因發生翹曲。

3.2 綜合走線背板上控制信號分析與仿真驗證

隨著數字電路時鐘速度的提高,信號完整性(SI)已成為越來越關心的問題。當電路中信號能以要求的時序、持續時間和電壓幅度到達負載時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。誤觸發、阻尼振蕩、過沖、欠沖等信號完整性問題會造成時鐘間歇振蕩和數據出錯。在實際的PCB板上的導線具有電阻、電容和電感等電氣特性,驅動器的輸出阻抗通常小于PCB互聯信號線的特征阻抗,而PCB互聯信號線的特征阻抗一般來說也小于接收器的輸入阻抗。這種阻抗的不連續性就會導致設計系統中信號反射的出現。在高速數字電路設計中,PCB板線路上的電容和電感會使導線等效于一條傳輸線。傳輸線上的阻抗會使信號達不到規定的電壓幅度,線路阻抗與外接負載不匹配會產生信號反射現象,這些都會引起信號完整性問題。

一般來說,減少信號完整性問題的常用方法是在傳輸線上增加端接元件。端接元件是一些無源元件,如電阻和電容。終端匹配技術就是利用這些元件在傳輸線和負載間實現阻抗匹配從而防止產生SI問題[2]。電阻可以用來匹配傳輸線阻抗與接收器的阻抗,而電容則可以用來限制電壓的變化從而削弱阻尼信號的能量。

綜合走線背板在布控制信號時需要考慮SI[7],在終端位置加載匹配電阻。采用軟件進行仿真設計,得到最佳匹配電阻值。本設計使用CST PCB STUDIO對綜合走線背板控制信號進行仿真驗證。

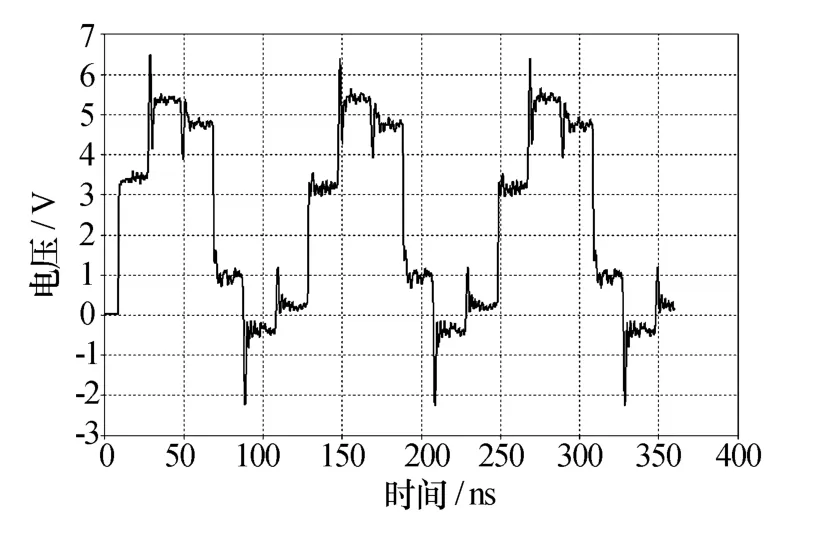

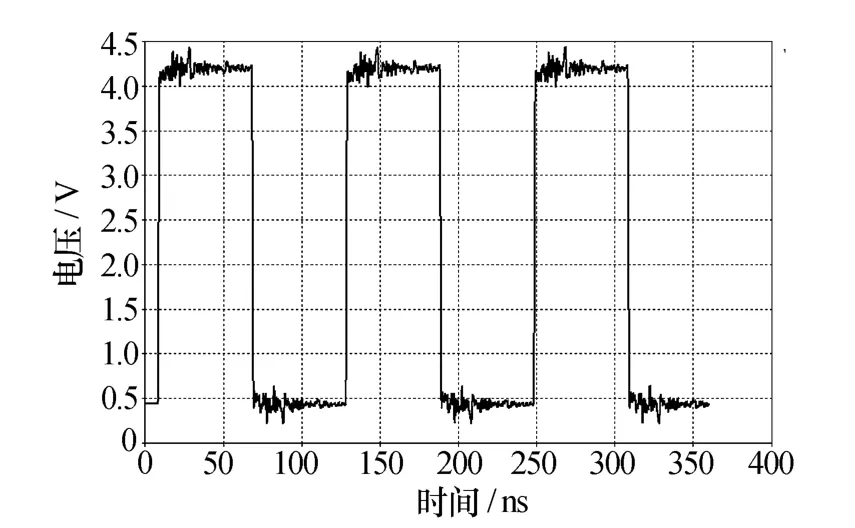

下面對綜合走線背板的一對差分對信號進行仿真分析,當終端不加匹配電阻時,負載信號波形如圖3所示。終端接匹配電阻,并對電阻值進行優化仿真,最后,選取最佳值100 Ω,負載信號波形最佳,如圖4所示。

通過仿真驗證,由圖3、圖4比較可以發現:終端匹配電阻對信號輸出波形起的作用極大,未加匹配電阻時,信號波形振蕩劇烈,信號反射現象嚴重;當加100 Ω匹配電阻時如圖4所示,信號平坦。

圖3 終端未接匹配電阻時負載端信號波形

圖4 終端接100 Ω匹配電阻時負載端信號波形

3.3 綜合走線背板上電源層分析與仿真驗證

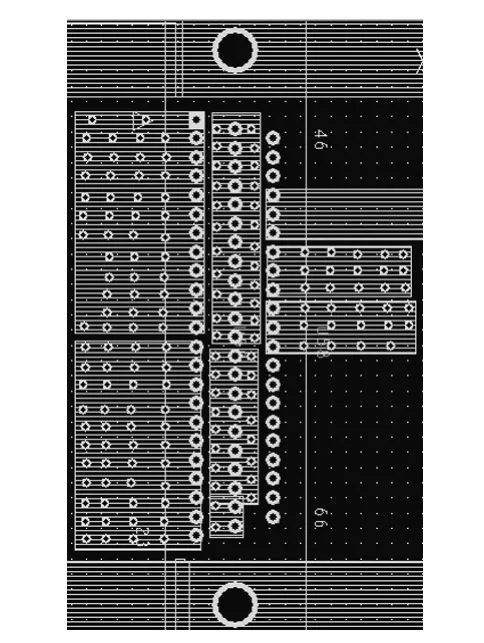

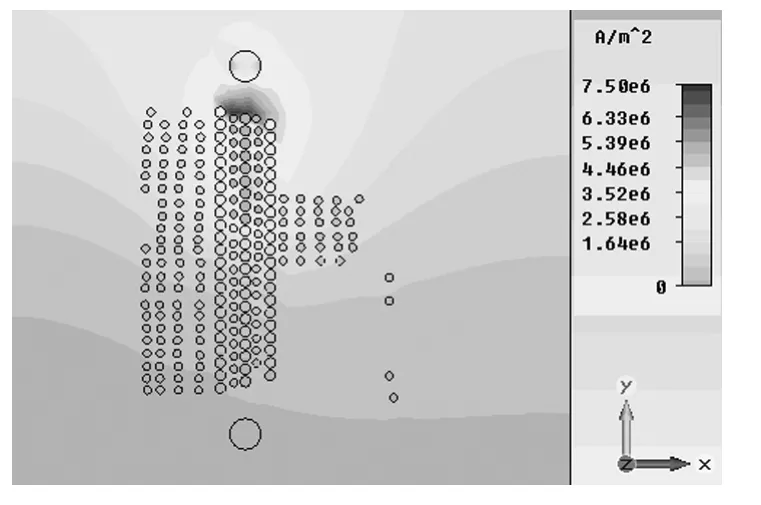

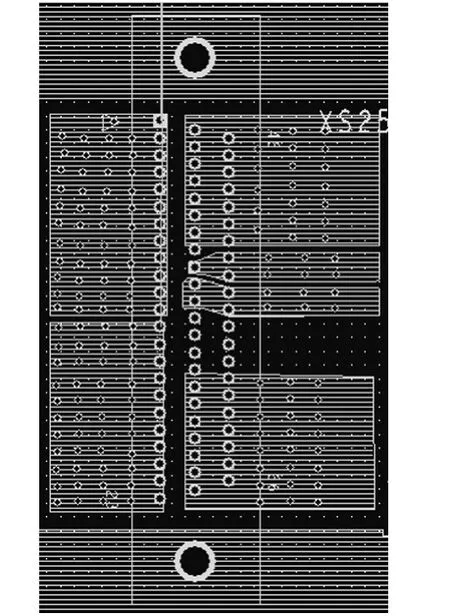

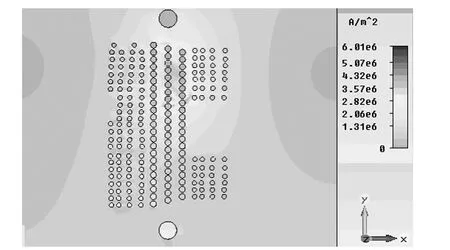

背板電源層走大電流時,經過理論計算電源層可走50 A的電流,輸入電流經過背板中部兩個J30J-66ZKN8P17-J電連接器進入背板電源層。在電流集中處需要進行分流處理,在J30J-66ZKN8P17-J電連接器旁邊打一些電流過孔,電流過孔一方面與電連接器對應管腳相連,另一方面與電源層相連,增加電流過孔目的是防止背板上對應的電連接器過孔由于電流過大而燒斷。最后,采用CST EM STUDIO軟件進行電流仿真驗證,觀察電流分布。J30J-66ZKN8P17-J電連接器輸入電流管腳排布未經優化時如圖5所示,對綜合走線背板進行仿真,該連接器附近電流密度分布如圖6所示;優化后的電連接器管腳排布如圖7所示,對綜合走線背板仿真分析,該連接器附近電流密度如圖8所示。

圖5 優化前連接器管腳排布

圖6 優化前連接器電流密度分布

圖7 優化后連接器管腳排布

圖8 優化后連接器電流密度分布

由圖7可知,連接器上部電流密度很大,接近7.5×106A/m2。由圖8可知,優化后的連接器附近電流密度明顯下降,電流密度最大不超過4×106A/m2。

4 復雜饋線系統設計

為實現電子設備小型化、輕型化,微波高頻PTFE板和低頻FR4板混合而成的PCB多層板開始成為一種新的發展潮流,在微波高低頻混合PCB多層板設計中,過孔的設計已成為影響高速PCB板信號完整性的一大關鍵性因素[7]。

傳統的PCB多層板是由相同材料壓合而成,多選用FR4材料,高低頻信號均走在這類材料中。當信號在不同層間過渡時,由于是在相同材料中打過孔,信號受到的影響不大,產生的電磁干擾(EMI)效應較小。高頻、低頻板混壓而成的PCB多層板,由于各層材料的不一致性,過孔在每層的阻抗都會發生突變,信號的完整性受到很大影響,產生較大的EMI[8],過孔的設計就顯得特別重要,它會影響整個系統的電性能。

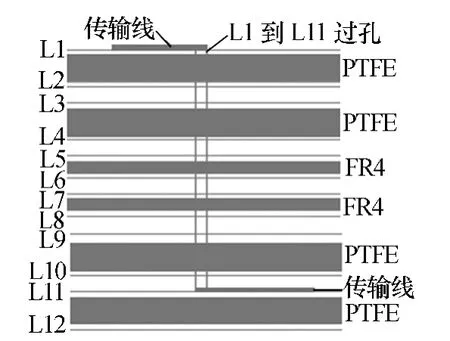

混合PCB多層板結構為:一至四層為微波板,材料為PTFE;五至八層為低頻版,材料為FR4;九至十二層為微波板,材料為PTFE。過孔為L1層傳輸線到L11層傳輸線之間的過渡,中間依次經過2塊PTFE微波板、2塊FR4低頻板、1塊PTFE微波板。如圖9所示。

圖9 混合PCB板層結構圖

三維微波網絡設計的關鍵之一就是設計出適用于該波段的垂直互聯結構。我們設計了一種垂直互聯結構,采用帶狀線-共面波導的垂直過渡形式,將射頻連接器和輸入輸出帶線一體化精確建模,如圖10所示。

圖10 過孔三維模型圖

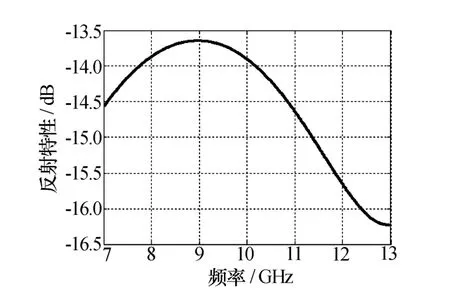

在7 GHz~13 GHz頻帶內對信號的反射、傳輸特性進行研究,信號由L1層傳輸線經過孔到達L11層的傳輸線。過孔優化前信號的反射特性很差,如圖11所示。

圖11 過孔沒有優化時的反射特性

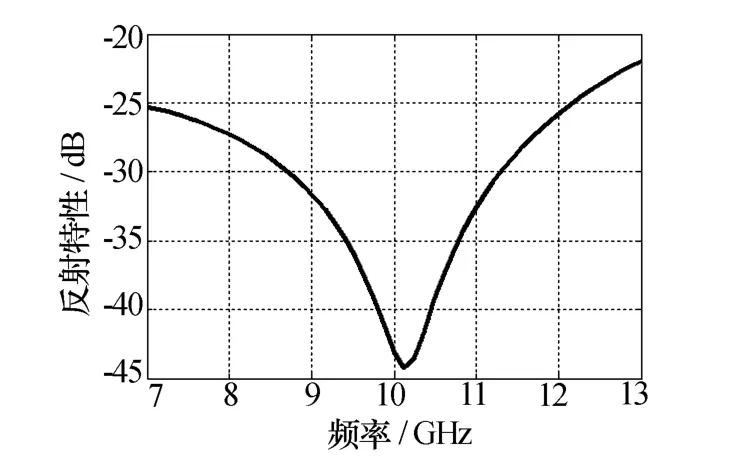

對過孔模型進行優化,改變過孔輸入輸出導帶線寬﹑孔徑大小,過孔隔離區。從而改變信號的反射特性,得出最優反射特性,如圖12所示。

圖12 過孔優化后的傳輸線反射特性

5 結束語

本文探討了雷達陣面綜合布線的設計流程和關鍵方法,復雜饋線系統設計,將綜合背板與綜合線束相結合,應用到雷達陣面綜合布線中,使得雷達陣面體系脈路分明、整潔,可維護性強、抗電磁干擾能力強。

[1]白同云,呂曉德.電磁兼容設計[M].北京:北京郵電大學出版社,2001.Bai Tongyun,Lü Xiaode.ECM design[M].Beijing:Beijing University of Posts and Telecommunications Press,2001.

[2]佟星元,朱樟明,楊銀堂,等.信號完整性設計中的抖動與振鈴消除技術[J].西安電子科技大學學報,2012,39(6):136-141.Tong Xingyuan,Zhu Zhangming,Yang Yintang,et al.Jitter and ringing cancellation techniques for signal integrity design[J].Journal of Xidian University,2012,39(6):136-141.

[3]Kodali V P.Engineering electromagnetic compatibility[M].New York:Wiley Press,2001.

[4]Montrose M I.EMC and the printed circuit board:design,theory,and layout made simple[M].New York:IEEE Electromagnetic Compatibility Society Press,1999.

[5]王高飛,邢秀洪.數字T/R組件的電磁兼容設計[J].現代雷達,2011,33(10):71-73.Wang Gaofei,Xing Xiuhong.EMC design of digital T/R modules[J].Modern Radar,2011,33(10):71-73.

[6]倪志紅.雷達系統開關電源電磁兼容技術研究[J].現代雷達,2006,28(3):91-94.Ni Zhihong.A study on electromagnetic compatibility of switching-power for radar[J].Modern Radar,2006,28(3):91-94.

[7]Thierauf S C.High-speed circuit board signal integrity[M].London:Artech House Publishers,2004.

[8]Howard J,Martin G.High-speed digital design:a handbook of black magic[M].Beijing:Publishing House of Electronics Industry,2004.