面向航電系統的Power架構雙核處理器系統設計

劉 浩,田 澤,劉承禹,雷 宇

(中航工業西安航空計算技術研究所 集成電路與微系統設計航空科技重點實驗室,陜西 西安 710068)

面向航電系統的Power架構雙核處理器系統設計

劉 浩,田 澤,劉承禹,雷 宇

(中航工業西安航空計算技術研究所 集成電路與微系統設計航空科技重點實驗室,陜西 西安 710068)

航電系統在需求牽引和技術推動下正朝著高度綜合化的方向發展,大量的紅外、射頻、信號處理、數字處理模塊被集成在單一系統中,對系統的處理器性能、數據帶寬提出了更高的挑戰。而單一地提高處理器工作頻率已經無法明顯提升系統整體性能,并且會帶來功耗、散熱等問題。雙核處理器解決方案可以在處理器主頻不變的情況下將可執行的指令數增加一倍。航電系統綜合化、小型化和低功耗的需求以及工藝水平的提升,為單芯片集成多處理器內核的設計提供了支撐。文中提出一種面向綜合化航電系統的Power架構雙核處理器系統設計方案。首先對雙核處理器系統架構進行描述,在此基礎上詳細分析了總線互連、復位策略、存儲一致性等關鍵技術。該方案可廣泛應用于高度綜合化航電系統設計領域。

Power架構;雙核;總線互連;存儲一致性

0 引 言

航電系統目前正在向高度綜合化方向發展[1],大量的紅外、射頻、信號處理、數字處理模塊[2]被綜合到一個系統,這對航電系統的性能、帶寬、功耗、散熱提出了嚴峻的挑戰。將多模塊集成為單芯片,能夠大幅度減少元器件種類和板間連接器,有效解決面積、功耗和散熱等問題。因此采用面向綜合化航電系統的專用單芯片雙核處理器設計成為絕佳的解決方案[3]。

PowerPC是一種精簡指令集(RISC)架構的中央處理器,以其優異的性能、較低的能耗以及較低的散熱量被廣泛應用于嵌入式環境[4]。文中提出面向綜合化航電系統的Power架構雙核處理器系統設計方案,內部集成兩個高性能PowerPC處理器,主處理器負責數據處理,從處理器負責FC-ASM協議[5]處理。主、從處理器之間通過DDR2存儲器交換數據。文中對基于Power架構的雙核乃至多核處理器開發具有一定的參考價值。

1 面向綜合化航電系統的Power架構雙核處理器架構設計

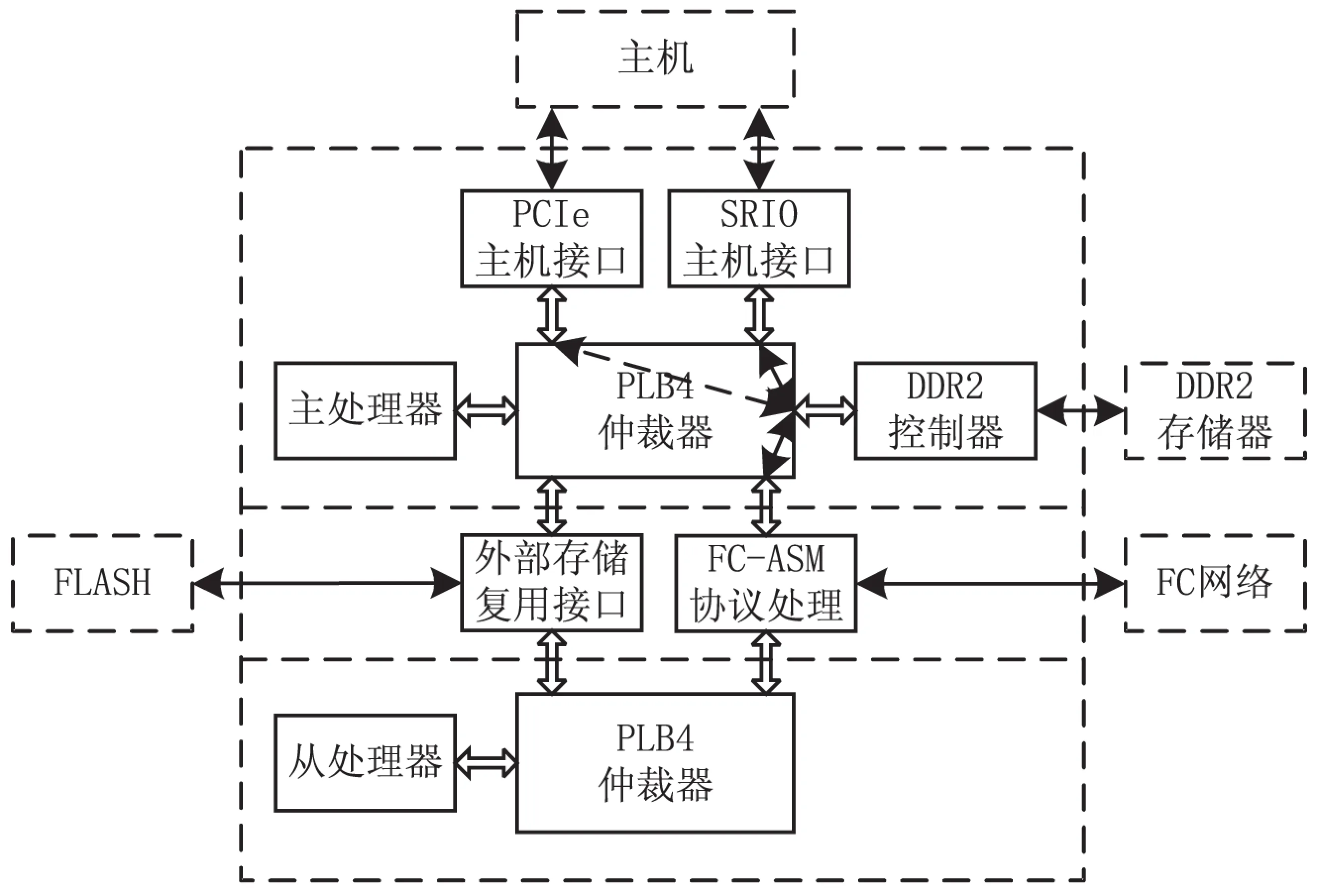

根據主、從處理器的功能劃分,提出面向綜合化航電系統的Power架構雙核處理器架構設計,如圖1所示。

圖1 面向綜合化航電系統的Power

主處理器集成了PCIe、SRIO主機接口和DDR2控制器,同時對FC-ASM協議處理模塊開放一個高速數據接口,提供了一條主機—DDR2存儲器—FC-ASM協議處理模塊之間的數據處理高速通道。從處理器對FC-ASM協議處理模塊開放一個配置接口,提供了初始化以及寄存器配置通道。主、從處理器通過外部存儲復用接口訪問片外FLASH,片外FLASH存放著處理器上電所需的初始化程序。

1 總線互連

主、從處理器以及周邊模塊之間通過PLB4總線[6]進行互連。PLB4總線是高性能數據總線,用于在高速主、從設備之間進行讀數據和寫數據的快速交換。PLB4總線包含64位地址線、128位數據線。每一個PLB主設備通過獨立的地址線、寫數據線、讀數據線和控制信號連接到PLB4總線上;每一個PLB從設備通過共享的地址線、讀數據線、寫數據線、控制和狀態信號連接到PLB4總線上。各個設備對PLB總線的訪問通過一個集中的總線仲裁器來完成總線控制的分配。

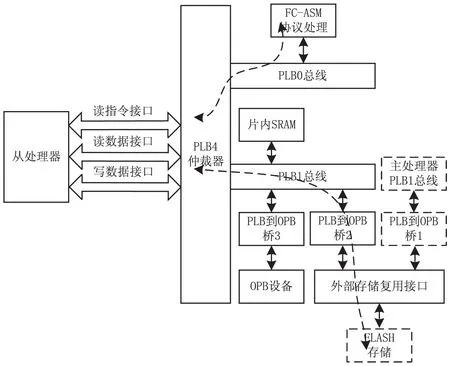

考慮到PCIe、SRIO主機接口與FC-ASM協議處理模塊之間需要通過DDR2存儲器交換大量數據,因此在主處理器PLB0總線上只分配DDR2控制器一個從設備;其余從設備被分配在主處理器的PLB1總線上。主處理器總線互連如圖2所示。

圖2 主處理器總線互連

從圖中可以看出,兩條相對獨立的數據通路:PCIe、SRIO、FC-ASM協議處理模塊與DDR2存儲器之間的FC通信數據通路;主處理器與FLASH存儲之間的程序加載數據通路[7]。

從處理器對冗余的周邊模塊進行裁剪,只保留了與處理器核和FC-ASM模塊正常工作相關的模塊。從處理器總線互連如圖3所示。

圖3 從處理器總線互連

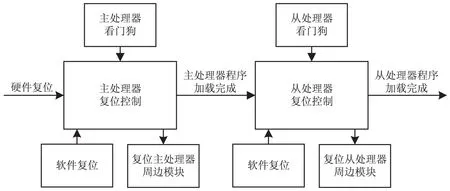

3 復位策略

復位分為硬件復位、軟件復位和看門狗復位三種方式[8-9]。其中主處理器和從處理器具有獨立的軟件復位和看門狗復位。復位策略如圖4所示。

圖4 復位策略

硬件復位結束后,主處理器開始初始化并從外部FLASH加載程序[10-14],待主處理器程序加載完成后,從處理器開始初始化并從外部FLASH加載程序。

4 存儲一致性信號量方案

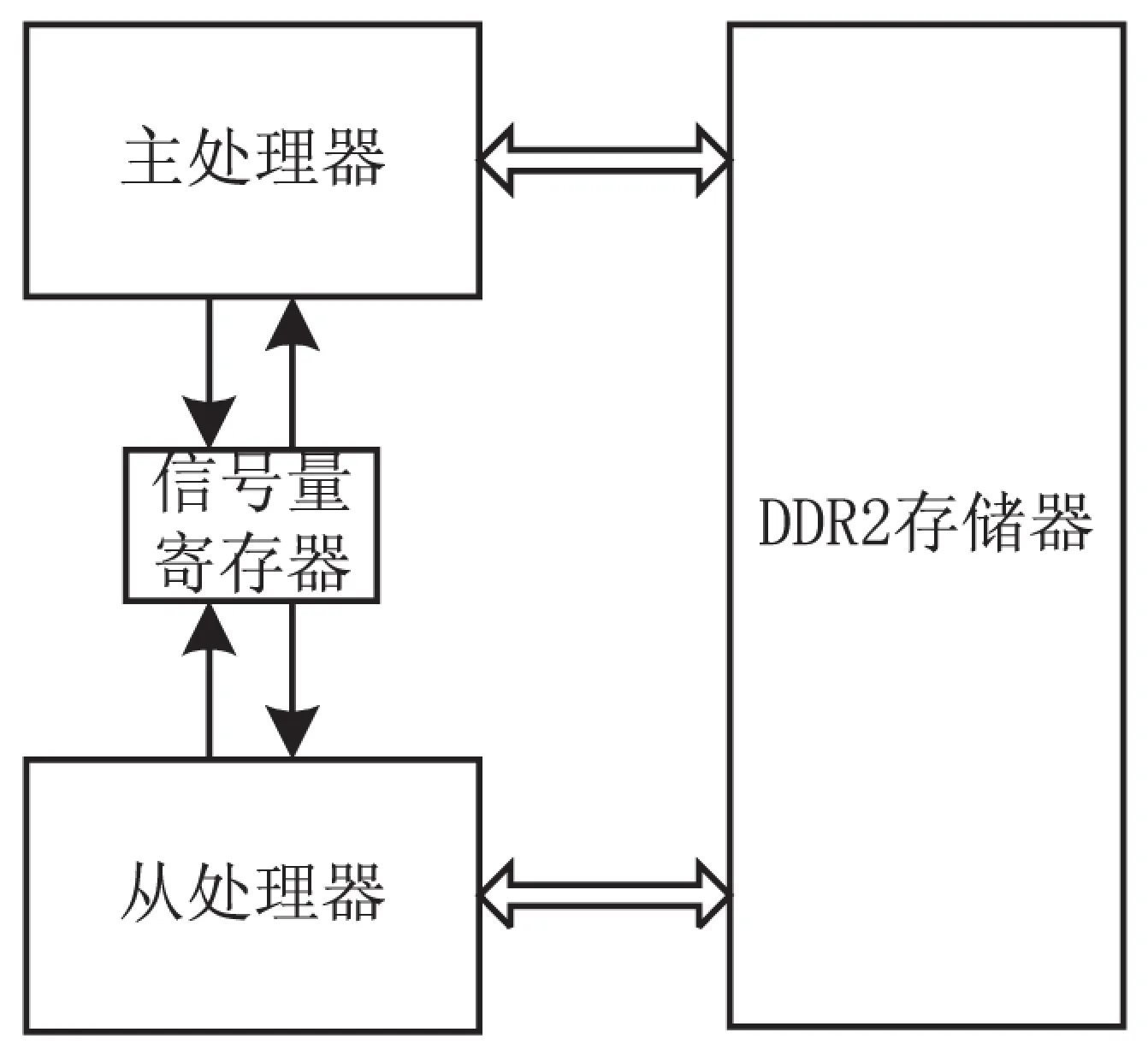

主、從處理器之間通過DDR2存儲器交換數據,為了保證存儲一致性[15],文中提出了一種信號量的解決方案。

存儲一致性信號量方案如圖5所示。

圖5 存儲一致性信號量方案

主、從處理器共享一個信號量寄存器。如果從處理器要對DDR2存儲器進行訪問,應先讀取信號量寄存器,如果寄存器值為“0”,表明主處理器正在對DDR2存儲器進行訪問。主處理器完成對DDR2存儲器的訪問后,對信號量寄存器進行寫操作,寫操作會將信號量寄存器主處理器端置“0”,從處理器端置“1”。從處理器讀取到信號量寄存器值為“1”后,表明從處理器可以發起對DDR2存儲器的訪問。信號量解決方案提供了主、從處理器對共享的DDR2存儲器的互斥操作機制,保證了存儲一致性。

5 結束語

文中提出了面向綜合化航電系統的Power架構雙核處理器系統設計方案,詳細論述了架構設計、總線互連、復位策略、存儲一致性設計。面向航電系統特定應用,將多模塊集成到單片,有效解決了原系統存在的面積、功耗、散熱、布線復雜等問題。文中對基于Power架構的雙核乃至多核處理器開發具有一定的參考價值。

[1] 李成文,李 鵬,湛文韜,等.一種小型化高性能綜合處理系統的設計與實現[J].航空計算技術,2014,44(4):121-125.

[2] 劉麗君,賀占莊,李 灝.基于PowerPC的嵌入式系統硬件設計[J].計算機技術與發展,2008,18(2):251-253.

[3] Kuon I,Tessier R,Rose J.FPGA architecture survey and challenges[J].Foundation and Trends in Electronic Design Automation,2008,2(2):135-253.

[4] 潘 越,宋 萍,李科杰.基于PowerPC和FPGA的小型無人直升機飛行控制計算機系統設計[J].計算機測量與控制,2013,21(1):112-115.

[5] John G H,Hani S M.Numerical modeling of ore dilution in blast hole stoping[J].International Journal of Rock Mechanics and Mining Sciences,2007,44(5):692-703.

[6] 128-bitprocessor local bus architecture specifications[M].[s.l.]:IBM,2004.

[7] PPC464-H90 embedded processor core support manual[M].[s.l.]:IBM,2007.

[8] 林學龍.MPC8xx系列處理器的嵌入式系統復位電路設計[J].單片機與嵌入式系統應用,2005(4):80-83.

[9] 王 勇.基于MPC8641D處理器的對稱多處理技術研究[J].信息與電腦,2010(5):22-23.

[10] 周 洪,沈 華.基于MPC8640處理器的通用處理模塊硬件設計[J].電腦知識與技術,2014,10(20):4922-4925.

[11] 許 偉,馮 萍,郭海山.光纖通道交換網絡接口卡的零拷貝技術研究與實現[J].計算機測量與控制,2008,16(3):366-369.

[12] 王長清,岑 凡,蔡惠智.基于PowerPC架構多核處理器嵌入式系統硬件設計[J].微計算機信息,2010,26(6-2):6-7.

[13] 劉麗君,賀占莊,李灝.基于PowerPC的嵌入式系統硬件設計[J].計算機技術與發展,2008,(02):251-253.

[14] 李 攀,田 澤,蔡葉芳,等.基于SOPC的PCI通信接口設計與實現[J].計算機技術與發展,2009,(09):211-214.

[15] 陳海榮.基于雙核PowerPC處理器的高性能計算模塊設計[J].計算機測量與控制,2011,19(11):2824-2827.

Avionics System-oriented Design of Dual-core Processor System Based on Power Architecture

LIU Hao,TIAN Ze,LIU Cheng-yu,LEI Yu

(Aeronautics Science and Technology Key Laboratory of Integrate Circuit and Micro-system Design,AVIC Computing Technique Research Institute,Xi’an 710068,China)

With the development trend of high-integration in avionics system under requirement and technique,more and more modules such as infrared devices,radio frequency devices,DSPs are integrated in a single system,which leads to a higher challenge to CPU performance and data bandwidth.The rise of CPU frequency solely would not promote the system performance and would cause problems of power consumption and heat radiation.The method of dual-core will double the number of instructions without changing the CPU frequency.The needs of integration,miniaturization and lower power-consumption in avionics system and development of technology brings supports to the design of multi-cores integrated in a single chip.A design scheme of integrated avionics system-oriented design of dual-core processor based on Power architecture is proposed.First,the architecture of dual-core processor is described,based on which analyzes bus interconnection,reset strategy,memory consistency in details.This scheme can widely adopt to design field of highly integrated avionics system.

Power architecture;dual-core;bus interconnection;memory consistency

2015-06-12

2015-09-18

時間:2016-03-04

中國航空工業集團公司創新基金(2010BD63111)

劉 浩(1985-),男,碩士研究生,工程師,研究方向為集成電路設計;田 澤,博士,研究員,中航首席技術專家,研究方向為SoC設計、嵌入式系統設計、VLSI設計等。

http://www.cnki.net/kcms/detail/61.1450.TP.20160304.1508.002.html

TP39

A

1673-629X(2016)03-0190-03

10.3969/j.issn.1673-629X.2016.03.044