軍用大規模集成電路關鍵外協工序控制

張 玲,田 澤

(1.中國航空工業集團公司 西安航空計算技術研究所,陜西 西安 710068;2.集成電路與微系統設計航空科技重點實驗室,陜西 西安 710068)

軍用大規模集成電路關鍵外協工序控制

張 玲1,2,田 澤1,2

(1.中國航空工業集團公司 西安航空計算技術研究所,陜西 西安 710068;2.集成電路與微系統設計航空科技重點實驗室,陜西 西安 710068)

隨著半導體技術的進步和發展,專業化分工越來越精細,后端設計、流片加工、封裝、測試都已成為專門領域。而集成電路設計、加工各個環節環環相扣密不可分,任何一個環節出現問題都可能導致整個芯片流片的失敗。因此如何保證每一個環節的正確性,是每一個集成電路設計單位都面臨的問題,其中如何控制集成電路設計的關鍵外協工序也就變得尤為重要。文中對目前軍用大規模集成電路的后端設計、芯片制造、封裝的流程及關鍵工序進行了分析和論述,總結了設計方應重點關注的芯片的后端設計、流片、封裝的工藝流程、關鍵工序及檢查方法,對集成電路設計關鍵外協工序質量控制有較好的指導意義。

后端設計;芯片制造;芯片封裝;關鍵工序控制

0 引 言

集成電路是信息產業的核心,隨著半導體技術的進步和產業發展,專業化分工越來越精細,集成電路產業從最初的IDM模式發展到目前設計[1-2]、制造、測試[3]分離的局面,產生了眾多專業從事集成電路設計的公司。通常情況下,集成電路設計公司只負責電路設計,芯片的流片、封裝、測試均由專業機構承擔,外協過程的質量,在很大程度上直接決定著集成電路產品的質量和成本。對于廣大設計公司而言,集成電路的外協過程進行質量控制已成為產品成敗的關鍵。對供應商的質量控制已成為集成電路設計企業項目及質量管理[4-5]的重要組成部分。

為提升芯片產品質量,需要建立科學規范的流程,設置質量控制點,建立質量控制方法和程序,按照PDCA的思想持續改進[6-7]。文中根據外包外協的材料或服務對集成電路產品特性影響的重要程度,重點對物理設計、制造、封裝三個環節進行分析,總結提出了每個環節的質量控制點和控制方法。

1 關鍵外協工序質量控制方法

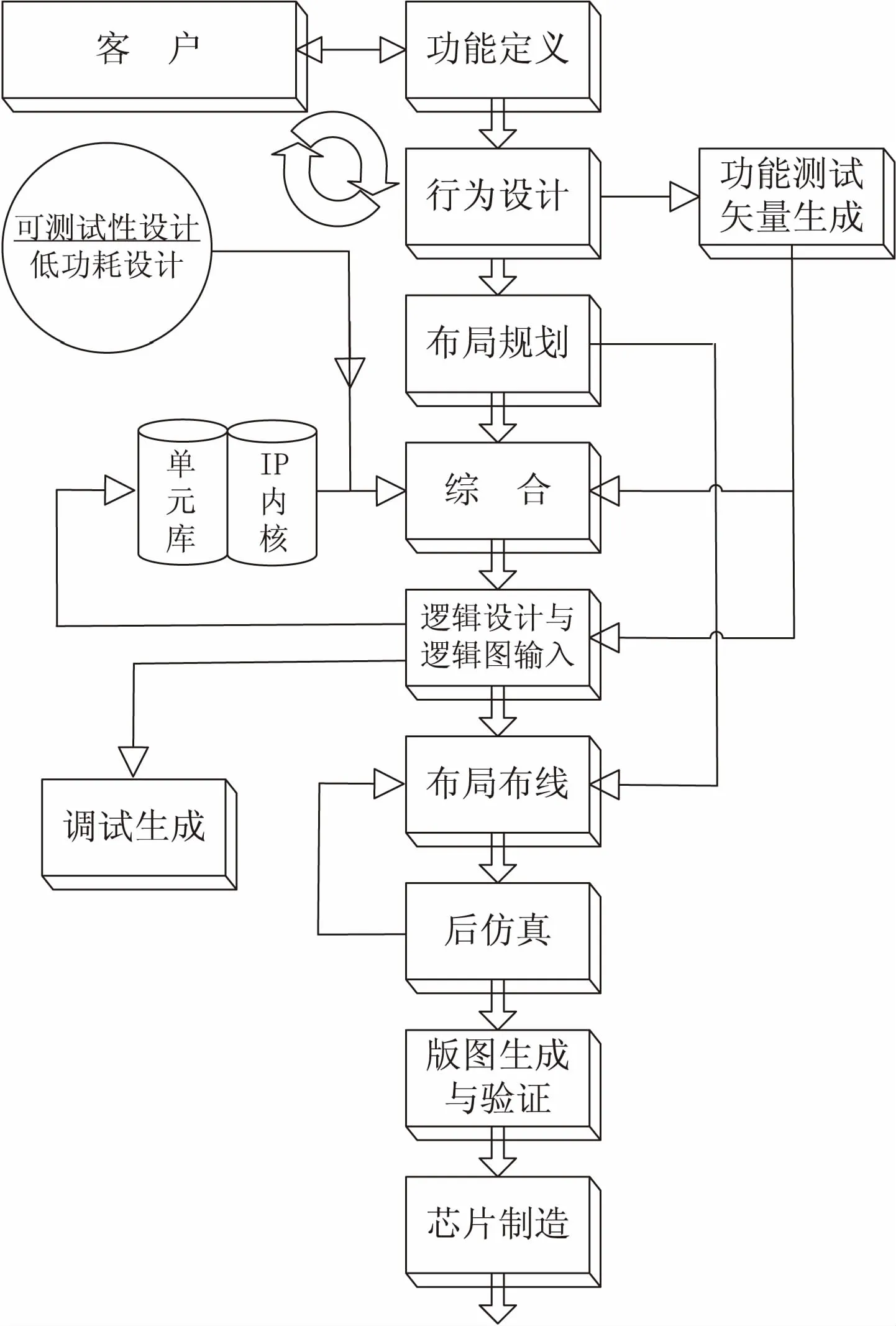

1.1 集成電路后端設計流程及關鍵工序

隨著集成電路專業分工的日益精細,后端版圖設計已經發展為一個獨立的專業,版圖設計是制造集成電路的基礎。計算機輔助的版圖設計將電路中所有元器件及其相互連接轉換成能進行芯片光刻加工、正確可靠的掩模圖形數據。專門的掩模制備公司利用所提供的數據,制備出符合流片需要的多層掩模版。通常的集成電路后端設計流程如圖1所示。

圖1 集成電路后端設計流程

后端設計工程師可以根據前端設計的數據及約束要求完成后端設計工作[8-9],委托方只需要進行預定步驟的檢查以確定后端設計與前端設計的一致性。傳統的檢查主要是設計規則檢查(DRC)、電學規則檢查(ERC)、版圖與電路圖一致性檢查(LVS)。隨著電路復雜度的提升和工藝尺寸的進一步縮小,在投片前Signoff時需要檢查的內容也日益增多,包括時序分析與檢查、功能一致性檢查、電源及信號完整性檢查、功耗分析與確認、ESD[10-11]及可靠性相關檢查。具體檢查項目與方法如表1所示。

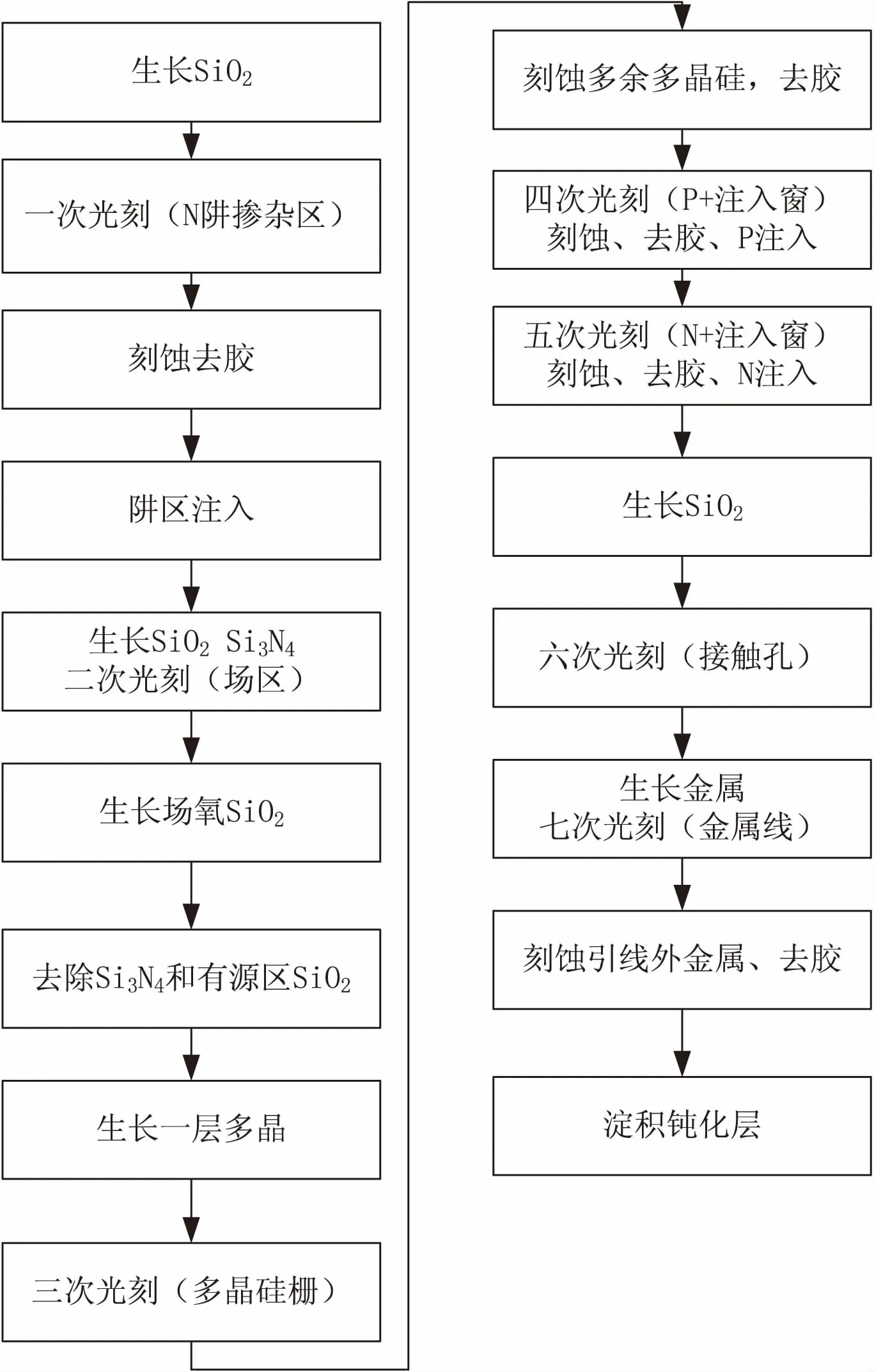

1.2 集成電路制造工藝流程及關鍵工序控制

芯片制造與互聯組成了微電子工業的高端譜線,在微電子工業中,性能和小型化保持著每18個月翻一番的發展速度,新材料和新工藝不斷提高以滿足工業性能和小型化目標。目前,集成電路的流片幾乎都是采用代工方式完成。

圖2是典型的集成電路制造工藝流程示意圖。

圖2 典型的集成電路制造工藝流程

集成電路流片費用隨著工藝的提高,價格也是成倍增加。例如,130 nm工藝工程批流片費用在200萬左右,65 nm工藝工程批流片費用在400萬左右,40 nm工藝工程批流片費用在800萬元左右。如果流片成功,由于可產生管芯數量較多,單只管芯成本并不高,但是一旦流片失敗,損失是非常大的。因此,如何保證流片不產生除設計缺陷以外的問題,保證芯片一

表1 集成電路后端檢查項目

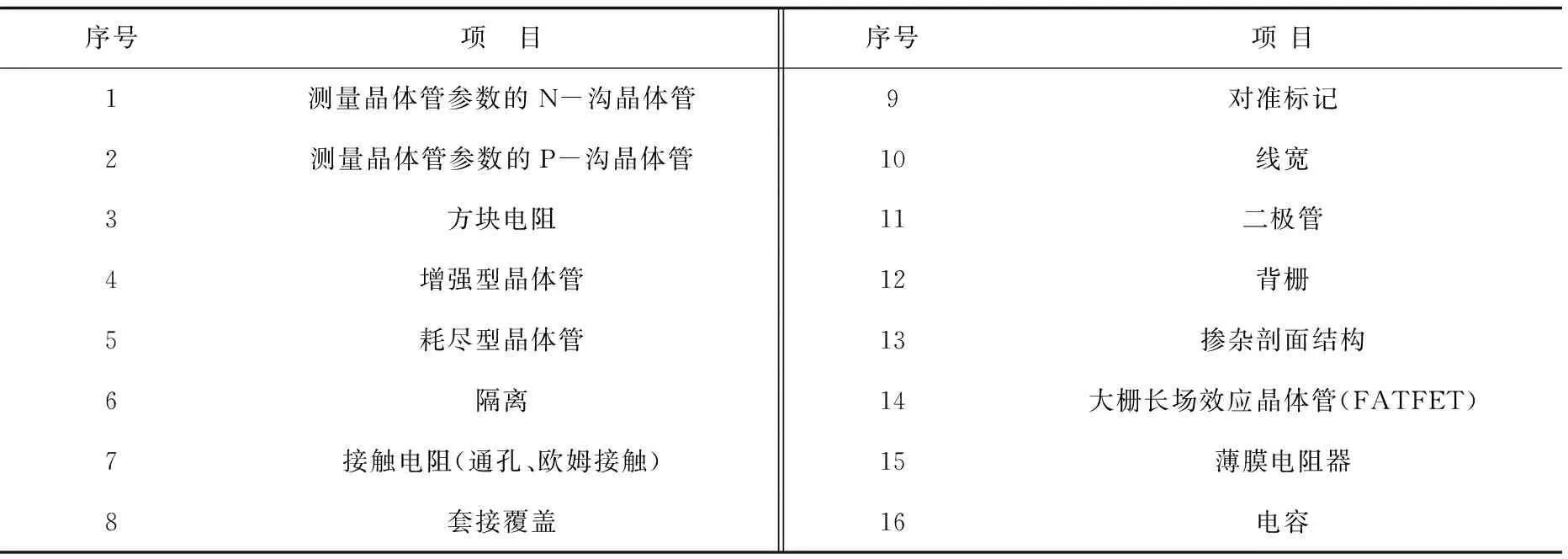

次投片成功至關重要。流片工序的檢查依據是,按照GJB548B[12]方法5013 GaAs工藝的晶圓制造控制和接收程序通過對工藝檢測圖形和目檢進行檢查,工藝檢測(PM)圖形是一組為工藝控制和確定晶圓可接收性提供數據的測試結構,PM可以插入于每個晶圓的特定位置,位于劃片槽位置,或包含在每個芯片中,也可以是這些方案的組合。建議的用于PM中的測試圖形如表2所示。

表2 PM中的測試圖形

晶圓接收要依據在制造過程中進行的PM室溫測試所提供的信息,對每一個晶圓逐片檢查。另外,在晶圓制造期間,應在關鍵工序進行光學顯微鏡或SEM檢查,檢查可以包括圖形對準標記和臨界尺寸測量。最終外包方應檢查所有規定的PM電參數的測量和數據記錄,必要時可以要求加工方提供除PM以外所有檢查的或測試的結果,每批的接收、拒收晶圓數目,返工晶圓數目和返工原因等。

1.3 集成電路封裝流程及關鍵工序控制

集成電路的封裝目的是為芯片提供一個接口,將內部電性訊號通過引腳將芯片連接到系統,并避免硅芯片受外力與水、濕氣、化學物的破壞與腐蝕,IC封裝屬于半導體產業的后段加工制程,主要是將前制程加工完成(即晶圓廠所生產)的晶圓上的IC予以分割,黏晶、打線并通過管殼實現對外部的鏈接。圖3為IC芯片的封裝流程。

集成電路封裝作為一個專門的專業分支,具有非常復雜的流程及質量管控體系[13]。現有的軍級電路基本都是陶瓷封裝的,國內擁有軍用集成電路封裝貫標線資質的單位有兩家:中電58所及航天772所。在貫標生產線上封裝的產品,用戶只需要檢查封裝工藝流程卡及生產線用于證明工藝一致性的首件產品的測試報告即可。劃片、鍵合和封帽是芯片封裝過程的關鍵工序,此三個步驟后的檢查(芯片鏡檢、鍵合檢查、氣密性檢查)應該在封裝工藝流程卡里面留有實驗記錄及具體測量數據。

對于塑封電路,國內可以完成芯片塑封的單位有很多,如天水華天、航天771所、深南電路等等;但是由于工藝水平的限制,目前國內尚無軍用塑封的貫標生產線。2011年,國內第一個指導塑封電路軍品認證的文件GJB7400-2011(合格制造廠認證用半導體集成電路通用規范[14])正式頒布,但目前國內還沒有企業通過認證。

圖3 IC芯片的封裝流程

2 結束語

集成電路的設計、實現、流片、封裝、測試是一個非常復雜的系統工程,每一個環節都是一個專門的學科,而集成電路各環節環環相扣密不可分,任何一個環節出現問題都可能導致流片的失敗,因此如何保證每一個流程的正確性是每一個集成電路設計單位都面臨的難題。文中總結了集成電路后端設計、流片、封裝工藝流程及關鍵工藝檢查流程,從而盡量減少外協合作環節中可能引入的各類問題,提高一次流片成功率。

[1]FurberS.ARMSystem-on-ChipArchitecture(ARMSoC體系結構)[M].田 澤,于敦山,譯.臺北:五南圖書出版公司,2003.

[2] 田 澤.航空專用集成電路-設計理論與工程實踐[M].北京:航空工業出版社,2013.

[3] 田 澤.SoC設計與測試[M].北京:航空工業出版社,2003.

[4] 科茲納.項目管理[M].北京:電子工業出版社,2006.

[5] 項目管理協會.Projectmanagementinstitute[M].北京:電子工業出版社,2009.

[6] 劉 銳,姚世鋒.半導體集成電路芯片質量與可靠性保證方法[J].兵工自動化,2013,32(6):17-19.

[7] 楊建生,李守平.對集成電路封測項目進度、投資與質量控制管理的探討[J].電子工業專用設備,2015(1):1-4.

[8] 羅志華,權進國,楊華中.基于層次法實現EOS芯片的后端設計[J].微計算機信息,2008,24(14):5-7.

[9]HodgesDA,JacksonHG,SalehRA.Analysisanddesignofdigitalintegratedcircuitsindeepsubmicrontechnology[M].[s.l.]:[s.n.],2005.

[10] 蔣玉賀,王 爽.CMOS集成電路ESD設計[J].微處理機,2008,29(3):19-21.

[11]KerKD,ChenTY,WuCY.ESDprotectiondesignonanalogpinwithverylowinputcapacitanceforhigh-frequencycurrent-modeapplication[J].IEEESolid-StateCircuits,2000,35(8):1194-1199.

[12] 陳裕焜,賈新章,張德勝,等.微電子器件試驗方法和程序[S].北京:總裝備部軍標出版發行部,2005.

[13] 韓忠華,王長濤,馬 斌,等.半導體封裝生產線工藝流程分析[J].科技廣場,2010(8):147-149.

[14] 李 錕,陳裕焜,秦國林,等.合格制造廠認證用半導體集成電路通用規范[S].北京:總裝備部軍標出版發行部,2011.

Critical Outsource Procedure Control for Military VLSI

ZHANG Ling1,2,TIAN Ze1,2

(1.AVIC Computing Technique Research Institute,Xi’an 710068,China;2.Key Laboratory of Aviation Science and Technology on Integrated Circuit and Micro-system Design,Xi’an 710068,China)

With the rapid advance and development of semiconductor technology,the division of labor has become more and more elaborate.The back-end design,chip processing,packaging and test has already developed into special areas.Integrated circuit design,processing and other steps are tied closely to each other,problems in any part of the whole procedure may lead to a chip tape-out failure.Therefore,how to ensure the correctness of every aspect of the whole procedure is always an important problem for every IC designer,especially for the problem of how to control the outsourcing procedure.Based on analysis of the process of back-end design,fabrication and packaging for military VLSI,it summarizes the key procedures and control methods of the back-end design,fabrication and packaging and checking in this paper,which is meaningful for the quality control of military VLSI outsourcing design.

back-end design;fabrication;packaging;key procedure control

2014-10-13

2015-01-05

時間:2016-05-05

中國航空工業集團公司創新基金(2010BD63111)

張 玲(1982-),女,碩士,研究方向為項目管理;田 澤,博士,研究員,中國航空工業集團首席技術專家,研究方向為SoC設計、嵌入式系統設計、VLSI設計等。

http://www.cnki.net/kcms/detail/61.1450.TP.20160505.0814.012.html

TP39

A

1673-629X(2016)05-0170-03

10.3969/j.issn.1673-629X.2016.05.037