基于0.13 μm CMOS 工藝的功率放大器設計

張 博, 原亞運, 賀 剛

(西安郵電大學 電子工程學院 ,陜西 西安 710121)

?

基于0.13 μm CMOS 工藝的功率放大器設計

張博, 原亞運, 賀剛

(西安郵電大學 電子工程學院 ,陜西 西安 710121)

基于0.13μmCMOS工藝,設計13~15GHz帶有分布式有源變壓器的集成功率放大器。利用分布式有源變壓器功率合成的特點,將其作為負載去匹配功放單元,采用共源共柵級與共源級級聯的功放單元結構來提高功放單元的增益和輸出功率;采用浮柵結構來減小分布式有源變壓器和片上巴倫的插入損耗;功分器采用帶柵格參考地的結構提高電路的性能。仿真結果表明,在13~15GHz頻段,該功放的飽和輸出功率為20dBm,功率附加效率為10%,功率增益為12.5dB,輸出功率和功率增益有所提高,減小了插入損耗。

互補金屬氧化物半導體;分布式有源變壓器;浮柵;功率放大器

在互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor, CMOS)集成電路技術中,高增益和高輸出功率的功率放大器尤為重要[1]。當頻率上升到毫米波的時候,功率放大器的設計難度相應加大。為了改善功率放大器的性能,GaAs、Inp HEMT和SiGe BiCMOS等化合物半導體工藝被應用在制造高性能功率放大器上[2],但CMOS相對于化合物半導體工藝具有低成本和高集成度的優點,持續促進著CMOS功率放大器的研究。

在功率合成放大器的設計中,晶體管的擊穿電壓低和片上阻抗傳輸的損耗高是至關重要的問題之一[3-4],其中損耗直接影響著功率放大器輸出功率的大小。 雖然,片上1∶N變壓器或者LC諧振匹配網絡可以被用于阻抗傳輸,但是由于介質的低電阻率和金屬的高損耗的原因,導致這些阻抗傳輸器件在CMOS工藝中產生很大的損耗。

本文將嘗試利用0.13 μm CMOS工藝設計13~15 GHz分布式有源變壓器(Distributed Active Transformer,DAT)的功率放大器,以期提高功放的輸出功率和增益,減小插入損耗。

1 CMOS DAT功率放大器整體設計

為了實現高功率輸出和高增益的功率放大器,需要通過多級功放單元進行功率合成,從而提高功放性能。利用分布式有源變壓器(Distributed Active Transformer,DAT)進行4路功放單元的阻抗傳輸和功率合成。CMOS DAT功率放大器的整體電路[5]包括功放單元、片上巴倫、DAT和功分器,結構如圖1所示。1個功分器和2個片上巴倫級聯起來同時驅動4個功放單元,然后再通過DAT和片上巴倫的級聯將4個功放單的功率合成進行輸出。

當工作頻率上升到15 GHz的時候,功分器、片上巴倫和DAT都會有插入損耗,而且也會降低CMOS DAT功率放大器的性能。下面分別對功放單元、DAT、片上巴倫和功分器進行設計。

1.1功放單元

在功放單元的設計中,共源結構作為功率輸出級被用來獲得最大功率輸出,共源共柵級作為驅動級被用來提高增益[6]。同時,利用增益增強技術[7]進行增益彌補。功放單元的原理如圖2所示。

圖2 功放單元的原理

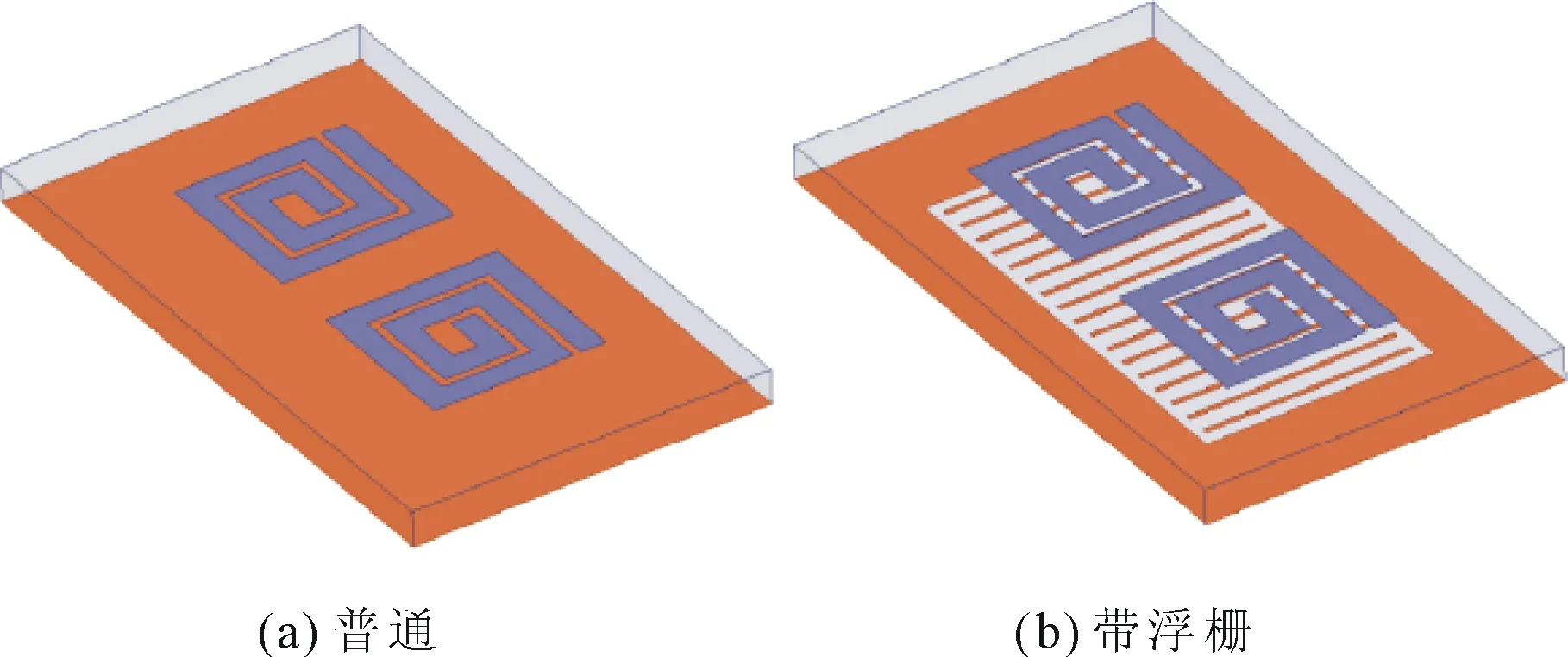

1.2片上巴倫

片上巴倫采用寬邊線耦合的形式來提高自身耦合效應。由于片上巴倫的插入損耗來源于導體和介質,其中介質損耗是由電磁場產生的渦輪電流導致, 故功率合成中需減小片上巴倫的損耗。通過使用浮柵結構[8],既可以有效地的減小片上巴倫的損耗,也可以減小介質中的電流,隔離度和高頻性能也會進一步增提升。圖3為普通片上巴倫和帶浮柵片上巴倫的3D示意圖。

圖3 片上巴倫3D示意圖

采用電磁仿真軟件(Advanced Design System,ADS)分別對普通片上巴倫和帶浮柵片上巴倫進行電磁仿真,散射參數S仿真結果如圖4所示。在13~15 GHz應用頻段內,帶浮柵片上巴倫的S(2,1)比普通巴倫的S(2,1)大1 dB左右(差損小1 dB左右),并且在-10 dB以下,帶浮柵巴倫的S(1,1)比普通巴倫的S(1,1)頻帶寬2 GHz。因此,帶浮柵的片上巴倫相比普通片上巴倫有更小的差損,而且也有更寬的帶寬。

圖4 普通和帶浮柵片上巴倫S參數仿真結果對比

1.3分布式有源變壓器

傳統變壓器耦合放大器能夠有效合成兩路功放單元來實現功率合成功能[9],而分布式有源變壓器(DAT)比傳統變壓器耦合的方式更加適合于多路功放單元的功率合成[10]。對于N路功放單元合成電路,DAT不僅可以合成每個功放單元的射頻輸出功率,而且同時進行1:N阻抗變換,對于低阻抗系統來說,這樣能夠簡化匹配網絡,減少每一路功放單元的輸出匹配電路,提高整體電路的緊湊性。

DAT的3D示意圖如圖5所示。在每個變壓器的輸入端并入電容。由于每一對輸入信號均為差分輸入,等效于在輸入結構的輸入端并入接地電容。引入合理的電容與寄生電感諧振,在不影響變壓器合成效果的基礎上有效地降低了合成插損,同時還有效地減小了合成變壓器的面積。DAT采用兩路差分信號輸入,一路差分信號輸出的合成方式,使用差分信號合成的方式能夠有效地抑制電路中信號的噪聲[11]。同時,應用浮柵技術在DAT上,使DAT具有結構簡單、緊湊的優點。

圖5 帶浮柵DAT的3D示意圖

通過ADS軟件電磁仿真,圖6給出了帶浮柵 DAT的S參數仿真結果,在13~15 GHz應用頻段內功率合成的插損只有0.8 dB,而且在應用頻段內輸出端口的反射小于 -10 dB。

圖6 帶浮柵DAT的S參數仿真結果

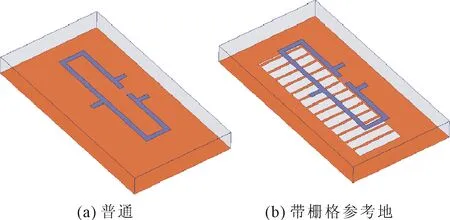

1.4功分器

功分器采用如圖7(b)所示的帶柵格參考地的結構。這種結構既適合片上電路設計的要求,同時又能提高電路的性能[12-13]。

圖7 功分器3D示意圖

通過ADS分別對普通功分器和帶柵格地功分器進行電磁仿真,S參數仿真結果如圖8所示。可以看出采用柵格地功分器的插損只有0.5 dB,比普通功分器的差損要小0.2 dB。

圖8 普通和帶柵格地功分器的S參數仿真結果

2 仿真結果

采用0.13 μm CMOS工藝,CMOS DAT功率放大器芯片的CMOS版圖如圖9所示。在ADS中進行CMOS DAT功率放大器的電磁仿真,S參數仿真結果、輸出功率(Pout)和功率附加效率(PAE)分別如圖10和圖11所示。

圖9 CMOS DAT功率放大器的版圖

圖10 S參數仿真結果

由圖10 CMOS DAT功率放大器的S參數仿真結果可以知道,CMOS DAT功率放大器的功率增益S(2,1)為12.5 dB±1 dB,反射系數S(1,1)小于-10 dB。

圖11 輸出功率和功率附加效率仿真結果

由圖11可知,所設計的CMOS DAT功率放大器的輸出飽和功率接近為20 dBm,此時功率附加效率為10%。

由仿真結果可以看出,CMOS DAT功率放大器提高了DAT功放的增益和輸出功率; CMOS DAT功率放大器的飽和功率可以達到20 dBm,功率增益為12.5 dB。

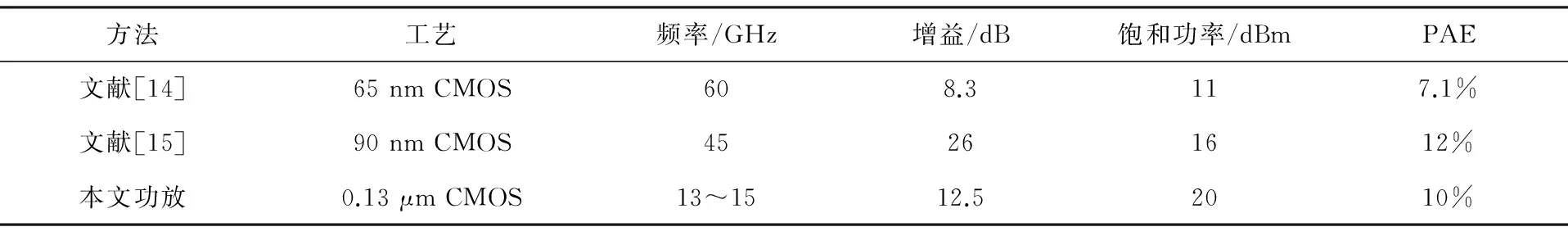

對比文獻[14]和文獻[15]功率放大器和本文功放的關鍵參數,結果如表1所示。可以看出,本設計的增益為12.5 dB,飽和輸出功率達到20 dBm,而且PAE也達到10%,功率放大器的性能指標得到了提高。

表1 CMOS功率放大器對比

3 結語

基于0.13 μm CMOS工藝的13~15 GHz分布式有源變壓器的功率放大器,通過優化整體功放內部模塊電路,共源共柵級與共源級級聯的功放單元有效提高了功放單元的增益和輸出功率,并且采用浮柵和帶柵格地的電路技術減小了CMOS DAT功率放大器中片上巴倫、分布式有源變壓器和功分器的插入損耗。仿真結果表明,該功放的飽和輸出功率可以達到20 dBm,功率附加效率為10%,在13~15 GHz頻段功率增益為12.5 dB,減小了插入損耗,有效地提高了CMOS DAT功率放大器的整體性能。

[1]郭超, 張文俊, 余志平. 60GHz 11dBm CMOS功率放大器設計[J]. 半導體技術, 2009, 34(12):1231-1234.

[2]陰亞芳, 張虹, 張博,等. 基于GaAs電感模型的微波功率放大器[J]. 西安郵電大學學報, 2014, 19(2):94-97.DOI:10.13682/j.issn.2095-6533.2014.02.018.

[3]韋小剛, 吳明贊, 李竹. 提高共源共柵CMOS功率放大器效率的方法[J]. 電子器件, 2011, 34(2):184-186.

[4]CHANG J N, LIN Y S. A high-performance CMOS power amplifier for 60 GHz short-range communication systems[J]. Microwave & Optical Technology Letters, 2013, 55(5):1155-1160.

[5]JEN Y N, TSAI J H, HUANG T W, et al. Design and analysis of a 55 to 71-GHz compact and broadband distributed active transformer power amplifier in 90-nm CMOS process[J]. IEEE Transactions on Microwave Theory & Techniques, 2009, 57(7):1637-1646.

[6]張海鵬, 汪洋, 李浩. 0.18μm CMOS高效高增益功率放大器設計[J]. 杭州電子科技大學學報, 2012(5):9-12.

[7]HE G, ZHANG B, SHEN X. A k-band gain enhanced power amplifier in 0.18μm CMOS process by slow wave structure[C]//2014 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT) Hefei:IEEE,2014:1-3. DOI:10.1109/RFIT.2014.6933257.

[8]XU L, WEI J. Characterization and analysis of patterned shields for millimeter-wave broadside-coupled balun in CMOS technology[C]// 2012 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Shenzhen:IEEE,2012:1-4.DOI: 10.1109/ICMMT.2012.6230018.

[9]徐元中, 梅菲, 周鑫. 基于片上變壓器耦合的CMOS功率放大器設計[J]. 電子元件與材料, 2015(6):87-89.

[10] AOKI I, KEE S D, RUTLEDGE D B, et al. Distributed active transformer: A new power-combining and impedance-transformation technique[J]. IEEE Transactions on Microwave Theory & Techniques, 2002, 50(1):316 -331.

[11] PFEIFFER U R, GOREN D. A 23-dBm 60-GHz Distributed Active Transformer in a Silicon Process Technology[J/OL]. IEEE Transactions on Microwave Theory and Techniques, 2007, 55(5):857-865[2016-01-20].http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4195676. DOI:10.1109/TMTT.2007.895654.

[12] LEE J H,CHEN C C, LIN Y S, et al. A V-band CMOS sub-harmonic mixer with integrated frequency doubler and 180°out-of-phase splitter[J]. Microwave and Optical Technology Letters,2011,53(4):870-875.DOI: 10.1002/mop.25888.

[13] 陳新宇, 蔣幼泉, 黃念寧,等. K波段單片功率放大器[J]. 功能材料與器件學報, 2000(3):154-156.

[14] FEI W ,HAO Y ,YEO K S ,et al. A 44-to-60GHz, 9.7dBm P1dB, 7.1% PAE power amplifier with 2D distributed power combining by meta material-based zero-phase-shifter in 65nm CMOS[C]//2012 IEEE MTT-S International Microwave Symposium Digest (MTT), Montreal, QC, Canada :IEEE, 2012:1-3.DOI: 10.1109/MWSYM.2012.6258391.

[15] ZHU F, HONG W, CHEN J X. A 40~50 GHz power amplifier with flat gain response in 90 nm CMOS technology[C]// 2014 IEEE International Wireless Symposium (IWS), Xi’an: IEEE,2014:1-4.DOI:10.1109/IEEE-IWS.2014.6864190.

[責任編輯:祝劍]

Design of power amplifier in 0.13 μm CMOS process

ZHANG Bo,YUAN Yayun,HE Gang

(School of Electronic Engineering , Xi’an University of Posts and Telecommunications, Xi’an 710121, China)

A 13~15 GHz fully integrated power amplifier with distributed active transformer (DAT) in 0.13 μm CMOS technology is presented. The DAT is used as the load to match the power amplifier(PA)unit, PA units employ cascade of common source stage and cascade stage to improve the gain and output power. Moreover, the patterned floating shield (PFS) is utilized to reduce the insertion loss of the DAT and on-chip balun, the patterned ground shield (PGS) structure is utilized to improve the Circuit performance. Simulation results show that CMOS DAT PA delivers 20 dBm saturated output power with 10% power added efficiency (PAE), and performs a gain of 12.5 dB from 13 to 15 GHz, the output power and the power gain are improved, and the insertion loss is reduced.

complementary metal oxide semiconductor, distributed active transformer, patterned floating shield, power amplifier

10.13682/j.issn.2095-6533.2016.04.011

2016-02-23

國家自然科學青年基金資助項目(61201044)

張 博(1983-)男,博士,副教授,從事射頻模擬集成電路設計研究。E-mail:zhangbo@xupt.edu.cn

原亞運(1990-)男,碩士研究生,研究方向為射頻集成電路系統設計。E-mail:yuanyayun@sxasic.com

TN385

A

2095-6533(2016)04-0057-05