404 Not Found

404 Not Found

高速彈載記錄儀存儲技術研究

劉雪飛,馬鐵華,劉廷輝,尤文斌,崔 敏

(1.中北大學 電子測試技術國家重點實驗室,山西 太原 030051;2.中北大學 儀器科學與動態測試教育部實重點實驗室,山西 太原 030051;3.中北大學 機電工程學院,山西 太原 030051)

?

高速彈載記錄儀存儲技術研究

劉雪飛1,2,馬鐵華1,2,劉廷輝3,尤文斌1,2,崔敏1

(1.中北大學 電子測試技術國家重點實驗室,山西 太原030051;2.中北大學 儀器科學與動態測試教育部實重點實驗室,山西 太原030051;3.中北大學 機電工程學院,山西 太原030051)

針對彈載記錄儀中NAND型Flash在負延時記錄時寫入速度低和可靠性差的問題,提出一種新型高速負延時存儲方法。在研究NAND型Flash存儲器存儲介質訪問原理的基礎上,采用當前成熟的高速率流水線存儲技術,設計了一種單通道雙控制總線的高速存儲結構,解決了當前具有負延時的彈載記錄儀存儲速度的瓶頸問題。以SOPC技術為基礎,將整個控制系統構建在單片FPGA上提高可靠性。試驗結果驗證了該存儲體系結構單通道寫入速度可達最高理論值40 MB/s,負延時容量、存儲總容量根據要求可設置。

負延時;記錄儀;高速存儲;NAND Flash

彈載負延時記錄儀可以將發射前初始姿態數據有效地存儲,從而記錄了完整的彈道姿態測試數據,保證數據的連貫性和完整性。隨著航空電子技術的高速發展,分辨率和采樣率大幅提高,且要求記錄全程彈道姿態數據,這樣對彈載負延時記錄儀的寫入速度提出了更高的要求[1-2]。傳統彈載記錄儀受到Flash先擦后寫、擦寫速度慢的限制,采樣頻率為1 MHz,已不能滿足高速存儲要求[3-5]。多通道NAND Flash的并行流水機制接口與有效配置數據緩存相結合的方法提高速率需要所有Flash芯片擦除完成才開始存儲[6-7]。從閃存轉換層(Flash Translation Layer, FTL)層面出發去提高系統的存儲速率,硬件資源消耗大,設計難,可靠性低[8]。

針對上述問題,筆者在研究NAND型Flash存儲器存儲介質訪問原理的基礎上,對當前成熟的高速率流水線存儲技術進行了改進,設計了一種單通道雙控制總線的高速存儲結構,以解決當前彈載負延時記錄儀傳輸速率瓶頸問題。以SOPC(System On a Programmable Chip,SOPC)技術為基礎,將整個控制系統構建在單片FPGA(Field Programmable Gate Array,FPGA)上提高可靠性。該結構可以在不改變硬件結構的基礎上,只更換NAND型Flash改變存儲容量,使該系統應用范圍更廣。

1 系統總體方案設計

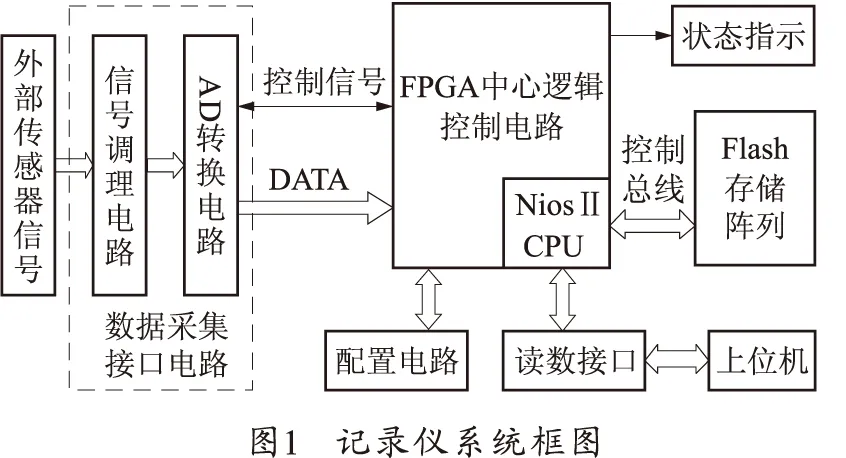

1.1系統結構組成

彈載負延時記錄儀結構組成如圖1所示,包括FPGA中心邏輯控制電路、數據采集接口電路、Flash存儲陣列、配置電路、讀數接口等。其中,在FPGA內用硬件描述語言VHDL設計內觸發、AD邏輯控制、數據編碼等功能;數據采集接口電路保證在有效地記錄被測信號的前提下不對被測信號造成任何干擾;Nios II軟核處理器是記錄儀核心控制器,控制與協調整個測試系統中各部分的協作與運行;Flash存儲陣列用于存儲數據。

使用 Quartus II 工具中的Megawizard Plug_In Manager設置相應的參數,構建8 KB的內部 FIFO 來緩存數字量,并采取半滿即讀的方式,即FIFO中存儲4 KB數據時,給出半滿標志HF。使用嵌入在Quartus II工具中的SOPC Builder系統集成工具,從IP組件中定義和建立Nios II嵌入式系統。加入Nios II處理器時,設置進入Nios系統模塊的時鐘頻率為50 MHz,Nios II處理器核的設置頁面如圖2所示。

Nios II軟核處理器具有3種處理器內核:經濟型內核、標準型內核和快速型內核。本記錄系統設計選擇快速型內核,擁有最高的程序執行速度,提高記錄儀數據采集實時性。

將Nios II軟核處理器和功能模塊集成到同一個現場可編程邏輯陣列FPGA上,構成一個可編程的片上系統,減少芯片使用數量,減小了電路板尺寸,提高了系統穩定性。

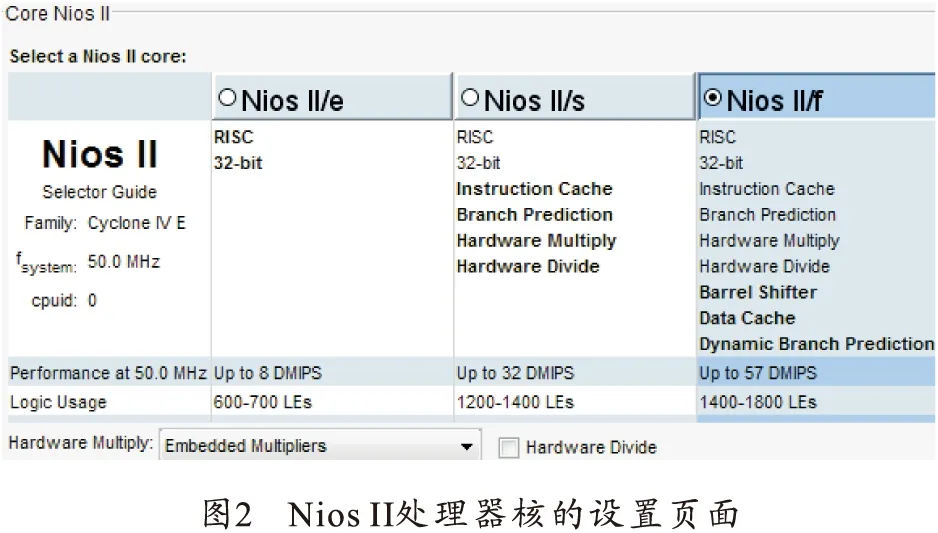

1.2記錄儀負延時實現原理

將Flash存儲總容量分為2個單元來實現負延時功能。根據設計要求第1單元總容量設為C,上電后,處于等待觸發狀態,存儲器保持循環記錄在第1個單元,儲存的內容不斷被擦除改寫;當觸發信號生效時,測試電路模塊觸發,首先將觸發地址寫入第2單元預設存儲單元,數據開始轉向第2單元進行順序記錄,當數據記錄達到滿容量時記錄儀停止采集數據,進入低功耗狀態,從而實現數據的負延時存儲[9-10]。負延時實現原理如圖3所示。

1.3讀數接口

讀數接口利用在Nios II系統中集成通用的UART內核,通過RS-232協議與外部命令交互。將USB讀數Flash存儲器中的數據讀取至上位機,并通過VB編寫的上位機軟件顯示給用戶。

2 存儲器寫入速度研究

NAND 型Flash存儲器是一種非易失性存儲器,具有生產工藝簡單、生產成本低、存儲密度大、功耗小及質量輕等優點,在電子設備中常用作數據存儲[11]。

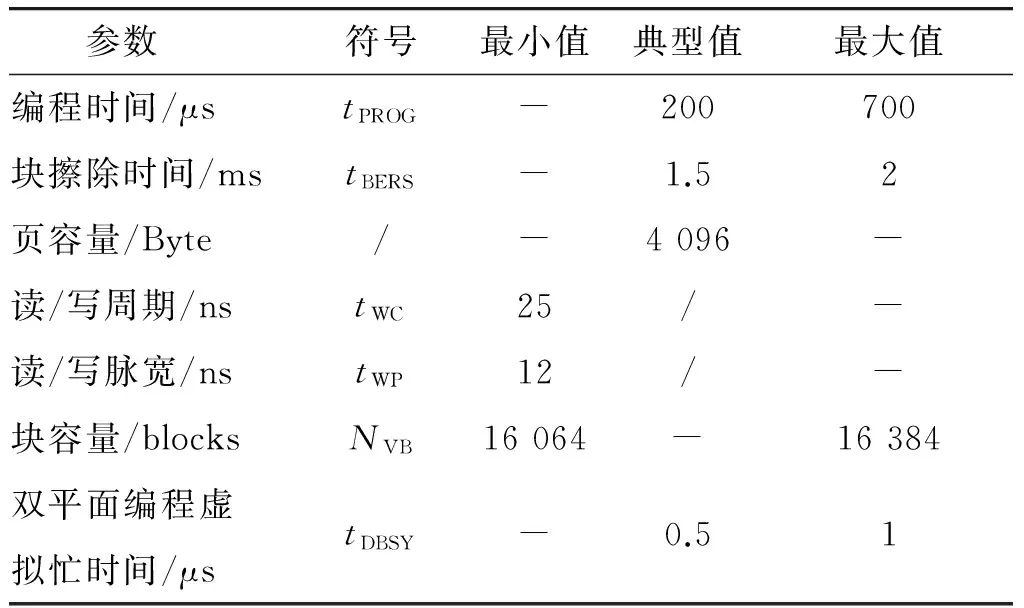

本記錄系統存儲介質選用三星公司的K9WBG08U1M存儲芯片,典型參數如表1所示。

表1 K9WBG08U1M存儲芯片的典型參數

K9WBG08U1M存儲芯片存儲操作、讀取操作基于頁為單位進行,命令字、地址、數據在寫使能上升沿寫入。擦除操作以塊為單位進行,其中1塊包含64頁。不需要外部干預自動完成編程過程,但編程時間內不能接收新的寫入命令。

2.1單平面操作

單平面操作即寫滿1頁后,芯片進入自動編程時間,完成編程操作后接著進行寫下一頁操作。當寫滿1塊后進行塊擦除操作,完成擦除操作后,接著進行寫操作。

數據加載1頁的峰值速度為

(1)

已加載的數據由緩沖區編程寫入到FlashMemory的時間為tPROG,頁編程周期由數據加載到Flash寫緩沖區和緊隨編程固化階段組成。負延時記錄儀存儲時需要擦除1塊寫1塊,則寫入FlashMemory的平均速度為

(2)

將表1的tPROG、tBERS、tWC代入式(2)得:

1.46MB/s≤v1≤2.27MB/s

即理論數據寫入速度在1.46~2.27MB/s之間。

2.2交替雙平面操作

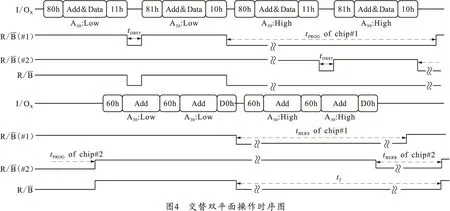

交替雙平面操作基于芯片內部不同平面可以單獨操作,能夠更好地利用頁編程時間。整個K9WBG08U1M存儲芯片分為片選chip#1和chip#2,每個片選有4個平面組成,定義chip#1的plane0和plane1為第0組,plane2和plane3為第1組,chip#2的plane0和plane1為第2組,plane2和plane3為第3組。當對第0組進行操作時,也可對其他3組分別執行寫命令操作、寫地址操作和寫數據操作。交替雙平面操作嚴格按照這個分組執行,時序圖如圖4所示。

由圖2可知,Nios II處理器指令執行時間可達57 DMIPS,執行指令的時間可以忽略不計,則單片Flash寫緩沖區、編程固化、交替雙平面擦除操作順序連續進行,寫入Flash Memory的平均速度為

(3)

式中,t2為交替雙平面擦除時間,實測可得:

t2≈tBERS

(4)

將式(4)、表1的tPROG、tWC、tBERS代入式(3)得:

5.27 MB/s≤v2≤7.76 MB/s

即理論數據寫入速度在5.27~7.76 MB/s之間。

3 存儲體系結構設計

3.1存儲結構

流水線是指將一個串行執行的任務分成若干可以順序執行的且又相互關聯的子任務,不同子任務之間可以并行執行的一種快速任務執行機制[12]。

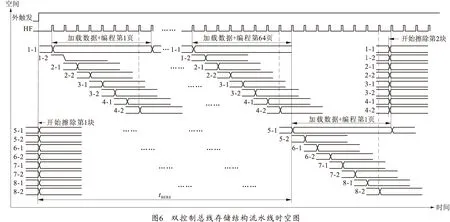

由K9WBG08U1M存儲芯片的典型參數可知,NAND Flash存儲器的編程時間一般在200~700 μs,但擦除1塊則需要1.5 ms左右。根據負延時實現原理和NAND Flash存儲結構,需要執行擦除1塊寫1塊的方法循環記錄數據。其中,塊擦除的存在很大程度上限制了Flash存儲器的寫入速度。為保證高速數據的完整可靠性,將高速率流水線存儲技術引入負延時記錄儀,隱藏擦除對存儲速度的影響,確保Flash在寫入數據前當前塊必須擦除完成,處于就緒狀態,設計了雙控制總線存儲系統架構,如圖5所示。

與存儲器控制邏輯單獨連接。命令、地址、數據分時復用8條數據信號線。

上述雙控制總線存儲結構不僅提高了存儲速度,而且降低了系統控制的復雜度。布電路板時,雙總線存儲結構可以縮短PCB板上的數據連線長度,減小數據與時鐘的相對位置,保證高速數據的可靠接收。

三星公司的NAND Flash存儲芯片封裝相同,容量不同。在不改變硬件結構的基礎上,只需要通過修改軟件程序即可改變存儲總容量、負延時容量和存儲速度。

3.2流水線工作

系統上電后,先對第1組Flash存儲器第0塊進行擦除,擦除完成后,使AD轉換器開始工作。此時切換控制總線對第2組Flash存儲器進行操作,發送擦除命令給第2組存儲器第0塊,命令發送完成后,第2組Flash存儲器執行內部擦除過程。切換控制總線,檢測到半滿標志HF后,開始流水線存儲數據,寫滿第1組存儲器第0塊后,切換到總線2,對第2組存儲器開始操作,此后交替進行擦除與寫操作。存儲數據時空如圖6所示。

閃存的1頁數據寫滿后,即可進行編程,切換到另一片進行寫數據[13]。采用流水線方式寫入數據,彈載試驗數據寫滿8塊所需時間為

T1=8×64×(4 096tWC+tRPOG)≈410.8 ms

(6)

留給每組閃存擦除的時間為

TBERS=T1?tBERS

(7)

由式(7)可以看出,寫滿當前組8塊后,下一組Flash已經處于就緒狀態可重新加載數據。

雙控制總線存儲結構寫入速度v2由公式(8)求得:

(8)

將表1的tPROG和tWC代入式(8)得:v2≤40 MB/s,即雙控制總線存儲結構寫入速度最高能達到40 MB/s。

4 試驗結果

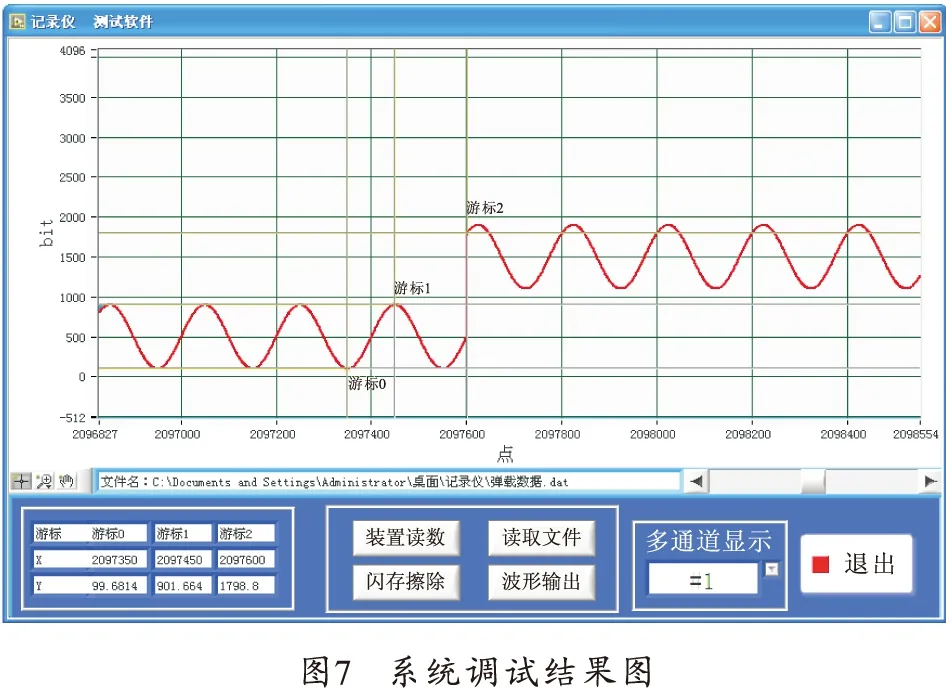

記錄系統設計完成后,在實驗室對其進行驗證。利用信號發生器向記錄儀輸入頻率為50 kHz,最小幅值為60 mV,最大幅值為560 mV的正弦信號。記錄儀采樣頻率設置為20 MHz。為了便于觀察,將負延時存儲長度設置為4 MB,觸發電平對應數字值設置為1 792。通過USB接口將采集數據讀回分析,結果如圖7所示。

從上位機顯示結果可以讀出,正弦信號在一個周期內橫坐標Δx內包含了200個點,縱坐標Δy=802 bit。其中,Δx表示系統采樣頻率與被采信號比值的一半,縱坐標中1 bit表示被采集信號的峰峰值為0.625 mV,可計算得讀取到存儲信號的頻率f,峰峰值Vp-p:

(9)

Vp-p=0.625×Δy=501.2 mV

(10)

由式(9)和(10)可知存儲的信號數據與信號源數值相符。

將正弦信號基線突發抬高模擬信號被觸發,信號滿足觸發條件后開始順序存儲第2個單元。由圖7可得觸發點的橫坐標為2 097 600,縱坐標為1 798.8。橫坐標每個點由2個數據形成,共有2 097 600點,計算可得4 195 200,即負延時為4 MB。縱坐標1 798.68大于觸發值1 792,系統觸發,之前為負延時。經過試驗驗證,系統能夠準確連續地采集信號。

5 結束語

筆者對Flash的固存技術進行了研究,設計了一種雙控制總線存儲結構,單通道寫入速度可達最高理論值40 MB/s。存儲總容量、負延時長度可根據要求設置。該技術有效提高了存儲系統的存儲效率和可靠性,滿足了負延時記錄儀在彈載試驗所需的要求,并可通過擴展Flash陣列滿足更高速度和更大容量的存儲要求。對從事這方面研究和工作的人員有一定的參考價值。

References)

[1]徐永剛,任國強,吳欽章,等.NAND Flash圖像記錄系統壞塊管理關鍵技術[J].紅外與激光工程,2012,41(4):1101-1106.

XU Yonggang, REN Guoqiang,WU Qinzhang,et al. Key technology of invalid block management in NAND flash-based image recorder system[J]. Infrared and Laser Engineering, 2012,41(4):1101-1106.(in Chinese)

[2]朱知博.基于NAND Flash的高速大容量存儲系統設計[J].現代電子技術,2011, 34(8):170-173.

ZHU Zhibo. Design of high-speed and mass storage system based on NAND Flash[J]. Modern Electronics Technique, 2011, 34(8):170-173.(in Chinese)

[3]張士飛.石油井下射孔壓力信息獲取系統的設計與研究[D].太原:中北大學, 2014.

ZHANG Shifei.The design and research of downhole perforating pressure information acquisition system[D].Tai-yuan:North University of China,2014.(in Chinese)

[4]時正,陳香蘭,紀金松,等.大容量NAND Flash文件系統中的地址映射算法研究[J].小型微型計算機系統,2010, 31(1):155-159.

SHI Zheng,CHEN Xianglan,JI Jinsong,et al. Space efficient mapping management for large-scale NAND Flash file system[J]. Journal of Chinese Computer Systems,2010,31(1):155-159.(in Chinese)

[5]裴峰.專用動態測試系統控制軟核的設計[D].太原:中北大學, 2013.

PEI Feng.The design of soft-core in special dynamic testing system[D]. Taiyuan:North University of China, 2013.(in Chinese)

[6]羅桂娥,康霞.固態硬盤性能優化研究與實現[J].計算機工程與應用,2015,51(1):43-48.

LUO Gui’e, KANG Xia. Research and implementation of solid state storage system-level performance optimization[J]. Computer Engineering and Applications,2015,51(1):43-48.(in Chinese)

[7]閆夢婷,安軍社.無縫壞塊處理與流水編程的NAND型內存控制器設計與實現[J].國防科技大學學報,2015,37(1):53-58.

YAN Mengting, AN Junshe. Design and implement of a NAND flash controller with pipelining program and non-missing invalid block handle[J]. Journal of National University of Defense Technology,2015,37(1):53-58.(in Chinese)

[8]彭軍,黎福海,羅旗舞,等.一種多通道并行固態存儲系統的設計與實現[J].計算機工程,2013,39(12):40-44,59.

PENG Jun, LI Fuhai, LUO Qiwu,et al. Design and implementation of a multi-channel parallel solid state storage system[J]. Computer Engineering,2013,39(12):40-44,59.(in Chinese)

[9]李亞娟,尤文斌,楊卓靜,等.無線控制的負延時存儲測試方法[J].探測與控制學報,2011,33(4):15-18,22.

LI Yajuan, YOU Wenbin, YANG Zhuojing,et al. Negative delay memory testing method based on wireless-control[J]. Journal of Detection & Control,2011,33(4):15-18,22.(in Chinese)

[10]原彥飛,尤文斌,李新娥.運用NAND閃存的負延時存儲測試系統[J].儀器儀表學報,2006,27(2):1517- 1518.

YUAN Yanfei, YOU Wenbin, LI Xin’e. NAND flash in negative delay stored testing and measuring system[J]. Chinese Journal of Scientific Instrument,2006,27(2):1517-1518. (in Chinese)

[11]盛江坤,邱孟通,姚志斌,等.NAND 型 Flash 存儲器總劑量效應實驗研究[J].原子能科學技術,2014,48(8):1502-1507.

SHENG Jiangkun, QIU Mengtong, YAO Zhibin,et al. Experimental study on total ionizing dose effect of NAND flash memory[J]. Atomic Energy Science and Technology,2014,48(8):1502-1507.(in Chinese)

[12]李釗,鄭紅,李業德.基于運行時間與資源消耗的流水線優化方法[J].儀器儀表學報,2014,35(9):2137- 2143.

LI Zhao,ZHENG Hong,LI Yede.Pipeline optimization design method based on runtime and area consumption[J]. Chinese Journal of Scientific Instrument,2014,35(9):2137-2143.(in Chinese)

[13]李亞娟,尤文斌,楊艷敏,等.無線監控沖擊波測試系統的研究[J].化工自動化及儀表, 2011, 38(11):1348- 1350.

LI Yajuan,YOU Wenbin,YANG Yanmin,et al. Study on wireless monitoring of shock wave test system[J]. Control and Instruments in Chemical Industry, 2011,38(11):1348-1350.(in Chinese)

The Research of High Speed Missile-borne Recorder Storage Technology

LIU Xuefei1,2,MA Tiehua1,2,LIU Tinghui3,YOU Wenbin1,2,CUI Min1

(1.National Key Laboratory for Electronic Measurement Technology, NUC, Taiyuan030051, Shanxi, China;2.Key Laboratory for Instrumentation Science & Dynamic Measurement,Ministry of Education, NUC, Taiyuan030051,Shanxi, China;3.College of Mechatronic Engineering, NUC, Taiyuan030051, Shanxi, China)

Aimed at the problem of low write speed and poor storage reliability of NAND flash in missile-borne recorder during negative delay recording, a new high-speed negative delay storage method is presented. On the basis of the study of the principle of access to the storage medium in NAND flash memory, the method of a currently mature technology of high-speed pipeline storage was adopted through the design of a high-speed structure of single channel dual bus control, which solved the bottleneck problem of storage speed of missile-borne recorder with negative delay. Based on SOPC (System On a Programmable Chip) technology, the whole control system was structured on a single FPGA (Field Programmable Gate Array) for the improvement of reliability. The test results show the write speed in the storage architecture of single channel could reach the highest theoretical value of 40MB/s. In the mean time, the negative delay capacity and the total storage capacity could be set according to the requirements.

negative delay; recorder; high-speed storage; NAND Flash

10.19323/j.issn.1673-6524.2016.02.006

2015-05-18

山西省青年科技研究基金(No.2013021015-1)

劉雪飛(1989—),男,碩士研究生,主要從事動態測試與智能儀器技術研究。E-mail:15135165175@126.com

TP73

A

1673-6524(2016)02-0025-06