三值光學計算機解碼器中并行感光陣列的設計

石也強,金翊,歐陽山,展豪君

(上海大學計算機工程與科學學院,上海 200444)

三值光學計算機解碼器中并行感光陣列的設計

石也強,金翊,歐陽山,展豪君

(上海大學計算機工程與科學學院,上海 200444)

介紹了針對數千位的三值光學計算機解碼器而設計的一款并行感光陣列。在整體規劃上,采用了將16個感光單元電路集成為一個感光模塊,再用多個感光模塊拼接成實用的并行感光陣列之策略.設計的感光單元電路將三值光學處理器一個像素輸出的光信號轉換成對應的電信號,一個感光模塊將三值光學處理器16個像素輸出的光信號并行轉換成對應的電信號,感光陣列將三值光學處理器的數千個像素輸出的光信號并行轉換成對應的電信號.設計的感光模塊封裝外形解決了拼裝成大規模感光陣列的問題.該模塊為三值光學計算機提供了一個成本低、方便維護及更換的并行光電器件.最后介紹了對感光模塊中電路的實驗研究和對模塊外形拼接性能的實物樣板測試,實驗證實了所設計電路的功能有效性和性能穩定性,樣板測試表明該設計的感光模塊封裝外形適于拼接.

光電轉換;并行感光陣列;三值光學計算機;模塊設計

隨著可重構三值光學處理器在理論和實驗上的成功[1-6],研制實用的三值光學計算機成為該領域的一個關注點[7-8],于是對這種新型計算機各部件的探索正在逐步從其工作原理和構造原理的研究轉向精密設計方面的研究,即通過對部件的精密設計來提高整機性能并達到實際可用的水平.在這個背景下,2004—2013年金翊等[9-15]對三值光學計算機的光電信號轉換部件——解碼器的感光陣列進行了全新設計,即以三值光學計算機前期實驗系統中建立的解碼器理論和技術為基礎,在延續了原技術中的電路、感光原理以及液晶結構的基礎上,針對構建全并行解碼器這一目標,對現有的技術進行了重大改進.

在三值光學計算機的研究過程中,以往的工作重心都集中在計算功能的實現上[7-8,16-21],面對整機性能的追求才剛剛開始,因此其解碼器的光電轉換部件至今仍將手機攝像頭用作替代品.然而,攝像頭的工作速度以滿足視覺為目標,鑒于視覺要求的幀頻遠遠低于圖像傳感器處理一幀圖像數據的速度,故攝像頭都采用行掃描工作方式,即攝像頭都采用對圖像像素依次處理的串行技術.但是,光學計算機要求對圖像的所有像素同時進行處理,故用作替代品的攝像頭嚴重影響了三值光學計算機的整機性能.目前在國內外對并行光電轉換陣列的研究比較少[22-24],少量成品的價格比較昂貴,而且封裝外形完全不適合在三值光學解碼器中使用,為此從科學研究、經濟效益和封裝外形等方面考慮,研究用于三值光學計算機解碼器的并行光電轉換器件很有必要.針對這一需求,本研究提出了一種適用于三值光學計算機解碼器的并行感光陣列,包括設計了該并行感光陣列的工作電路、單元芯片的集成規模、單元芯片的封裝外形、單元芯片的內部電路、單元芯片的外部引腳配置、用單元芯片拼裝成大規模并行感光陣列等.本研究通過必要的實驗證實了所設計的并行感光陣列的有效性和適用性,并報道了這項研究的核心內容和實驗情況.

1 并行感光陣列的設計要點

1.1 設計方案的選擇

本設計的總體目標是研發全部像素并行工作的、易維護且造價低的感光陣列.

為達到這個目標,最直觀的設計方案是制作一整塊與液晶板大小相同的感光陣列.以三值光學計算機實驗系統使用的液晶板為例,需要制作一塊24×24大小的陣列.該方案雖能達到全部像素并行工作的目的,但一個器件中包含很多相同的單元電路,這存在3個問題:①成品的需要量很小,導致成本很高;②單個陣列中包含的像素越多,單像素損壞的概率就越高,而單像素損壞就會導致整個陣列不可用,于是成品的損壞率就很高,這進一步提高了成本;③使用過程中有一個像素點損壞就需要更換整個陣列,當更換了整個感光陣列后,系統的每個像素都需要重新設定工作電壓,從而使系統維護相當困難.故這個方案是不可行的.

第二種方案是將每一個感光電路制作成一個芯片,即每個芯片僅包含一個感光像素.顯然,對這種小芯片的需求量會很大,每個小芯片的成本就會比較低,而且一個感光像素損壞時只需更換一個小芯片,對其他像素沒有產生影響,便于維護.但是,小芯片的體積很小,對制作工藝的精度要求較高,而且制作一塊24×24大小的陣列就需將576個小芯片拼接起來,導致拼接大感光陣列很難.因此這個方案也不可行.

第三種設計方案是取前兩種設計方案中的合理部分,綜合考慮電路制作的難易、感光陣列的成本、拼接的可實現性和維護難度等因素,構造包含多個感光像素的單元芯片,并使單元芯片的體積和外形便于拼接.這樣的單元芯片有便于制作、成本較低、方便拼接、易于維護等優點.鑒于此,本研究選擇了這個方案.

在第三種設計方案的指導下,本研究選定一個單元芯片中包含4×4個感光像素.主要原因有以下3個方面:①為方便模塊的拼接與擴充,將模塊的形狀設計為方陣;②為了便于利用現有的常規器件,如四運算放大器LM324、16位鎖存器,故方陣的階數最好為2的冪數;③綜合考慮陣列的幾何尺寸大小、目標像素的大小以及模塊加工制作的難易程度、拼接成大感光陣列的方便性和維護的簡便性.

1.2 關鍵技術

為制作合適的感光模塊,必須解決的關鍵技術如下.

(1)當被測圖像上任一個像素的亮度超過亮閾值時,對應感光單元輸出確定的高電平值;而當被測圖像任一個像素的亮度低于暗閾值時,對應感光單元輸出確定的低電平值.

(2)感光陣列的所有感光單元同時曝光,同時輸出探測電平.

(3)制作包含適當數量感光單元的并行感光模塊,并用這種感光模塊拼接成大規模的感光陣列.

如果能解決關鍵技術(1),則允許三值光學處理器輸出光信號的亮度在一個較大的范圍內變化,于是就降低了對光學處理器輸出圖像的亮度均勻性要求,進而降低了對光源穩定性的要求;也降低了對液晶旋光角度的精準性要求,進而降低了對液晶控制電路的精度要求.這就使得三值光學計算機整機更容易達到穩定的工作狀態,且降低制造精度和研發成本.

解決這個問題的設計要點是:用一個感光管、一個運算放大器(以下簡稱運放)和一位鎖存器構成一個感光單元.在感光單元中,感光管的輸出端接運算放大器的輸入端,運放的輸出端接鎖存器的輸入端,鎖存器的輸出端為該感光單元的輸出信號.在這個設計中,感光管用來探測光學處理器中一個像素的光亮度,運放將感光管的輸出放大到足以推動鎖存器輸入端的電平,而鎖存器對運放的輸出電平進行整形,使該感光單元的輸出電平符合TTL電平規范.

關鍵技術(2)是針對并行感光陣列的基本要求,解決這個問題的設計要點是:將所有感光單元中鎖存器的鎖存有效端并接在一起,用一個信號控制所有感光單元同時探測光學處理器各像素的輸出光強;并將所有感光單元中鎖存器的輸出有效端并接在一起,用一個信號控制所有感光單元同時輸出探測電平.

關鍵技術(3)的作用有3點:①制作數量較多的小感光模塊比制作一個大感光陣列的成本低很多;②用小感光模塊可以拼接成長寬尺寸不同的多種并行感光陣列,以適應三值光學處理器使用不同規格的液晶陣列;③當感光陣列局部損壞時,只需調換損壞的幾個感光模塊即可修復整個感光陣列,從而延長系統的壽命,降低維護成本.

解決這個問題的設計要點是:將16個感光單元排成4×4方陣構成一個感光模塊,這16個感光單元的一位鎖存器合并成一個16位鎖存器;該模塊的一面均勻排列4×4個感光管,另一面排列24根電接觸針,其中16根為16位鎖存器數據的輸出針,一根為鎖存信號,一根為輸出有效信號,兩根電源,兩根地線,兩根未用(計劃用于防止插座接反);該模塊的4個側面為燕尾形互接齒,以方便拼接成感光陣列時感光模塊間相互嚙合.

2 并行感光陣列的詳細設計

2.1 電路設計

(1)感光單元設計.

本研究采用的CMOS型感光管是一種光控三極管,當其光控端接收到光照時,它的PN結電阻減小,借此實現光照信號強度對PN結上電信號強度的控制.但光電管允許通過的電流強度在微安量級,通常用運放電路將這個弱信號放大到可以被后續電路識別的程度,本研究也采用這一設計思想,具體電路設計如圖1所示.圖1中感光管為CMOS型光電三極管,運放采用負反饋反向比例放大電路,鎖存器為一位D觸發器.本研究用G、L和D分別表示感光管和鎖存器.

圖1的工作原理可以簡述為照射到感光管上的光信號越亮,感光管的導通性就越好,則運放兩個輸入端的信號差就越大,運放的輸出電壓就越高,當光照強度超過一個較高的亮度時,運放輸出電壓就會超過3.5V,這時對于鎖存器的輸入端就是高電平狀態,鎖存器就存儲“1”值;而當光照強度低于一個較低的閾值時,運放輸出電壓就會遠低于3.5V,這時鎖存器的輸入端處于低電平狀態,它就存儲“0”值.用這個電路去探測光學處理器一個像素的輸出光強,當該像素輸出亮信號時,鎖存器中就存儲到“1”值,而當該像素輸出暗信號時,鎖存器中就存儲到“0”值.于是圖1的電路將光學處理器一個像素的輸出光信號轉換成一位的電信號,故本研究稱它為感光單元電路.

圖1的工作時序由鎖存器的鎖存有效端LE和輸出有效端OE控制,當給LE施加有效信號時,鎖存器將運放的當前輸出值保存在鎖存器中,即完成探測光強的操作,當給OE施加有效信號時,鎖存器將保存的值輸出.于是外界通過適時給LE和OE施加有效信號,控制感光單元的操作時序.另外,鎖存器輸出標準的TTL電平,這意味著對運放的輸出信號進行了整形,于是只要照射感光管的光強度超過較大閾值[25-26],即使光強有波動也不會影響感光單元電路輸出“1”;同理,暗光狀態有波動也不會影響感光單元電路輸出“0”,因此這個電路對光學處理器輸出光信號強度的容錯能力較高.

圖1 感光單元電路Fig.1 Photoreceptor cell circuit

(2)感光模塊設計.

圖1給出的感光單元電路能夠探測光學處理器的一個像素輸出的光信號,對于有數百萬個像素并行工作的光學處理器[27-28],每個像素都需要一個感光單元電路,這數百萬個感光單元電路將按照光學處理器像素的排列方式組成感光陣列.由于光學處理器的像素面積很小,這些感光單元電路必須采用集成化制造技術構成一個與光學處理器對應的大規模集成感光陣列,本研究就是為構建這種大規模集成感光陣列奠定技術和結構研究的基礎.因此,必須考慮用盡量低的代價來驗證用圖1給出的感光單元電路排成的感光陣列的功能有效性和制造的可行性.為達到這一目標,考慮在此期間三值光學處理器還保持著較大的像素面積以方便人眼直接觀察,本研究采取用較少的感光單元構成一個小規模集成度的感光模塊,再用許多感光模塊拼接成感光陣列之策略.由于感光模塊的集成度較小,其研發成本和風險比研發感光陣列低很多;由于需要的數量較多,每個感光模塊的制作成本就比較低;由于感光陣列用很多感光模塊拼接而成,當感光陣列局部損壞時,只需更換個別感光模塊即可,從而降低了實驗研究的成本和系統維護成本,因此這個策略滿足本研究的需要.

鑒于目前三值光學處理器一個像素的尺寸為3.98 mm×3.28 mm[29],本設計的感光模塊包含排成4×4方陣的16個感光單元電路,圖2給出了感光模塊的內部電路圖.為了進一步減小感光模塊的集成度,也為了能對運放輸出電平進行更細致的研究和利用,圖2中將16個感光單元的一位鎖存器集中在一個16位的常規鎖存器中,并將該存儲器設置在感光模塊之外,于是這個鎖存器可以使用常規芯片,進一步降低研究成本.由于16個感光單元的一位鎖存器集中在一個鎖存芯片中,它們的OE端在鎖存芯片內連在一起,LE端也連在一起,于是16個感光單元的操作時序完全同步.

圖2 感光模塊電路Fig.2 Photoreceptor module circuit

在使用中,每個感光模塊都將被貼附在三值光學處理器的輸出畫面上,每一個感光管正好對正光學處理器的一個像素.于是,每個感光模塊并行探測光學處理器16個像素的光強度并同時輸出探測結果,整個感光陣列就同時探測光學處理器每個像素輸出的光信息,并同時輸出探測結果,成為實現三值光學計算機并行解碼器的基本器件.

2.2 感光模塊的封裝設計

用多個模塊拼接成實用的感光陣列的設計思想可以有效降低研發成本、制作成本和維護成本.但模塊的幾何尺寸應既方便模塊電路和引腳的配置,又便于每個感光單元對正光學處理器的一個像素,而模塊的外形也應既方便相互拼接,又便于相互嚙合,避免松散,為此本研究詳細設計了感光模塊的封裝.

(1)感光模塊尺寸.

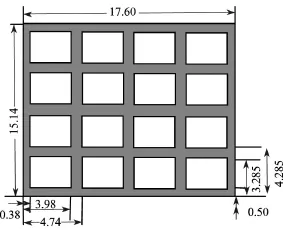

設計感光模塊外形的最大幾何尺寸為長17.60 mm、寬15.14 mm,高度由芯片制作工藝確定(見圖3).

設計感光模塊的正面為光線射入面,要求鏡面平整且透光性好,各部分的具體尺寸如圖3所示.圖3中的白色部分對應于光學處理器輸出面上的像素面積,灰色部分對應于光學處理器輸出面上像素之間的隔光帶,每一個白色區域的中部安置一個感光單元的光電管,為提高感光管的可靠性,在每個白色區域中安放并聯的3個感光管,只要有一個感光管能正確感知光學處理器像素的輸出光強,該感光單元即可正常工作.為充分降低相鄰液晶點對感光陣列的影響,液晶像素的隔光帶必須正對感光模塊中感光管之間的間隔,并且制作時盡量將感光管集中在圖3中白色區域中心,以增大隔光帶的尺寸,降低相鄰液晶點的相互影響.

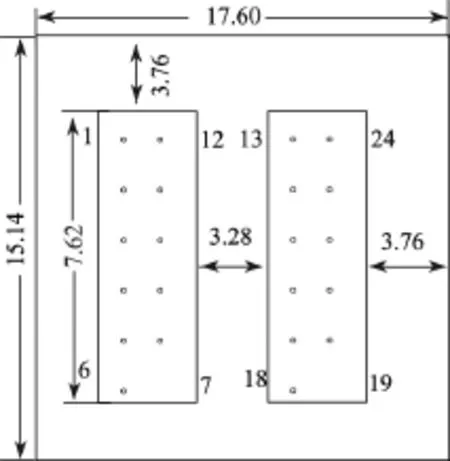

設計感光模塊的背面安裝垂直插針,用于電連接.參考派睿公司M50-3500622型號的排針規格,設計感光模塊安裝兩個相同的雙排直針A和B,它們在感光模塊上的定位參數如圖4所示.排針的幾何參數為針距1.27mm、行距1.27mm,針直徑為0.50mm,電器參數為額定電流1A、絕緣電壓為500V,環境溫度:[-40,105]?C.

圖3 感光陣列模塊尺寸大小(mm)Fig.3 Photoreceptor array module size(mm)

(2)模塊電接觸引腳設計.

感光模塊共有24根插針,各針的編號如圖4所示,各針的功能定義如表1所示,其中O1~O16是16個感光單元輸出的電信號,在本設計中為各個運放輸出的電平.第7號和第19號引腳沒有定義,要求對應的插座上的這兩個位置為空,以防止插反.

圖4 感光陣列模塊引腳設計(mm)Fig.4 Photoreceptor array module pin design(mm)

表1 感光陣列模塊引腳功能定義Table 1 Pin function definition of photoreceptor array module

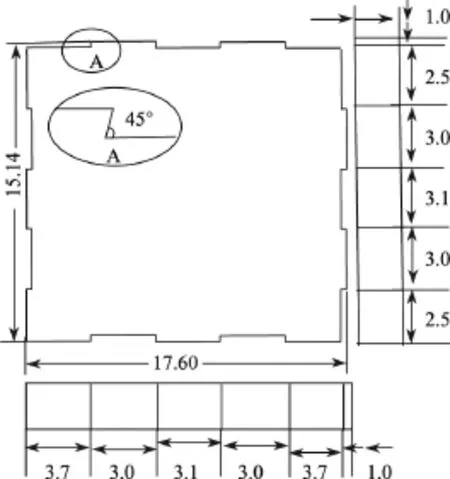

(3)模塊外形設計.

為方便將感光模塊拼接成感光陣列,在感光模塊的4個側面設計了燕尾形互接齒,具體形狀和尺寸如圖5所示.

圖5 感光陣列模塊封裝外形三視圖(mm)Fig.5 Photoreceptor array module encapsulation shape(mm)

3 實驗

3.1 電路原理實驗

3.1.1 實驗環境搭建

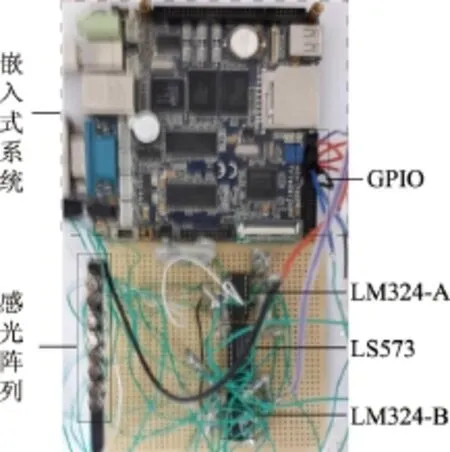

圖6中的實驗電路板上焊裝有8個如圖1所示的感光單元電路,其中感光管采用與感光單元中感光材料質地和結構均相同的CMOS管,以真實驗證感光單元的工作情況;各電阻的值分別為R1=200?,反饋電阻Rf=50 M?,平衡電阻R2=3 k?;8個運算放大器采用兩個LM324芯片來實現,記為LM324-A和LM324-B,每片集成了4個運算放大器,每個運放負責放大一個感光管的輸出信號;8個一位鎖存器采用一片LS573來實現,LS573中集成了8位鎖存器;還焊裝了一個12針插口,用于連接嵌入式系統.實驗電路板上各元件的主要連線如圖7所示.

在圖7所示的連接中,鎖存器LS573的輸出有效端OE通過H12的8號引腳與嵌入式系統的GPB1相連,于是當嵌入式系統在GPB1輸出低電平時,控制LS573輸出鎖存值,即控制鎖存器輸出的嵌入式系統指令為rGPBCON=0x10,rGPBDAT=0x01;同理,LS573的鎖存有效端LE通過H12的9號引腳與嵌入式系統的GPB2相連,于是當嵌入式系統在GPB2輸出低電平時,控制LS573鎖存輸入值,即控制鎖存的嵌入式系統指令為rGPBCON=0x04,rGPBDAT=0x03.在這個連接下,通過PC機的ADS開發環境向嵌入式系統發出的實驗命令由一個鎖存命令和經過延時t后的一個鎖存器輸出指令組成:rGPBCON=0x10,rGPBDAT=0x03,delay(100),rGPBCON=0x04,rGPBDAT=0x01.

圖6 感光陣列(8位)實驗照片Fig.6 Photoreceptor array(8 bits)experiment device photo

3.1.2 實驗過程

為了能夠全面地測試與驗證并行感光陣列的功能,本設計的實驗步驟如下.

(1)用散射光照亮8個感光管,使0號感光單元的運放輸出電平達3.5V(使用DT-9205A型號數字萬用表測量);發出實驗命令;在PC上保存收到的鎖存器輸出值.理論值為FF.

(2)遮擋對8個感光管的光照;發出實驗命令;在PC上保存收到的鎖存器輸出值.理論值為00.

(3)遮擋對1、3、5、7號感光管的光照;發出實驗命令;在PC上保存收到的鎖存器輸出值.理論值為55.

女人很漂亮,約莫二十歲出頭,高挑的個頭,瓷白的皮膚。一條曵地的白色紗裙像一朵盛開的白色薔薇朝下鋪陳開放著。

(4)遮擋對0、2、4、6號感光管的光照;發出實驗命令;在PC上保存收到的鎖存器輸出值.理論值為AA.

(5)降低散射光亮度,使0號感光單元的運放輸出電平約3.0V;執行實驗步驟(1)~(4).

(6)降低散射光亮度,使0號感光單元的運放輸出電平約2.5V;執行實驗步驟(1)~(4).

(7)降低散射光亮度,使0號感光單元的運放輸出電平約2.0V;執行實驗步驟(1)~(4).

(8)根據上述實驗情況,調整散射光亮度,重復實驗步驟(1)~(4),找到能正確測定光信號的光強度值所對應的0號感光單元的運放輸出電平.

(9)根據步驟(8)的實驗結果定出光亮度的高閾值,執行實驗步驟(1)~(4),重復10遍,每次重復間隔2min.

(10)根據步驟(8)的實驗結果定出光亮度的低閾值,執行實驗步驟(1)~(4),重復10遍,每次重復間隔2min.

3.1.3 實驗數據及分析

步驟(1)的目的是為了判斷感光陣列能否正確地探測到光強度的亮狀態;步驟(2)是為了判斷感光陣列能否正確地探測到光強度的暗狀態;步驟(3)和(4)是為了判斷液晶相鄰像素的亮暗信息是否影響感光陣列的工作;步驟(5)~(8)的設計目的是為了找出感光陣列的亮暗閾值;步驟(9)是為了驗證感光陣列的亮閾值是否正確;步驟(10)是為了驗證感光陣列的暗閾值是否正確.

根據光電轉換原理,目標像素的光強度用0號感光單元的運放輸出電壓表示.這里由于篇幅所限,表2中只列出了上述實驗過程中步驟(1)和(3)的實驗數據.步驟(2)的實驗數據全部為0,步驟(4)和步驟(3)相似,略.

圖7 感光陣列(8位)實驗圖Fig.7 Photoreceptor array(8 bits)experimental schematic diagram

表2 實驗數據Table 2 Experimental data

分析實驗數據可知,在0號感光單元的輸出電壓值為[0,1]V之間,不管是否用黑色物質擋住感光陣列,測試單元的輸出電信號的值均為0,與理論值一致;0號感光單元的輸出電壓值在[2.0,3.5]V之間時,如果感光管被黑色的不透光物體遮擋住,測試單元輸出的電信號為0,否則為1,與理論值一致;當0號感光單元的輸出電壓值在[1,2]V時,測試單元輸出的電信號有時為1,有時為0,光電轉換的結果是不穩定的,該區間對應的光強度介于暗閾值與亮閾值之間.

3.1.4 實驗結論

(1)能正確測定光信號的光強度亮閾值所對應的0號感光單元的運放輸出電平為2V;暗閾值所對應的0號感光單元的運放輸出電平為1V.

(2)當光強度超過選定的高閾值時,各感光單元的輸出值在反復10次的實驗中都為1,與理論值一致.

(3)當光強度低于選定的低閾值時,各感光單元的輸出值在反復10次的實驗中都為0,與理論值一致.

(4)當光強度介于暗閾值與亮閾值之間時,隨著光強度的降低(電壓值的下降),輸出1的能力明顯減弱,輸出0的能力明顯增強.

(5)步驟(3)和(4)的實驗結果表明,相鄰液晶點像素之間的亮暗對感光陣列沒有影響.

3.2 外形及拼接實驗

為了驗證模塊設計中外形封裝的正確性,本研究采用厚度為2mm的雙色塑料板制作了感光模塊的1∶1外形樣板,用這種樣板進行了拼接實驗.操作容易,拼接效果良好,拼接實物照片如圖8所示.

圖8 感光陣列模塊拼接示意圖Fig.8 Photoreceptor array module splicing diagram

4 并行解碼器與串行解碼器的對比

三值光學計算機解碼器的基本功能是將光學處理器的輸出結果從光信號轉換為電信號,其核心部件是光電轉換器件,將感光陣列作為光電轉換器件的解碼器稱為并行解碼器,將CMOS手機攝像頭作為光電轉換器件的解碼器稱為串行解碼器.雖然二者的解碼過程比較類似,但在性能上卻有較大區別.

首先,在串行解碼器中,CMOS攝像頭工作速度以滿足視覺為目標,通常為30幀/s,鑒于視覺要求的幀頻遠遠慢于圖像傳感器處理一幀圖像數據的速度,故攝像頭都采用行掃描工作方式,即采用攝像頭對圖像像素依次處理的串行技術,因此采用該器件的解碼器也是串行的.解碼的每個數字電信號的寬度為8位或10位,進而影響光學解碼器的工作速度.

本設計的感光陣列能夠全并行地探測到三值光學處理器對應像素的光狀態,并且同時將光電轉換結果進行輸出.三值光學處理器的信號光源與SI-PIN光電二極管的光譜特性相符合,均在可見光與紅外光之間;光電二極管響應時間的數量級為10-6s,低于液晶的響應時間(10-3s)[27-28].另外,感光陣列中使用的光電二極管具有信號噪聲低、線性性能好、價格低廉、使用壽命長、外加電壓低、功耗小和穩定可靠等優越的特性,能滿足光學解碼器的全并行、低功耗和可靠性的需求,故感光陣列更適合用作三值光學解碼器中的光電轉換器件.

5 結束語

隨著三值光學計算機整機實驗系統SD11的建成,快速提高三值光學計算機的性能成為下一個研究重點.在當前的三值光學計算機實驗系統中,制約提高運行速度的主要因素之一是解碼器感光部分采用了串行工作的攝像頭,因此研發并行工作的解碼器感光部件成為提高三值光學計算機性能的關鍵技術之一.本研究為解決這一問題設計了一款并行感光陣列器件.該設計采用將16個感光單元電路集成為一個感光模塊,再用多個感光模塊拼接成實用的并行感光陣列之策略.由于感光模塊的集成度低而用量大,因此大幅度降低了研發成本,提高了感光陣列的可維護性;而且感光模塊的幾何尺度適中,能容納足夠多的電路引腳,便于保存、手持、安裝.經過實驗驗證,本設計的感光單元電路功能達到要求,工作可靠;感光模塊外形合理,拼接方便,相對位置穩定可靠.本研究為廠家生產這種并行感光模塊奠定了理論基礎和提供技術支持,為三值光學計算機構造并行解碼器解決了關鍵技術問題.

[1]JIN Y,HE H C,L¨U Y T.Ternary optical computer principle[J].Sci China Ser F-Inf Sci,2003, 46(2):145-150.

[2]JIN Y,HE H C,L¨U Y T.Ternary optical computer architecture[J].Phys Scr,2005,T118:98-101.

[3]金翊.走近光學計算機[J].上海大學學報(自然科學版),2011,17(4):401-411.

[4]YAN J Y,JIN Y,ZUO K Z.Decrease-radix design principle for carrying/borrowing free multivalued and application internary optical computer[J].Sci China Ser F-Inf Sci,2008,51(10):1415-1426.

[5]JIN Y,WANG H J,OUYANG S,et al.Principles,structures,and implementation of reconfigurable ternary optical processors[J].Science China Information Sciences,2011,54(11):2236-2246.

[6]王宏健,金翊,歐陽山.一位可重構三值光學處理器的設計和實現[J].計算機學報,2014,37(7):1500-1507.

[7]張茜,金翊,宋凱,等.三值光學計算機MPI編程技術在超算集群中的使用[J].上海大學學報(自然科學版),2014,20(2):180-189.

[8]李梅,金翊,何華燦,等.基于三值邏輯光學處理器實現向量矩陣乘法[J].計算機應用研究,2009, 26(8):2839-2841.

[9]YAN J Y,JIN Y,SUN H.Study on the feasibility of coding and decoding multi-bit ternary optical signal used in ternary optical computer[J].Comput Eng,2004,30(14):175-177.

[10]SUN H,JIN Y,YAN J Y.Research on principle of coder and decoder in ternary optical computer by experiment[J].Comput Eng Appl,2004,40(16):82-83,136.

[11]JIN Y,GU Y Y,ZUO K Z.Theory,technology and implementation of ternary optical computer[J].Science Sinica,2013,43(2):275-286.

[12]嚴軍勇,金翊,孫浩.三值光計算機多位編碼器與解碼器的可行性實驗研究[J].計算機工程,2004, 30(14):175-177.

[13]ZUO K Z,JIN Y,XUE T,et al.Study on image acquiring system based on decoding simulator of ternary optical computer[J].Semicond Optoelectron,2008,29(6):949-952.

[14]XUE T,JIN Y,ZUO K Z.Data acquiring control system for decoder of tema optical computer[J].Comput Eng Des,2009,30(17):3932-3933.

[15]LIU S B,PENG J J,JIN Y,et al.Technology of synchronizing decoder with operator in TOC experimental system[J].Comput Eng Des,2010,31(16):3565-3568.

[16]JIN Y,HE H,AI L.Lane of parallel through carry in ternary optical adder[J].Sci China Ser F-Inf Sci,2005,48(1):107-116.

[17]JIN Y,SHEN Y F,PENG J J,et al.Principles and construction of MSD adder in ternary optical computer[J].Sci China Ser F-Inf Sci,2010,53(11):2159-2168.

[18]沈云付,潘磊,金翊,等.三值光學計算機一種限制輸入一步式MSD加法器[J].中國科學E輯(信息科學),2012,42(7):869-881.

[19]LIU Y,PENG J,CHEN Y,et al.A new carry-free adder model for ternary optical computer[C]// Distributed Computing and Applications to Business,Engineering and Science(DCABES),2011 Tenth International Symposium on IEEE.2011:64-68.

[20]SONG K,YAN L.Design and implementation of the one-step MSD adder of optical computer[J].Applied Optics,2012,51(7):917-926.

[21]PENG J J,SHEN R,JIN Y,et al.Design and implementation of modified signed-digit adder[J]. IEEE Transactions on Computers,2010,53(11):2159-2168.

[22]初寧,曹立軍,黃威.基于光照強度的PIN光電二極管響應時間分析[J].傳感技術學報,2013,26(1):34-37.

[23]戴競,張敏明,何巖,等.新型液晶光學相控陣的特性研究[J].光子學報,2014,43(2):61-66.

[24]秦臻,林祖倫,葉祥平,等.CMOS圖像傳感器光電二極管模型[J].電子器件,2014(6):1039-1042.

[25]LEI L,JIN Y.Auto-measurement of grayscale threshold of ternary optical computer's decoder[J].Comput Eng Des,2012,33(1):233-237.

[26]雷鐳,金翊.三值光學計算機解碼器亮度閾值自動測定技術[J].計算機工程與設計,2012,33(1):233-237.

[27]金翊,歐陽山,宋凱,等.三值光學處理器的數據位管理理論和技術[J].中國科學E輯(信息科學), 2013,43(3):361-373.

[28]金翊.三值光計算機高數據寬度的管理策略[J].上海大學學報(自然科學版),2007,13(5):519-523.

[29]諶章義.千位三值光學處理器理論、結構和實現[D].上海:上海大學,2010.

本文彩色版可登陸本刊網站查詢:http://www.journal.shu.edu.cn

Design of parallel photosensitive array in ternary optical computer decoder

SHI Yeqiang,JIN Yi,OUYANG Shan,ZHAN Haojun

(School of Computer Engineering and Science,Shanghai University,Shanghai 200444,China)

This paper discusses the design of a parallel photosensitive array for a decoder in a thousand-bit ternary optical computer.The strategy is to make a parallel module with 16 photosensitive pixels and circuits,and joint some modules into a utility parallel photosensitive array.Each module transforms 16 three-state optical signals from a ternary optical processor into 16 two-state electoral signals concurrently.A parallel photosensitive array then transforms thousands of three-state optical signals into electoral signals concurrently.Thus the module becomes a low-cost,maintainable and replaceable parallel photoelectric device.Experiments are performed to verify stability and correctness of the photosensitive pixels and their circuits.A test on four samples of the module outline shows that splicing a large-scaled photosensitive array with lots of modules is convenient.

photoelectric conversion;parallel photosensitive array;ternary optical computer;module design

TP 311

A

1007-2861(2016)04-0449-12

10.3969/j.issn.1007-2861.2015.01.004

2014-12-17

國家自然科學基金資助項目(61073049);國家自然科學基金青年基金資助項目(61103054);上海市教委科研創新項目(13ZZ074,13YZ005);上海市自然科學基金資助項目(13ZR1416000);上海高校青年教師培養資助計劃項目(ZZSD13035)

金翊(1957—),男,教授,博士生導師,研究方向為三值光學計算機和計算機體系結構. E-mail:yijin@shu.edu.cn