32位低功耗高速乘法器設計?

張明英

(西安外事學院,西安710077)

32位低功耗高速乘法器設計?

張明英

(西安外事學院,西安710077)

采用Verilog HDL硬件描述語言,設計了一個高性能、低功耗的32位定點乘法器。該乘法器通過對基4布斯算法、4∶2壓縮器算法及最終加法器的優(yōu)化設計,進一步提高了乘法的運算速度。另外,在設計中加入了操作數(shù)隔離、門控時鐘等低功耗設計技術,從而大幅度減少了電路功耗。采用SMIC 0.18μm CMOS工藝,使用Synopsys的Design Compiler工具對電路進行邏輯綜合。結(jié)果顯示,最壞情況下的時間延遲為3.9ns,系統(tǒng)時鐘頻率可達256MHz,功耗小于37mW。

低功耗;高速乘法器;基4布斯算法;操作數(shù)隔離;門控時鐘;CMOS工藝

1 引 言

乘法器是微處理器的核心部件之一,也是數(shù)字信號處理領域的基本單元。乘法運算的性能好壞直接關系到整個系統(tǒng)的性能。本設計主要從速度和功耗兩個方面對乘法器進行了優(yōu)化設計。在速度方面通過改進算法來改善運算速度;在功耗方面通過分析功耗產(chǎn)生的原因?qū)ζ溥M行改善,有針對性的加入門控時鐘等低功耗設計方法,最終使電路功耗大幅度降低。

2 低功耗高速乘法器設計

2.1低功耗設計

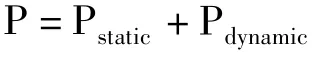

集成電路中的功耗損失主要由靜態(tài)功耗和動態(tài)功耗兩部分構(gòu)成。其中,靜態(tài)功耗主要是由亞閾值泄露電流所引起的功耗和由柵極泄露所引起的功耗;動態(tài)功耗包括晶體管翻轉(zhuǎn)時,電源和地間瞬時短路所引起的功耗和電路工作時對負載充放電所消耗的功耗。整個集成電路的功耗為:

靜態(tài)功耗與集成電路工藝有關,很難在設計中改變。在該乘法器設計中主要是想方設法降低電路的動態(tài)功耗。采用降低動態(tài)功耗的方法主要包括:

(1)門控時鐘

一般情況下時鐘信號(clk)直接接入電路中,只要clk發(fā)生變化,整個電路就會不斷運轉(zhuǎn)。設計中增加了門控時鐘后,情況則會不同,當電路正常工作時,時鐘門控使能信號為高,時鐘正常翻轉(zhuǎn);當電路處于空閑狀態(tài)時,時鐘門控使能信號置低,這時候輸入電路的clk一直為零,電路不再運行,電路將進入低功耗模式。所設計的門控時鐘電路如圖1所示,該電路由一個負鎖存器和一個與門實現(xiàn)。

圖1 門控時鐘電路

電路工作原理為:負鎖存器在clk為低時透明傳輸,en1信號上的毛刺僅出現(xiàn)在clk的低電平處,與clk進行與操作,可以將這部分毛刺消除掉。這樣,gclk上就沒有毛刺了。該電路輸出的時鐘gclk將接入電路中替代clk,當en為高電平時,電路正常工作;當en為低電平時gclk也為0,電路處于低功耗狀態(tài),這樣就能極大減少電路的動態(tài)功耗。

(2)隔離操作數(shù)

采用隔離操作數(shù)的方法來降低功耗,其主要原理是在不進行乘法運算的時候,將這些模塊的輸入置0,不輸入數(shù)據(jù),輸出結(jié)果不會發(fā)生變化;如果進行乘法運算時,再將輸入端口打開。這種方法會對系統(tǒng)的動態(tài)功耗有較大改進,在芯片面積方面所增加的邏輯僅僅是幾個多路選擇器。

(3)狀態(tài)編碼優(yōu)化

狀態(tài)編碼優(yōu)化方法主要對電路中的狀態(tài)機所產(chǎn)生的功耗進行優(yōu)化,目的在于通過減小兩個相鄰狀態(tài)之間的加權平均距離來減小開關活動性(狀態(tài)轉(zhuǎn)換時不變的比特位數(shù))。選取編碼的原則是:對于頻繁切換的相鄰狀態(tài),盡量采用相鄰編碼。例如,Gray碼在任何兩個連續(xù)的編碼之間只有一位數(shù)值不同,在設計計數(shù)器時使用Gray碼取代二進制碼,可顯著降低功耗。

2.2電路設計

設計的低功耗高速乘法器的硬件框圖如圖2所示,該電路主要由Booth編碼模塊、部分積相加模塊和高速寬位加法器模塊組成。

圖2 32位定點乘法器結(jié)構(gòu)

2.2.1基4布斯編碼模塊

布斯編碼是A.D.Booth在1951年提出的一種補碼相乘算法,可以將符號位與數(shù)值位合并在一起參與運算,直接得出用補碼表示的乘積,且正數(shù)和負數(shù)同等對待。傳統(tǒng)的布斯算法以2為基,形成N項編碼項、乘積項。為了提高運算速度,這里采用基4布斯算法,該算法可減少近一半的乘法乘積項,從而大大提高運算速度。該算法的原理如下所示。

兩個N(N為偶數(shù))位補碼表示的符號數(shù)相乘A×B,那么乘數(shù)A可表示為:

此即符號數(shù)的基4布斯算法,基4布斯編碼一次考慮了三位:本位、相鄰高位、相鄰低位;處理了兩位,形成(N/2)項編碼項、乘積項,從而大大減少了運算量。對于無符號數(shù),可將其高位作0擴展(擴展后位數(shù)也必須為偶數(shù)),并無影響。

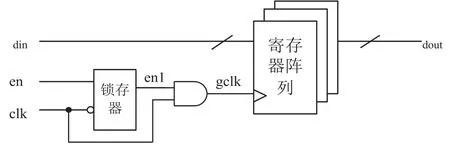

2.2.2部分積相加電路

為了能夠同時處理符號數(shù)和無符號數(shù),需要將32位寬度擴展為34位寬度,從而由布斯編碼器可得17個乘積項。由于乘積項有為負的,運算時需要進行取補運算,如果用一獨立的取補邏輯會給電路帶來額外的延遲和功耗。這里將取補邏輯中的加1運算,作為進位來處理,這樣做可以有效減小電路延遲,當前一乘積項為負時,CC取值為01,否則為00。各乘積項要以權值對齊,各進位也要以權值對齊,新構(gòu)成的乘積項陣列如下所示。

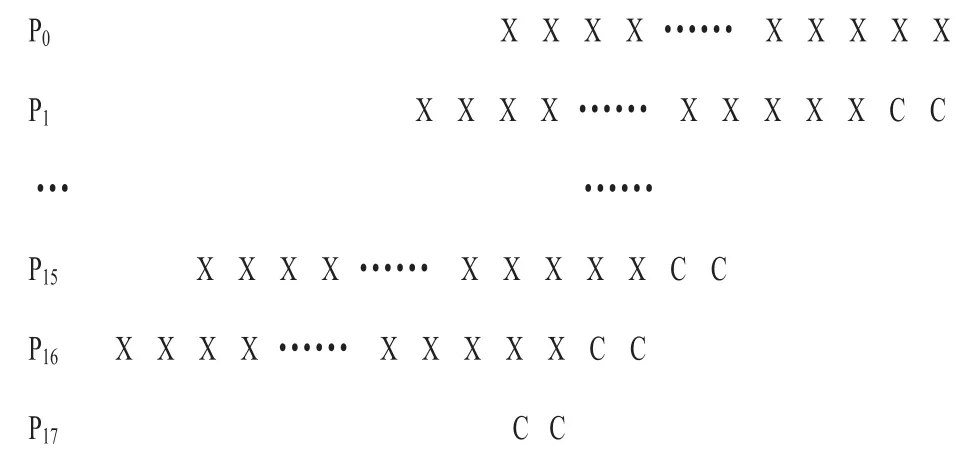

乘積項陣列已得到,還要將此陣列轉(zhuǎn)換為最終結(jié)果,這就用到加法器陣列。最簡單的方法是采用串行累加,但由于運算是串行的,延遲會比較大,需要17級加法器延遲。這里采用如圖3所示的流水線結(jié)構(gòu)。該結(jié)構(gòu)采用并行操作,全部采用4∶2壓縮器完成運算,布局規(guī)整,使執(zhí)行層次降低為log2N,從而大大減小了電路延遲。

圖3 壓縮器構(gòu)成的華萊士樹流水線結(jié)構(gòu)

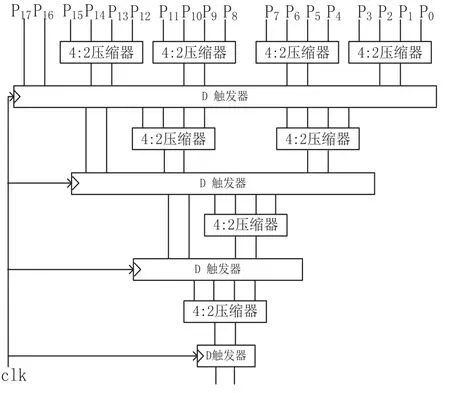

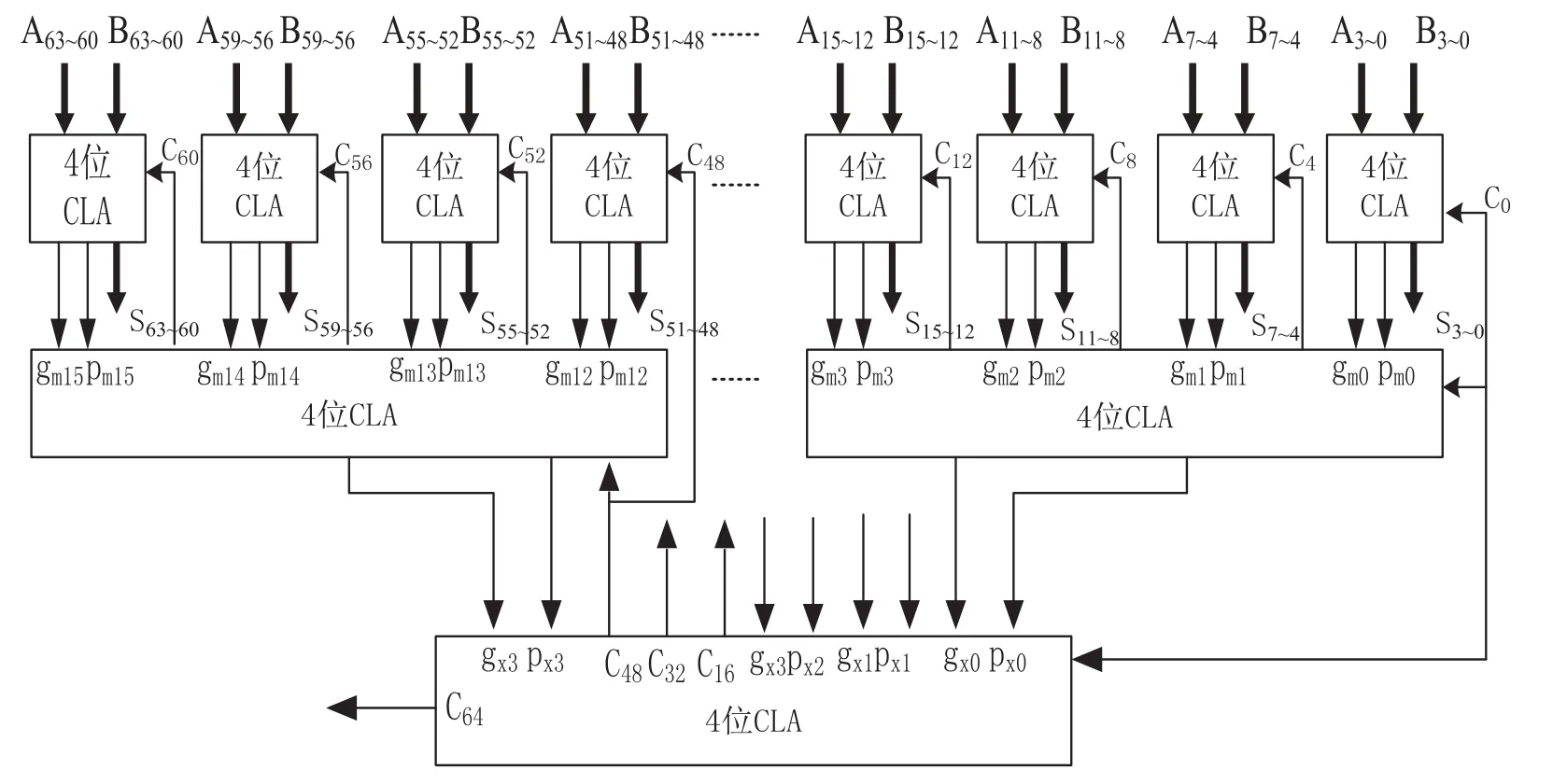

2.2.3高速寬位加法器設計

經(jīng)華萊士樹輸出的兩路64位數(shù)據(jù)相加后才能得到最終結(jié)果。本設計的64位加法器采用三級超前進位實現(xiàn),如圖4所示。該方法組內(nèi)和組間都采用先行進位方式,其延遲和加法器的位數(shù)沒有太大關系,不會隨著位數(shù)的增加而延長時間。

圖4 64位高速加法器結(jié)構(gòu)

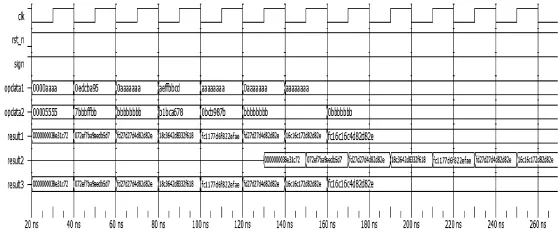

3 電路性能

根據(jù)系統(tǒng)設計要求,整個電路采用SMIC 0.18μm CMOS工藝實現(xiàn),利用Modelsim軟件對整個乘法器電路進行仿真,綜合工具是Design compiler,功耗分析工具是PowerCompiler。Modelsim仿真結(jié)果如圖5所示,clk為該乘法器的時鐘,rst_n為復位信號。opdata1為被乘數(shù),opdata2為乘數(shù),result1為采用組合邏輯實現(xiàn)的輸出結(jié)果,result2為采用流水線實現(xiàn)輸出的結(jié)果,result3為理論計算結(jié)果。從仿真結(jié)果可以看出所設計電路的計算結(jié)果與理論計算結(jié)果一致,電路實現(xiàn)了正確功能,區(qū)別在于流水線結(jié)構(gòu)的結(jié)果需要等待5個時鐘周期才能輸出。另外我們使用Synopsys的Design Compiler工具對流水線結(jié)構(gòu)實現(xiàn)電路進行邏輯綜合,最壞情況下的時間延遲為3.9ns,系統(tǒng)時鐘頻率可達256MHz,功耗小于37mw,與文獻[2-3,5-6]所設計電路相比,速度有了較大提高。

圖5 乘法器仿真結(jié)果

4 結(jié)束語

該設計對32bits定點乘法器各級電路結(jié)構(gòu)進行了優(yōu)化,與其他文獻中設計方法相比,減少了乘法器各級的延遲和功耗。電路采用SMIC 0.18μm CMOS工藝實現(xiàn),從設計結(jié)果可以看出:①與傳統(tǒng)乘法器相比,大幅提高乘法器運算速度,其最大時鐘頻率可達256MHz;②與不加低功耗設計技術的乘法器電路相比,加入低功耗設計技術后大幅度降低了電路功耗。設計中全部采用4∶2壓縮器實現(xiàn)新型Wallace樹結(jié)構(gòu),設計規(guī)則、對稱性好,易于ASIC實現(xiàn)。設計思想不僅可以在高速低功耗乘法器設計中能夠提升電路性能,而且可以將這種設計加入其它硬件電路中,對系統(tǒng)性能都會有極大提升。

[1]周怡,李樹國.一種改進的基4-Booth編碼流水線大數(shù)乘法器設計[J].微電子學與計算機,2014,31(1):60-63.Zhou Yi,Li Shuguo.Design of pipeline large integer multiplier based on an implementation of radix-4 modified booth encoding[J].MICROELECTRONICS&COMPUTER,2014,31(1):60-63.

[2]翟召岳,韓志剛.基于Booth算法的32位流水線型乘法器設計[J].微電子學與計算機,2014,31(3):146-149.Zhai Zhaoyue,Han Zhigang.32 bit pipeline multiplier design based on booth encoder[J].MICROELECTRONICS&COMPUTER,2014,31(3):146-149.

[3]姚若河,徐新才.基于冗余符號數(shù)的定點乘法器的設計[J].華南理工大學學報(自然科學版),2014,42(3):27-34.Yao Ruohe,Xu Xincai.Design of a fixed-point multiplier based on redundant signed digit[J].Journal of South China University of Technology(Natural Science Edition),2014,42(3):27-34.

[4]李飛雄,蔣林.一種結(jié)構(gòu)新穎的流水線Booth乘法器設計[J].電子科技,2013,26(8):46-48,67.Li Feixiong,Jiang Lin.A novel structure of the pipelined booth multiplier[J].Electronic Sci.&Tech.,2013,26(8):46-48,67.

[5]李軍強,李東生,李奕磊,等.32×32高速乘法器的設計與實現(xiàn)[J].微電子學與計算機,2009,26(12):23-26,30.Li Junqiang,Li Dongsheng,Li Yilei,et al.32×32 Highspeed multiplier design and implemetation[J].MICROELECTRONICS&COMPUTER,2009,26(12):23-26,30.

[6]周婉婷,李磊.基4Booth編碼的高速32×32乘法器的設計與實現(xiàn)[J].電子科技大學學報,2008,37(增刊):106-108.Zhou Wanting,Li Lei.A high-speed 32×32b multiplier implementation using improved radix-4 booth coders[J].Journal of University of Electronic Science and Technology of China,2008,37(suppl):106-108.

[7]蔣勇,羅玉平,馬晏,等.基于FPGA的32位并行乘法器的設計與實現(xiàn)[J].計算機工程,2005,31(23):222-224.Jiang Yong,Luo Yuping,Ma Yan,et al.Design and implemetation of 32-bit parallel multiplier using FPGA[J].Computer Engineering,2005,31(23):222-224.

[8]杜慧敏,李宥謀,趙全良.基于Verilog的FPGA設計基礎[M].西安:電子科技大學出版社,2006.Du Huimin,Li Youmou,Zhao Quanliang.FPAG Design Based on Verilog[M].Xi'an:XIDIAN UNIVERSITY PRESS,2006.

Design on 32-bit High-speed Low-power Multiplier

Zhang Mingying

(Xi'an International University,Xi'an 710077,China)

Using Verilog HDL hardware description language,a design of low power and high speed 32-bit fixed-point multiplier is presented.The speed of the multiplier,by means of optimization the design of radix-4 booth algorithm,4∶2 compressor and the final wide bit adder,is improved.In addition,the power consumption of the circuit is significantly reduced by means of performing the design techniques of operand isolation,clock gating and other low-power.Based on SMIC's 0.18μm CMOS process model,the circuit is synthesized by Synopsys's Design Compiler tool.The result shows that the maximum delay can be reduced to 3.9ns,the frequency of the system can reach 256MHz and the power consumption is less than 37mW.

Low-power;High speed multiplier;Radix-4 algorithm;Operand isolation;Clockgating;CMOS process

10.3969/j.issn.1002-2279.2016.01.005

TN409

A

1002-2279(2016)01-0018-04

?陜西省教育廳課題(2013JK1146)

張明英(1980-),女,山東省濰坊市人,碩士研究生,講師,主研方向:集成電路系統(tǒng)設計。

2015-03-30