一種考慮漏電流最低損耗的控制器電子模塊設計與實現

褚新建++宋東亞

摘 要: 漏電流損耗占電路能耗的大部分,屬于實時變化的動態過程,傳統控制器采用堆棧方法,通過對輸入信號的控制實現對漏電流損耗的控制,無法適應漏電流的動態變化,不能實現最低損耗控制。為此,設計一種考慮漏電流最低損耗的控制器電子模塊,通過模擬電路與CPLD相結合的方法對漏電流最低損耗控制器電子模塊進行設計,給出設計的總體結構。通過霍爾傳感器對漏電流進行檢測,利用比較器將檢測的實際漏電流與參考漏電流進行比較,用CPLD形成對應的斬波驅動信號,發送至電壓控制器,通過電壓控制器對主開關器件的導通和斷開進行控制,實現漏電流最低損耗的控制。軟件設計中,設計一個調試軟件,給出電流最低損耗控制程序和交替斬波程序。實驗結果表明,所設計控制器電子模塊的漏電流損耗很低,且運行效率高。

關鍵詞: 漏電流; 最低損耗; 控制器; 電子模塊

中圖分類號: TN722.7+3?34; TP303 文獻標識碼: A 文章編號: 1004?373X(2016)22?0138?0

0 引 言

隨著電子技術的逐漸發展,相關產業已步入深亞微米和納米工藝時代。漏電流損耗已經成為電子技術研究過程中所需考慮的一個關鍵指標[1?2]。電子技術領域中產生漏電流的機制越來越復雜,漏電流損耗對功耗產生的影響也越來越大。因此,對漏電流最低損耗進行控制具有重要意義,是亟需解決的關鍵問題,已經成為相關學者研究的重點課題,受到越來越廣泛的關注[3?4]。

目前,有關漏電流最低損耗控制器的研究有很多,相關研究也取得了一定的成果。其中,文獻[5]提出一種基于模型的漏電流最低損耗控制方法,該方法依據漏電流偏差約束條件與電壓預測法對漏電流進行最低損耗控制,可完成對命令信號的有效跟蹤,但該方法對參數的改變過于敏感,在一定程度上降低了預測控制的動態性能。文獻[6]提出一種基于堆棧的漏電流最低損耗控制器,該控制器將若干晶體管連接在一起,若一個或一個以上晶體管處于關閉狀態,則產生的漏電流將較單個晶體管明顯降低,依據堆棧原理,將時鐘門控信號看作是休眠模式的控制信號。如果電路處于待機狀態,則電路將形成既定輸入向量,使得盡可能多的晶體管處于堆棧狀態,從而將漏電流控制在最低損耗內,但該方法實現過程復雜,不適用于實際應用。文獻[7]設計了一種基于可變閾值的漏電流最低損耗控制器,即通過改變襯底偏置電壓對漏電流進行控制。在電路處于休眠狀態的情況下,在襯底添加一個負偏置電壓以提高閾值電壓,從而切斷漏電流。在電路處于運行狀態的情況下,在襯底添加一個相對較低的正偏置電壓,從而提高電路效率,然而該方法所需時間過長、效率極低。文獻[8]設計了一種基于多閾值的漏電流最低損耗控制器,該控制器引入一個高閾值NMOS管,將輸入信號看作是其控制信號。為了降低NMOS管對電路性能產生的影響,將其導通電阻就取最小值。隨著NMOS管導通電阻的逐漸增加,其寬度逐漸減小,漏電流損耗逐漸降低,但隨著NMOS管寬度的減小,其性能也逐漸降低。

針對上述方法的弊端,設計了一種考慮漏電流最低損耗的控制器電子模塊,通過模擬電路與CPLD相結合的方法對漏電流最低損耗控制器電子模塊進行設計,給出設計的總體結構,詳細分析了各硬件結構。軟件設計中,設計了一個調試軟件,給出電流最低損耗控制程序和交替斬波程序。實驗結果表明,所設計控制器電子模塊的漏電流損耗很低,且運行效率高。

1 一種考慮漏電流最低損耗的控制器電子模塊

設計與實現

1.1 考慮漏電流最低損耗的控制器電子模塊總體設計

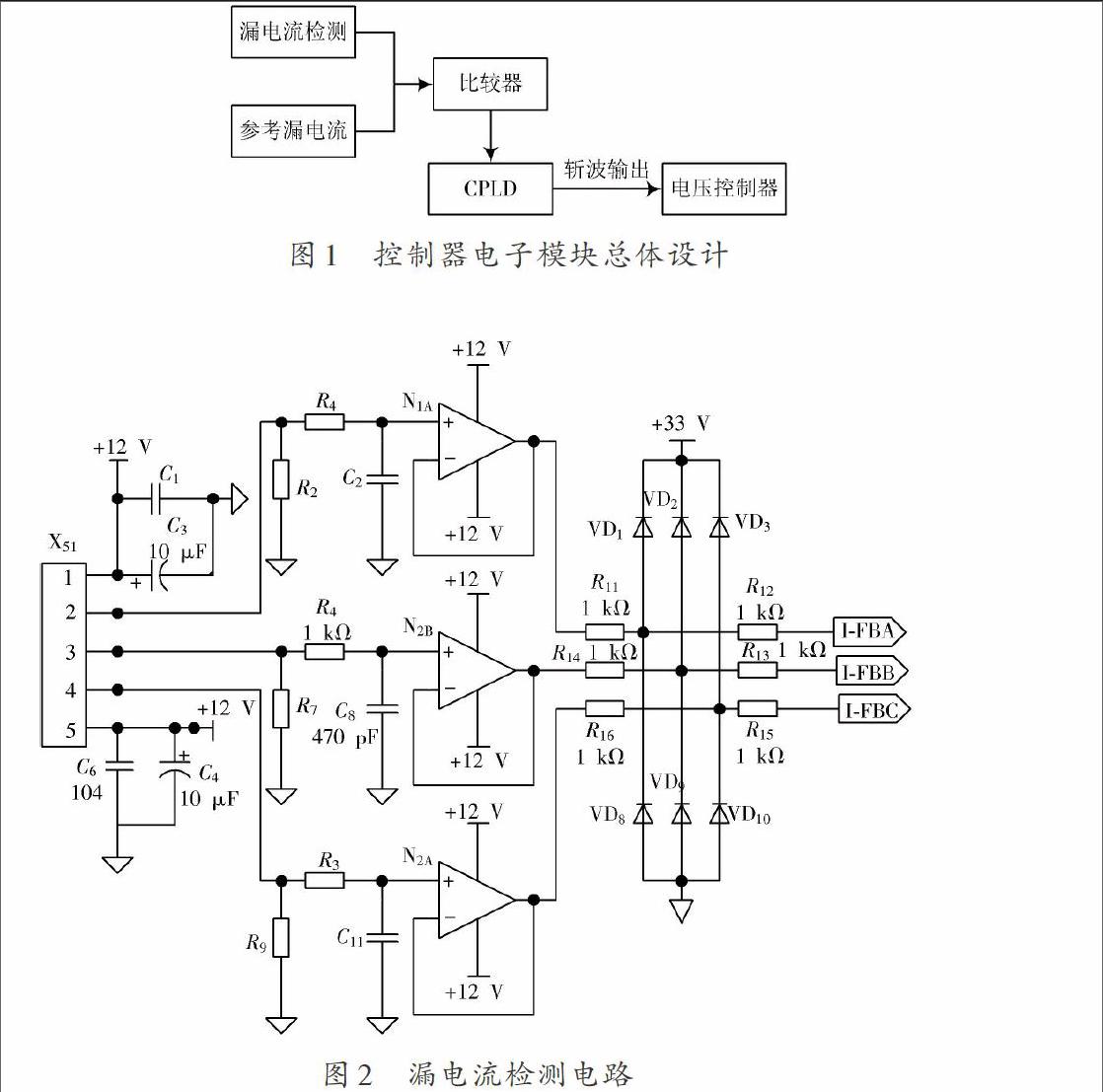

通過模擬電路與CPLD相結合的方法對漏電流最低損耗控制器電子模塊進行設計,該方法不僅響應速度快、跟蹤能力強、實時性高,而且不易受環境因素的干擾、控制更加可靠。控制器電子模塊總體設計如圖1所示。

由圖1可知,通過霍爾傳感器對漏電流進行檢測,利用比較器將檢測的實際漏電流與參考漏電流進行比較,如果實際漏電流未超過參考漏電流,則輸出低電平信號;否則,將比較器的輸出信號傳輸給CPLD;將漏電流最低損耗控制程序代碼從PC機下載至CPLD芯片中,CPLD形成對應的斬波驅動信號,發送至電壓控制器;通過電壓控制器對主開關器件的導通和斷開進行控制,以實現漏電流最低損耗的控制。

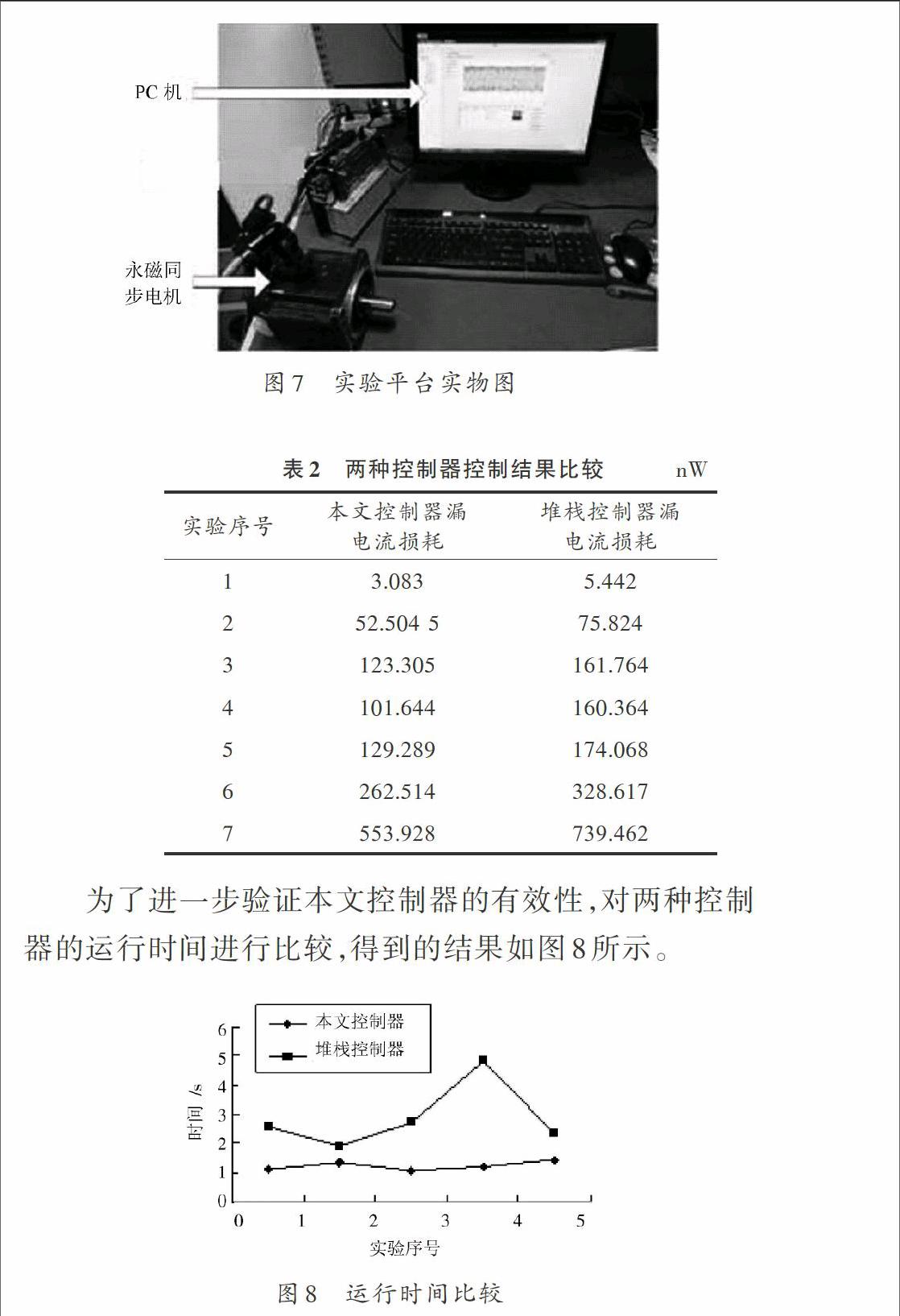

1.2 漏電流檢測電路

在考慮漏電流最低損耗的控制器中,首先需對漏電流進行檢測,圖2為漏電流檢測的部分電路。

選用型號是LT108?S7的磁場平衡式霍爾電流傳感器對漏電流進行檢測,其不僅檢測精度高,而且響應速度快,抗干擾性能強,能夠實現電隔離檢測。所設計控制器電子模塊僅需一只傳感器即可,LT108?57轉換率是l∶2 000,也就是被測漏電流是輸出電流的2 000倍,通過輸出電流即可間接獲取被測漏電流。圖2中R2,R7,R9分別為A相、B相、C相電流的采樣電阻,將輸出電流在采樣電阻上的壓降看作是相電流的反饋信號,經濾波、TL032運放與限幅穩壓處理后通過I?FBA,I?FBB,

I?FBC引腳輸出。

1.3 LM393雙電壓比較器

比較器將檢測到的實際漏電流與參考漏電流進行比較,如果實際漏電流未超過參考漏電流,則比較器會輸出低電平信號;否則,比較器將輸出信號發送至CPLD。比較器選擇LM393H雙電壓比較器,其電路圖如圖3所示。

LM393H工作電源電壓范圍較廣,所消耗能耗較低,其輸出能夠和TTL,MOS,CMOS等兼容。通過漏電流檢測到的漏電流信號,I?FBA/I?FBB/I?FBC。通過采樣電阻加在LM393H的同相輸入端,參考漏電流經RP1采樣變成電壓信號,通過反相輸入端進入LM393H。RP1是變阻器,其端電壓在0~2.75 V范圍內可調,以改變參考電流。若I?FBA/I?FBB/I?FBC超過參考漏電流,則LM393H將輸出高電平信號;反之,其輸出的為低電平信號。