VHDL中常用的數據對象

劉春梅 高香梅

摘 要

簡要介紹了VHDL中數據對象的基本概念,從不同方面討論了常用的數據對象的區別與聯系,通過實例詳細比較了信號與變量的用法。

【關鍵詞】VHDL 變量 信號 常量

1 引言

VHDL是一種常用的高級描述語言,通常包含庫、程序包、實體、構造體和配置等部分。而數據對象根據不同情況可以定義在VHDL程序的這些部分中,尤其是信號和變量的使用易產生混淆。

2 數據對象的區別與聯系

在VHDL語言中,凡是可以賦予一個值的對象稱為客體也可叫做數據對象,能夠接受不同數據類型的賦值。常用的數據對象主要有常量、變量和信號三種。

從定義范圍來看,常量和信號是全局量,變量是局部量。常量可以在程序包、實體、進程中使用,一般在程序開始前對常量進行賦值。信號是電子電路內部硬件實體相互連接的抽象表示,可以在結構體、程序包和實體說明中使用,信號名不能沖突。變量僅在進程語句、過程語句、函數語句的結構中使用,不能將信息帶出對它作出定義的當前設計單元。其中,應用在不同范圍的變量名可以重復。

從延時特性來看,常量與變量的賦值是立即生效的,沒有延時。VHDL語言規則不支持變量附加延時語句,變量的賦值是一種理想化的數據傳輸,是立即發生。但是信號的代入賦值是允許延時的。比如,A0<=A1 AFTER 10 ns表示信號A0的值是由A1延時10ns所賦予的。

從賦值方式來看,常量與變量采用的是“:=”進行賦值,信號采用的是“<=”進行代入賦值,但是不論何種數據對象,初始化賦值均采用“:=”,其中,采用“:=”對信號賦初值時候不產生延時。常量的值在程序運行過程不能改變,但是信號與變量可以進行賦值。

常量、變量和信號所賦的值應該與定義的表達式數據類型一致,否則會出現錯誤。信號與變量也可相互賦值,賦值符號的選擇取決于被賦值的數據對象。由于變量只能在所定義進程內使用,若想將變量用于進程外,則可以賦值給同類型的信號。在VHDL中,如果需要對某一數據進行多次操作,則必須使用變量,因為對信號的多次賦值只有最后一次會生效。

3 變量與信號用法的實例分析

數據對象中,變量與信號的用法易混淆,以四選一數據選擇器為例,分別采用信號賦值語句和變量賦值語句來實現。A0,A1,A2,A3分別為選擇器的一位數據輸入端,選擇端為S1,S0,其中S1S0分別為00,01,10,11時,選擇A0,A1,A2,A3的值給輸出端口Q。采用信號賦值語句的結構體程序如下:

ARCHITECTURE one OF mux4 IS

SIGNAL xy:INTEGER RANGE 0 TO 3;

BEGIN

PROCESS(A0,A1,A2,A3,S0,S1)

BEGIN

xy<=0;

IF (S0='1') THEN xy<=xy+1;

END IF;

IF (S1='1') THEN xy<=xy+2;

END IF;

CASE xy IS

WHEN 0=>Q<=A0;

WHEN 1=>Q<=A1;

WHEN 2=>Q<=A2;

WHEN 3=>Q<=A3;

WHEN OTHERS =>NULL;

END CASE;

END PROCESS;

END one;

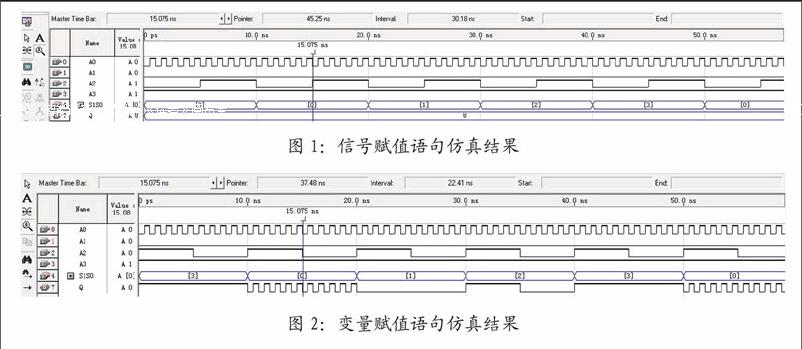

該程序段內xy是全局量的信號,定義在結構體中,其值與S1S0的值一樣,當xy分別為0,1,2,3時,將A0,A1,A2,A3賦給Q。經過Quartus II9.0軟件程序編譯可以通過。仿真結果如圖1所示,其中,輸入A0設置為頻率較高的周期信號,A1為低電平,A2位頻率較低的周期信號,A3為高電平。

從圖1仿真結果看出,采用信號賦值語句的結果不正確,分析其原因主要是因為信號賦值是在進程結束時更新,啟動一次進程信號xy的值只能改變一次。

下面采用變量賦值語句來實現,對程序進行如下修改:

ARCHITECTURE one OF mux4 IS

BEGIN

PROCESS(A0,A1,A2,A3,S0,S1)

VARIABLE xy:INTEGER RANGE 0 TO 3;

BEGIN

xy:=0;

IF (S0='1') THEN xy:=xy+1;

END IF;

IF (S1='1') THEN xy:=xy+2;

END IF;

CASE xy IS

WHEN 0=>Q<=A0;

WHEN 1=>Q<=A1;

WHEN 2=>Q<=A2;

WHEN 3=>Q<=A3;

WHEN OTHERS =>NULL;

END CASE;

END PROCESS;

END one;

該程序段中,作為局部量的變量定義在進程中,經過軟件編譯成功。圖2為采用變量賦值語句的仿真結果。

從圖2看出,當S1S0也就是xy的值為0時,Q輸出A0的值,S1S0為1時,Q輸出A1的值,S1S0為2時,Q輸出A2的值,S1S0為3時,Q輸出A3的值,所以采用變量賦值語句的結果實現了選擇器的功能,這是因為變量賦值是立即更新,啟動一次進程變量xy的值為所需要的最后結果。

4 結束語

在VHDL中,數據對象類似于一種容器,它接受不同數據類型的賦值。常量,變量和信號是常用的三種數據對象。其中,信號與變量的使用容易產生混淆,通過實例分析討論了信號與變量,如果使用不當,結果會產生錯誤,因此,在設計中要謹慎使用信號與變量。

參考文獻

[1]吳方,劉文娟.EDA技術[M].武漢:武漢大學出版社,2011.

[2]劉昌華.EDA技術與應用——基于Quartus II和VHDL[M].北京:北京航空航天大學出版社,2012.

[3]胥勛濤.EDA技術項目化教程[M].北京:電子工業出版社,2011.

作者單位

安徽農業大學經濟技術學院 安徽省合肥市 230011