一種基于2FSK的調制解調系統設計

張華亮+酒樂

摘 要

本文根據2FSK調制解調的工作原理,提出了一種基于FPGA 芯片的2FSK調制解調器的設計方法。該方法采用頻率選擇法實現調制器設計,非相干解調法實現解調器設計。同時利用VHDL語言在Xilinx公司的Spartan-6系列芯片上進行實現。經過實際工程驗證,該方法滿足系統要求,具有較高的通用性和可靠性。

【關鍵詞】2FSK 頻移鍵控 調制 解調 系統

1 引言

FSK頻移鍵控(FSK-Frequency Shift Keying)是一種用數字信號去調制載波頻率的調制方式,是信息傳輸中使用較早的一種調制方式,具有實現方法簡單,并且解調不須恢復本地載波、可以異步傳輸、抗噪聲和抗衰落性能強等特點。在中低速數據傳輸,特別是在衰落信道數據傳輸中,有著廣泛的應用。

針對傳統用硬件實現2FSK調制解調的方法,特別是相干解調需要提取載波,設備相對復雜、成本較高的特點,本文重點研究了基于FPGA 芯片的非相干調制解調系統。通過ISE軟件平臺,進行硬件描述語言的設計,提出了一種2FSK調制解調系統的設計及實現方法。

2 2FSK數字調制解調原理

2FSK 也稱為二進制頻移鍵控。二進制頻移鍵控信號碼元的“1”和“0”分別用兩個不同頻率的正弦波來傳送,其振幅和初始相位不變。可表示為。

上式中假設碼元的初始相位分別θ1和θ2;ω1=2πf1和ω2=2πf2為兩個不同頻率碼元的角頻率。

2FSK信號的產生有兩種方式:

(1)頻率選擇法;

(2) 載波調頻法。

頻率選擇法是用基帶脈沖序列控制的開關電路對兩個不同的獨立頻率源進行開關選通。載波調頻法采用調頻電路來實現,將碼元調制到不同的載波頻率上,使其輸出不同頻率的碼元信號。這兩種方法產生的 2FSK 信號的波形基本相同,但由調頻器產生的 2FSK 信號在相位上是連續的,而頻率選擇法產生的2FSK 信號,由于分別由兩個獨立的頻率源產生兩個不同頻率的信號,因此相鄰碼元的相位不連續。

2 FSK信號的解調方法有相干解調、非相干解調兩種方法

相干解調通過將兩路信號與本地相干載波相乘后,經低通濾波器進行抽樣判決,比較兩路信號包絡的大小,進行解調。相干解調中的相干載波必須從接收信號中提取,并且和信號碼元同頻同相。非相干解調中應用較多的是包絡檢波法,用兩個窄帶濾波器濾除無用信號,保留有用信號后,經包絡檢測后分別取出包絡信息,再將兩路輸出同時送到抽樣判決器進行比較,從而判決輸出基帶數字信號,本系統采用非相干解調的方法。

3 2FSK數字調制信號產生

本文采用FPGA芯片進行2FSK數字化設計,系統時鐘在FPGA內部經分頻器后得到頻率產生器1、頻率產生器2的工作時鐘,生成兩個頻率為f1、f2的正弦載波頻率信號。根據輸入的二進制串行數據,通過選通開關,完成對f1、f2兩個載波頻率的選擇,生成2FSK調制信號,經過D/A芯片轉換后,經信道將信號發送。

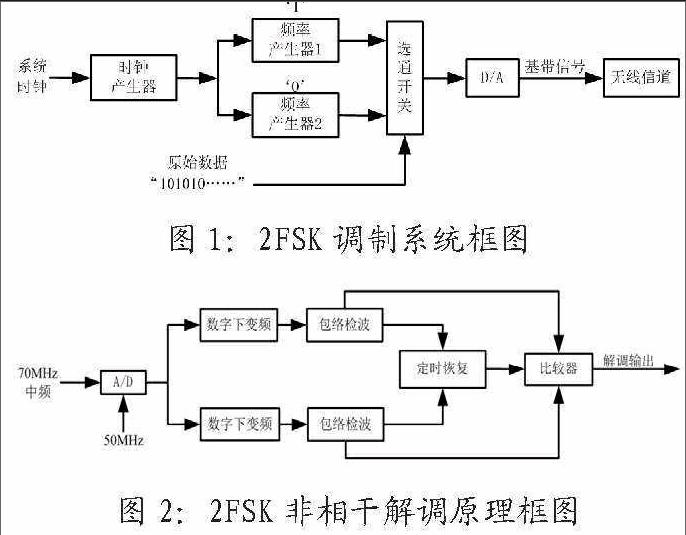

2FSK 數字信號發生器的原理框圖如圖1 所示,整個系統共分為時鐘產生模塊、頻率產生模塊、選通開關模塊及D/A模數變換器等4 部分, 其中前3 個部分均在FPGA 器件內部設計生成。

本文利用FPGA芯片進行數字DDS[3-5]設計,直接用數字頻率合成方式產生頻率、相位和幅度可控的2FSK調制所需的兩種數字載波頻率信號。DDS主要由相位累加器、相位調制器、正弦查找表構成。

本設計中選擇調制中頻頻率為70MHz,系統時鐘設置為200MHz,設置兩個輸入頻率字分別為70.1 MHz和69.9 MHz,通過DDS模塊可產生以上兩個頻率的數字信號。

選通開關根據數字基帶碼元信號選擇輸出頻率信號,當選通開關接收到碼元“0”時,輸出頻率為70.1 MHz的正弦波;當選通開關接收到碼元“1”時,輸出頻率為69.9 MHz的正弦波。

4 2FSK非相干解調

在本設計中,2FSK信號經過收信機模擬放大和變頻后,形成一個幅度穩定的中頻信號,經過A/D變換器直接對中頻信號進行采樣,采樣后在FPGA芯片內完成2FSK信號的非相干數字解調。

2FSK非相干數字解調器由數字下變頻器、包絡檢波器、定時恢復單元等組成,工作原理框圖如圖2所示。

本設計中首先將70M中頻模擬信號進行A/ D 變換,轉換為數字信號后,在數字域上采用FPGA 來實現2FSK信號的解調處理。數字化的中頻信號通過與本地載波信號的正交下變頻變換,將兩路數字信號變換到零頻,再通過信號的包絡檢測,比較每個頻點的能量值就可以恢復出原始碼元信息。

由于解調系統的系統時鐘為50MHz,故設置兩個本地載波信號的頻率分別為20.1MHz和19.9MHz。輸入的70MHz中頻信號通過分路器分為I、Q兩路信號,分別與本地載波信號混頻到零頻,經過低通濾波濾除倍頻項和帶外噪聲后,分別對I、Q 兩支路進行平方相加,計算每一個支路能量,在比特定時脈沖的控制下,比較兩路信號能量值即可恢復出基帶信息。

5 結語

本文中2FSK調制解調模塊均進行了系統仿真和測試,并采用VHDL 語言在Xilinx公司的Spartan-6系列芯片上進行了工程化實現,并進行了實際測試,結果表明,信號頻率精度、調制譜指標及解調指標完全滿足設備指標要求。

參考文獻

[1]樊昌信,曹麗娜.通信原理[M].北京:國防工業出版社,2001.

[2]梅燦華,張潛.基于FPGA的鍵控移頻調制解調器的設計與實現[J].安徽大學學報:自然科學版,2005,29(02).

[3]賴昭勝.基于DSP Builder的DDS實現及其應用[J].微計算機信息,2006(11):186-189.

[4]李志鵬,郭勇,沈軍基.基于DDS技術實現信號發生器[J].微計算機信息,2007.

[5]梅燦華,張潛.基于FPGA的鍵控移頻調制解調器的設計與實現[J].安徽大學學報,2003,27(02):22-27.

作者單位

中國電子科技集團公司第五十四研究所 河北石家莊 050081