基于國產CPU的并行冗余計算機系統研究

黃 晨,汪文明,張義超,岳 瑋

(北京宇航系統工程研究所,北京 100076)

基于國產CPU的并行冗余計算機系統研究

黃 晨,汪文明,張義超,岳 瑋

(北京宇航系統工程研究所,北京 100076)

目前國家不斷推進的國產自主可控信息系統建設,其核心國產計算機系統由于技術成熟度低、市場推廣晚等原因,暴露出可靠性低、穩定性差的問題,直接導致系統功能無法成功應用;圍繞國產化計算機系統的并行冗余架構開展研究,通過計算機系統架構的軟硬件設計,以及高速緩存一致性架構、高速互聯總線和三狀態轉換機制方法的應用,基于國產CPU 并行冗余計算機系統,可以有效消除備份計算機系統進行當班切換時,存在的切換時間延時和切換過程數據丟失的問題;通過試驗驗證,該系統可以完成計算機系統中CPU處理器和功能橋片故障模式的容錯處理,并保障信息數據的完整性和實時性,有效提高設備中計算機系統的工作可靠性與穩定性。

并行冗余計算機系統; HyperTransport總線;高速緩存一致性協議

0 引言

然而計算機系統作為電氣系統的控制中樞與數據中心,其地位和作用都是舉足輕重的,計算機系統絲毫的差錯與謬誤的出現,輕則能夠造成任務的延誤,重則可能危及到全局成敗。

為了提升國產計算機系統的可靠性,目前的電氣系統在應用時通常都采用雙計算機系統的設計,主從計算機系統采用相同的初始設置,一旦主計算機系統出現工作異常,經指揮決策后,關閉主計算機系統,啟動從計算機系統來代替原計算機,繼續完成相關工作,保證任務的繼續完成。然而這種工作模式存在著一定的弊端,首先,該模式下,由主計算機系統到從計算機系統的切換需要一定的等待時間,然而在某些特定工作場合下,設備的工作停滯是難以承受的;其次,計算機系統切換后,必定存在一定程度的數據丟失,或者進程丟失,往往會帶來不可挽回的損失。為了解決備份計算機系統切換所存在的隱患,本文對基于國產CPU處理器的并行冗余計算機系統進行針對性研究,旨在提升國產計算機系統的工作可靠性。

1 系統結構及原理

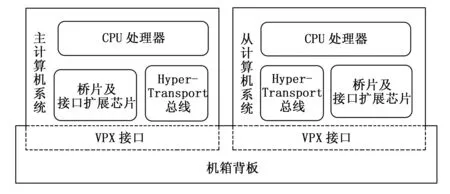

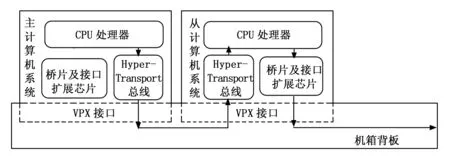

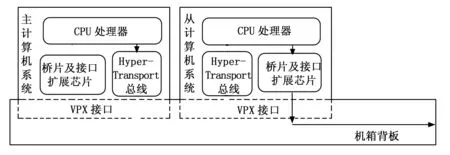

本并行冗余計算機系統結構組成如圖1所示,包含主從兩個計算機系統,兩個計算機系統的硬件組成基本相同,每個計算機系統的結構均按照機箱插卡模塊的樣式完成設計,通過VPX接口插入設備機箱的插槽之中,兩個模塊之間的互連總線經VPX接口與機箱背板完成走線。

圖1 并行冗余計算機系統結構圖

兩個計算機系統構成分布式存儲結構。多個存儲單元與處理單元分布在整個系統之中,通過專門的互連網絡結構連接在一起組成分布式的共享內存空間。每一個處理器可以訪問自己的存儲器,也可以訪問其他處理器的存儲器或共享的存儲器。通過硬件維護的高速緩存一致性協議,使得各個處理器對于本地及遠程存儲單元的影響都是統一的[1]。

正常工作時,由主計算機系統的芯片組完成系統控制與數據管理工作,從計算機系統的芯片組通過16位的HT(HyperTransport)總線跟蹤主計算機系統處理器的進程操作及工作狀態,包括CPU進程信息、電子盤存儲信息等,并在從計算機系統的電子盤之中同步備份主計算機系統的電子盤中的操作數據,利用高速緩存一致性協議,保證兩個計算機系統的處理器核、內存以及電子盤之間的數據與緩存狀態均保持一致。正常工作時信號通路如圖2所示。

圖2 正常工作時信號通路示意圖

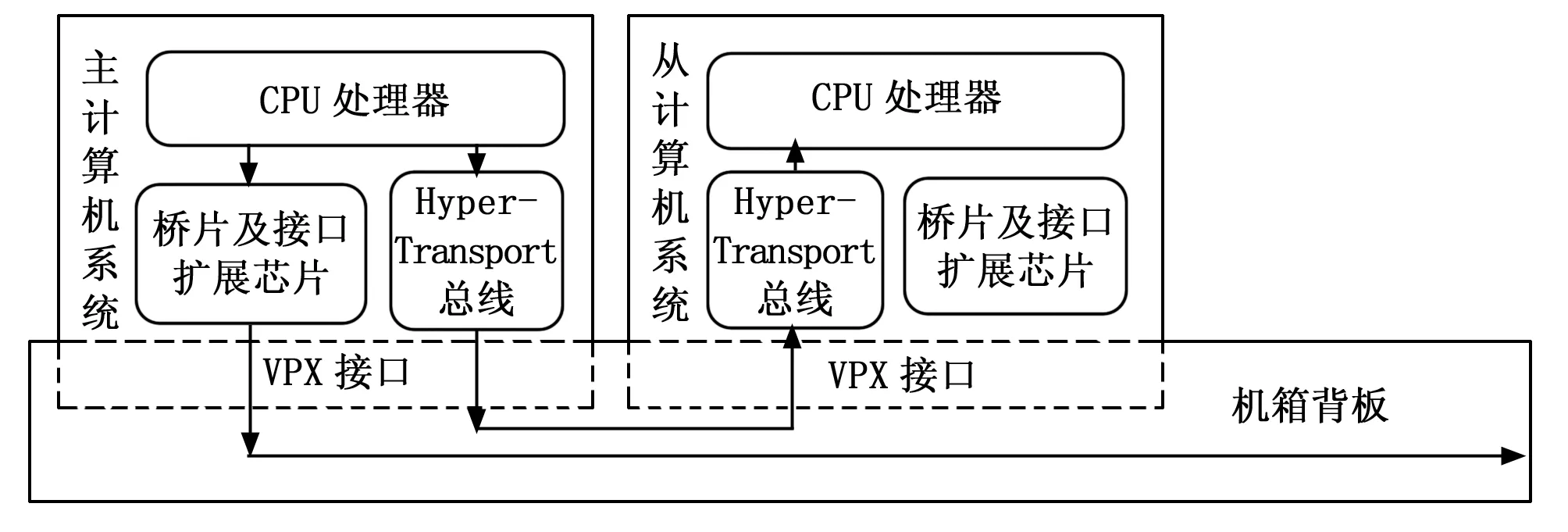

當主計算機系統的橋片或者接口芯片出現問題,導致工作異常時,主計算機系統的處理器可以通過HT總線將信息或指令傳輸給從計算機系統的處理器,通過從計算機系統所具有的橋片或接口芯片繼續完成系統工作或任務。橋片故障時信號通路如圖3所示。

圖3 橋片故障時信號通路示意圖

當主計算機系統的處理器出現異常時,從計算機系統的處理器將依靠HT總線接口的硬件所支持的系統高速緩存一致性維護,達到系統工作的近似無縫切換,保證系統工作的正常,CPU故障時信號通路如圖4所示。避免了由于計算機系統的工作異常,導致工作流程終止,甚至重要數據丟失等難以挽回的危害,從而有效提高系統可靠性,實現了計算機系統的熱備冗余備份。

呂凌子把5萬元現金重新揣回了家。呂凌子原以為5萬元可以將事情做個了斷,然而事情并沒有朝著她所期待的方向發展,并沒有她想象中那么順利。

圖4 CPU故障時信號通路示意圖

2 系統硬件設計

出于安全性和自主性考慮,本計算機系統采用中國科學院計算所自主研發的龍芯3A CPU處理器作為核心處理器開展研究。

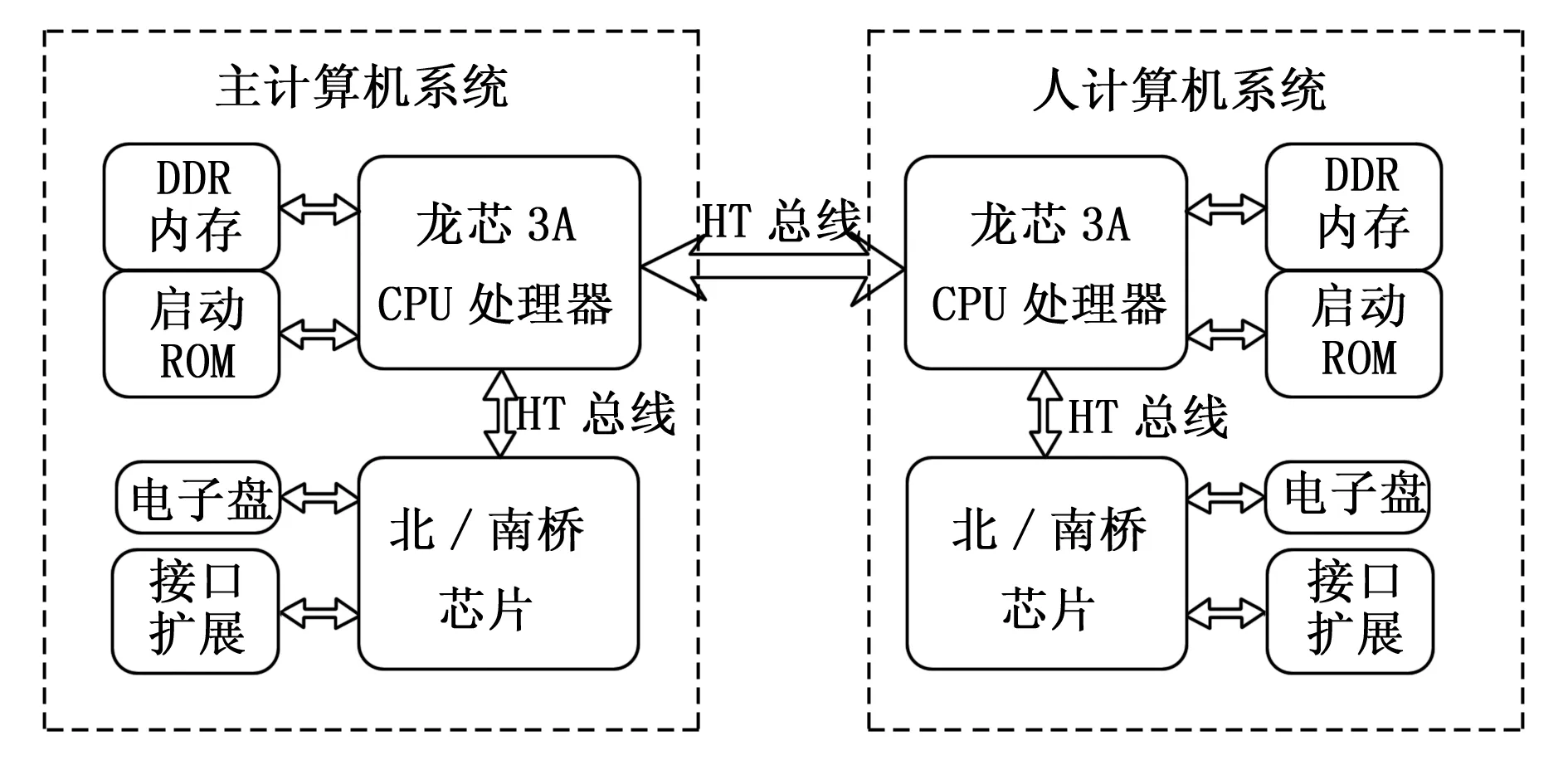

本并行冗余計算機系統包含主備兩個計算機系統,構成雙冗余模式,如圖5所示。

圖5 并行計算機系統架構組成

兩個計算機系統的硬件組成設計基本相同,均由CPU單元、南北橋單元、存儲單元、接口單元4部分組成。CPU單元主要包含龍芯3A四核處理器;南北橋單元主要由RS780E北橋芯片和SB710南橋芯片構成;存儲單元則包括DDR內存、啟動配置ROM和電子硬盤3大類;接口擴展芯片則依據系統需求具體設計,可以包含網絡信號、串并行接口總線、視頻信號、音頻信號等等。 兩個芯片組之間通過16位HyperTransport總線接口實現兩個CPU間互連,利用高速緩存一致性協議,保證兩處理器核間數據及指令緩存的一致性。

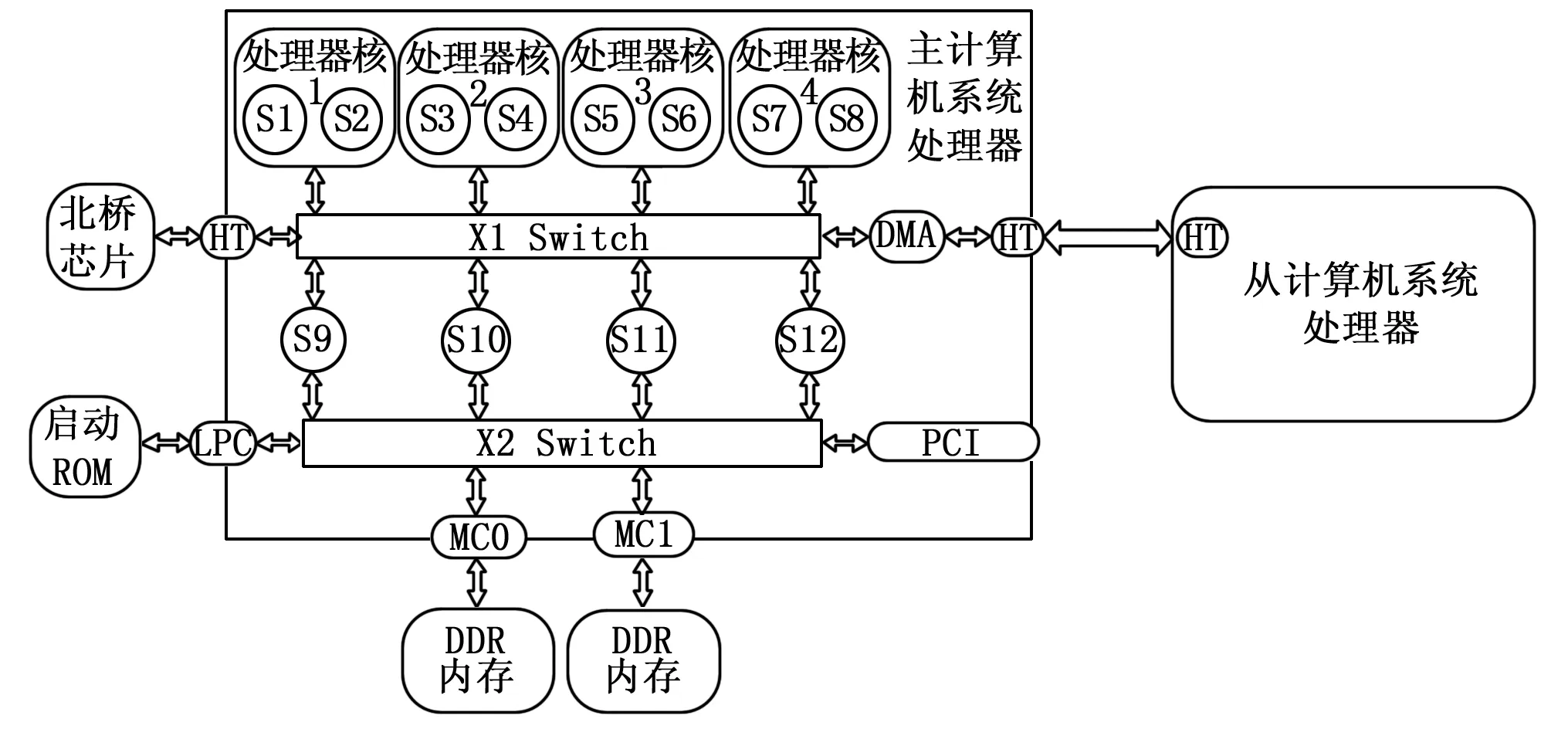

并行計算機系統利用龍芯3A處理器內部結構搭建并行互連體系結構,結構示意圖如圖6所示。

圖6 并行互連體系架構示意圖

CPU芯片內含有4個處理器核,每個處理器核內具有獨立的一級數據緩存和一級指令緩存,一級緩存由各處理器核私有;芯片內的二級高速緩存被片內的所有處理器核共享,根據地址可以分成供并行訪問的4個交錯體。每個芯片具有兩級AXI交叉開關,X1和X2,處理器核通過X1訪問二級緩存塊,二級緩存通過X2訪問兩個內存控制器,內存地址分布和二級緩存地址分布一致,以簡化二級緩存和內存之間的通路并降低二級緩存訪問失效的延遲[2]。

HT控制器通過DMA控制器與X1相連,由DMA負責IO的DMA控制及片間、IO訪問和處理器訪問之間的數據一致性維護,由于交叉開關不區分處理器端口和互連端口,HT接口也可視為特殊的處理器處理。

互連結構體系中的存儲單元與處理器節點可以分布在系統內不同位置,其中的存儲單元可以通過互連網絡被各個處理器所共享。互連體系結構中采用X-Y路由算法,點到點的路由是固定的,可以保證點對點數據包嚴格有序傳輸;每個模塊均會被分配給一個與邏輯位置相關的全局ID號,以決定轉發端口路由。

CPU級間互連的HyperTransport總線是基于報文的、點對點串行鏈路結構,將芯片內部低頻并行信號通過發送端物理層DA轉換接口處理為高頻串行信號,每個時鐘沿傳輸并行信號中的一位,通過LVDS信號傳輸線,到達接收端,再由接收端物理層AD轉換接口還原為低速并行信號。HT總線信號分為三類:

1)鏈路信號:32位CAD傳輸信號、1位CTL控制信號、4位CLK時鐘信號,用于控制、傳輸數據;

2)復位信號:PWROK和RESET信號,用于初始化和復位鏈路;

3)管理信號:LDTSTOP和LDTREQ信號。

HT總線采用單向點對點傳輸技術,將CAD信號分成兩組,按照不同方向單向傳輸,可達GB/s,在處理器芯片上按照接收端和發送端分別處理,傳輸效率與有效帶寬均遠大于雙向信號總線,簡化板級設計工作。

HT總線采用包交換方式進行信號傳輸,將總線操作分為控制包和數據包兩大類,控制包還包括讀命令包、寫命令包、讀響應包、寫響應包,每組傳輸總線使用一位控制信號線來區分傳輸的為控制包還是數據包。

HT總線采用虛通道技術,將HT協議劃分為三種不同的數據流:無響應請求通道、需響應請求通道、響應通道,將一個物理鏈路劃分為若干相互獨立的邏輯通道。針對這三種通道,還設置了六種緩沖區類型,實現每個虛通道的緩沖流控自行維護,避免命令之間的互鎖,提供了亂序執行的基礎條件,實現不同數據流在同一信號線上的并發傳輸,提高總線傳輸的效率和性能[3]。

3 系統軟件設計

并行冗余計算機系統采用基于目錄的高速緩存一致性協議,系統內共享二級緩存與各個處理器核內私有指令緩存和數據緩存之間的數據一致性,由系統中共享存儲層次的目錄維護。目錄與其數據的存儲位置相關聯,目錄的管理由各個存儲單元所在的存儲節點目錄決定,目錄控制器存儲的相關一致性信息包括存儲單元的狀態和擁有此存儲單元備份的處理器號。

每個共享存儲單元的狀態由這個共享存儲單元自身維護,這個狀態標識了當前這個共享存儲單元在其它處理節點中私有緩存的使用方式,并且記錄了哪些處理器的私有高速緩存中擁有該共享存儲單元的備份。系統中任意一個處理器需要對共享存儲單元進行操作時,都直接與這個共享存儲單元本身交互,由這個共享存儲單元的狀態控制器再與其它處理器中的緩存備份交互,通過一致性協議控制整個系統中的緩存數據一致性。

龍芯3A處理器的一級緩存由各處理器私有,二級緩存和內存采用全局編制,由所有處理器共享。緩存塊的目錄信息在宿主二級緩存中維護,目錄使用32位寬度的位向量來記錄擁有每個緩存備份的一級緩存編號,因此硬件能自動維護各指令和數據緩存之間的一致性,同時也就維護了全系統各級存儲結構間的數據一致性。

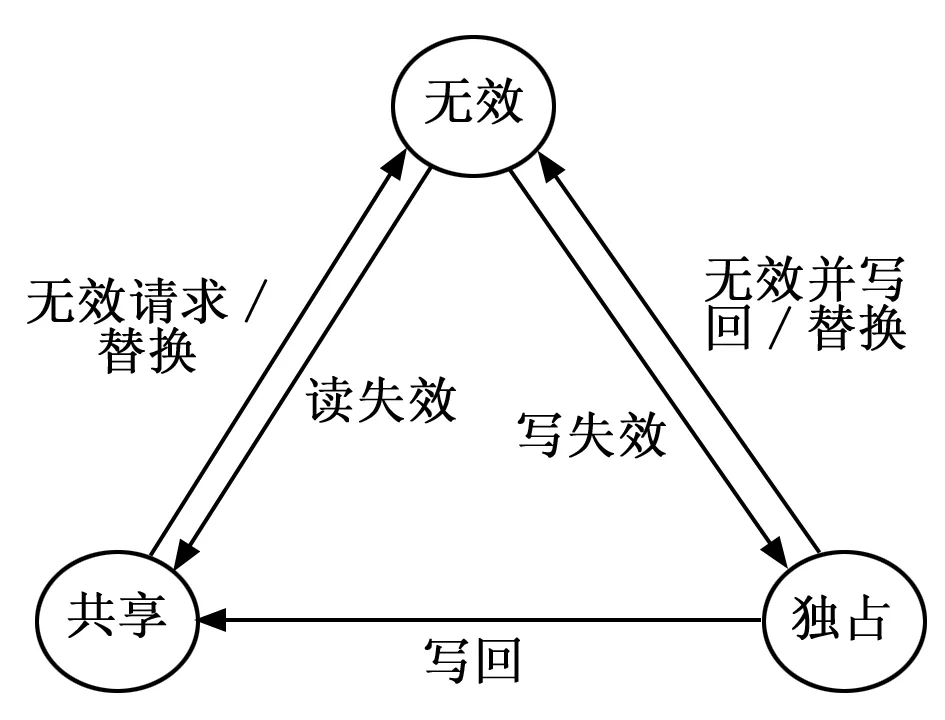

一級緩存塊采用三狀態轉換機制,無效狀態、共享狀態和獨占狀態,無效表示這個緩存塊中沒有有效數據,獨占表示這個緩存塊中的數據有效且未經修改,共享表示這個緩存塊中的數據已經被修改而且還未寫回下級緩存。三種狀態的相互轉移圖如圖7所示。

圖7 并行互連體系架構示意圖

4 實驗結果與分析

并行冗余計算機系統工作主頻為800 MHz,將系統工作周期設定為125 μs,主副計算機系統同步周期設定每間隔125 ms主副計算機系統完成一次硬盤數據同步備份。通過在計算機系統二次供電母線增加功能開關的方式,進行故障注入,分別將主計算機系統的CPU處理器或接口橋片的供電關斷,實現應急故障模擬。經測試驗證,該并行冗余計算機系統可以通過加載CPU寄存器信息和內存信息,實現計算機系統運算及通信內容的無縫切換,而依靠CPU芯片內的Cache一致性設計和三狀態轉換機制,成功保障了寄存器信息與內存信息的高度同步性。

5 結束語

本文首先對于并行冗余計算機系統的功能應用進行了介紹與分析,然后又介紹了并行冗余計算機系統的構成,并對于該系統的硬件和軟件設計的關鍵技術進行了細致全面的分析,為該系統的實現提供了基礎與參考,最后通過故障注入方式,對于系統的容錯備份功能進行了驗證。并行冗余計算機系統在的應用,對于國產自主可控計算機設備的可靠性改進具有重要意義,為任務的成功完成提供有效支撐。

[1] Chen D, Su H, Yew P. The impact of synchronization and granularity on parallel systems[C]. Proceedings of 17th Annual International Symposium on Computer Architecture, 1990,239-248.

[2] 王煥東,高 翔,陳云霽,等.龍芯3號互聯系統的設計與實現[J],計算機研究與發展,2008(45):2001-2010.

[3] HyperTranspon Technology Consortium. Hyper TransportTM1/O Link Specification Revision 1.03.http://www.bypertransprot.org/default.cfm?page=Hyper[EB/OL].TransportSpecificationslx, 2008-11-20.

Research of Parallel Redundant Computer System Based on Domestic CPU

Huang Chen, Wang Wenming, Zhang Yichao, Yue Wei

(BeiJing Institute of Aerospace Systems Engineering,Beijing 100076,China)

The construction of the domestic information system at present the country continues to advance, the core of the domestic computer system due to the low degree of technological maturity, market promotion and other reasons later exposed, low reliability, poor stability, led directly to the system function cannot be successfully applied. The parallel redundant architecture research on localization of computer system, the hardware and software design of computer system architecture, application and conversion mechanism method of cache coherence architecture, high-speed interconnection bus and three state, domestic CPU parallel computer system based on redundancy, can effectively eliminate the backup computer system on duty when switching the switch time delay the problem of data loss and switching process. Through the test, the system can complete the fault-tolerant computer system of CPU processor and the function of bridge chip fault modes, and ensure the completeness and timeliness of information data, effectively improving the working reliability and stability of the computer system in equipment.

parallel redundant computer system; HyperTransport bus; cache coherent protocol

2017-02-13;

2017-03-31。

黃 晨(1986-),男,山東龍口人,工程師,主要從事重點研究信息應用系統線路綜合設計方向的研究。

1671-4598(2017)07-0257-03

10.16526/j.cnki.11-4762/tp.2017.07.064

TP3

A