PCB阻抗測試模塊設計研究

藍春華 張鴻偉 張柏勇

摘要:信號高頻、高速化發展對PCB阻抗精度要求越來越高。常用PCB阻抗測試模塊設計方法缺乏阻抗測試模塊的精細化設計,因此測試模塊中的測量值不能高精度體現出PCB實際的阻抗值。文章從阻抗線長度、阻抗線尾部狀態、阻抗測試孔隔離環寬、阻抗線與周邊鋪銅間距共四個因素設計不同的阻抗測試模塊,研究與實驗PCB阻抗測試模塊的最佳設計。

關鍵詞:阻抗測試模塊;阻抗線;阻抗值

Abstract:Signals high frequency, high speed development of PCB impedance accuracy requirements are getting higher and higher.The commonly used PCB impedance test module design method lacks the fine design of the impedance testing module, so the measured values in the test module can not reflect the actual impedance value of PCB.In this article shows four different factors design of impedance test module :the impedance line length, line tail status, test hole isolation ring width, line and the surrounding copper spacing, study and do Experiments to choice the best disgn for PCB impedance test module.

Key words:Impedance test module; impedance line; impedance value

信號高頻、高速化發展對信號的完整性要求越來越嚴格,對PCB阻抗精度提出更高的要求。承載PCB主要信號傳遞的是阻抗線部分。基于PCB有效單元內的阻抗線難以單獨測量,在PCB工作拼版有效單元中設計相同條件的阻抗測試模塊,在PCB蝕刻后和阻焊后對阻抗測試模塊測量。傳統PCB阻抗測試模塊設計在PCB工作拼版的中間位置,為改善阻抗線和阻抗線周邊位置的鍍銅均勻性,通常在阻抗線邊緣設計鋪銅,對測試模塊中的阻抗線長短、測試孔隔離環寬、鋪銅與阻抗線的間距等工程設計方面,缺乏精細阻抗測試模塊設計,因此測試模塊中的測量值不能高精度體現出PCB實際的阻抗值。本文從阻抗線長度、阻抗線尾部狀態、阻抗測試孔隔離環寬、阻抗線與周邊鋪銅間距共四個因素設計不同的阻抗測試模塊,研究與實驗PCB阻抗測試模塊最佳設計,為阻抗PCB工程設計優化提供依據。

1 實驗

1.1 實驗工程設計

從阻抗線長度、阻抗線尾部狀態、阻抗測試孔隔離環寬 、阻抗線與周邊鋪銅間距共四個方面的影響因素,設計不同規格的阻抗測試模塊,具體如表1所述。

1.2 實驗板設計

(1)將以上四種阻抗測試模塊均設計在PCB工程拼版上,同時板邊設計距離有效測試模塊50mm以上,使各測試模塊的介質厚度、銅厚、線寬、油墨厚度以及DK值都處于相同條件。

(2)四種測試模塊在板邊、板中均有設置,防止因板內分布不同導致阻抗值偏差。

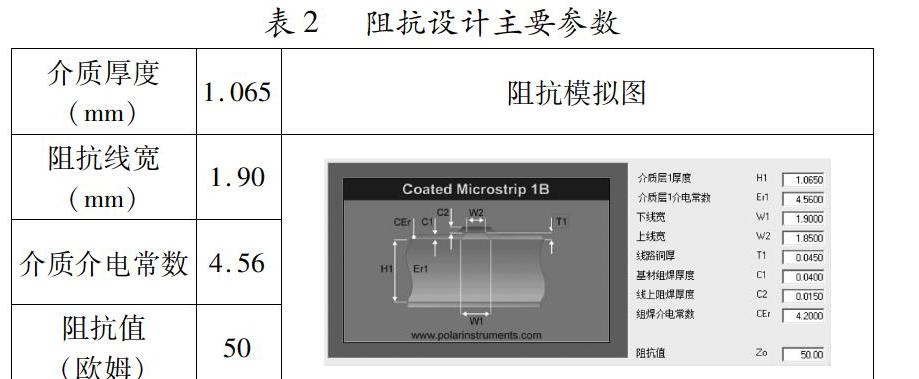

(3)為防止介質厚度不均導致阻抗值偏差,實驗板不采用壓合流程,直接使用雙面板工藝流程。設計1.10mm厚度(含銅)的雙面阻抗測試板實驗,阻抗測試模塊以50歐姆的單線阻抗為研究對象。

1.3 實驗材料

選用常規FR4基板,基板厚度1.10mm,底銅厚度為Hoz,介電常數值4.56。

1.4 流程設計

開料→鉆孔→化學鍍銅/板電→圖形線路→圖電→蝕刻→阻焊→阻抗測試。

2 實驗結果

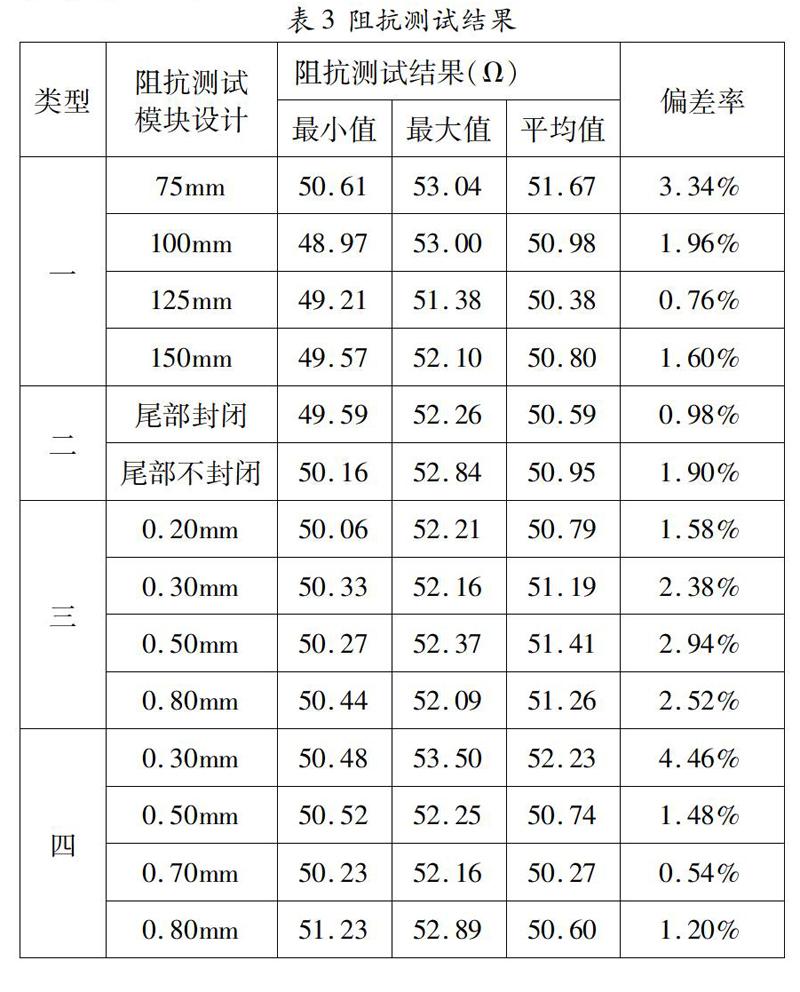

每種阻抗測試模塊的50個測量數據的平均值,與設計要求中值對比,最接近中值得測試數據為最佳設置條件。實驗板完成阻焊制作后阻抗測試結果如表3所述。

3 結論

通過以上研究與實驗,可以得出以下結論:

(1)從阻抗測試模塊的阻抗線長度的實驗數據來看,阻抗線長度在100mm以上接近阻抗中值,其中125mm最接近中值。

(2)從阻抗測試模塊的阻抗線狀態中尾部封閉的阻抗值較接近中值,無明顯影響阻抗差異不大。

(3)從阻抗測試模塊的四種隔離環大小,0.20mm的隔離環阻抗值最接近中值。

(4)從阻抗測試模塊的鋪銅與阻抗線的間距0.70mm的阻抗,最接近中值。

綜上所述,PCB工作拼版中的阻抗測試模塊最佳設計:阻抗線長度125mm、測試孔隔離環0.20mm,阻抗與銅皮的間距0.70mm。

作者簡介:藍春華,研發部工程師,主要負責新產品、新技術、新工藝開發以及重點客戶產品導入等工作。