基于0.18μm CMOS工藝的鎖相環頻率綜合器設計

馬意彭 葛飛翔

摘要 本文設計了一種基于3.3V0.18umCMOS工藝的鎖相環頻率綜合器電路,該電路的壓控振蕩器部分采用LC型壓控振蕩器,保證了高諧振頻率與低相位噪聲。鎖相環頻率綜合器輸出頻率在0.9GHz-9.2GHz之間,相位噪聲為-95dB,鎖定時間為6.1 μs,適用于時鐘頻率在1. 2GHz-9CHz之間的應用場合。

【關鍵詞】鎖相環頻率綜合器電路 LC型壓控振蕩器 相位噪聲

在現代無線通信系統中,穩定的本地震蕩源是影響通信效果的重要模塊。常見的穩定震蕩源是晶體震蕩電路,然而晶體振蕩器除了可以使用數字電路分頻以外,其頻率幾乎無法改變。鎖相環( Phase Locked Loop)的提出解決了上述問題,并在電子設備中得到了廣泛的應用。

隨著集成電路工藝的飛速發展,基于CMOS工藝的鎖相環頻率綜合器逐漸成為研究熱點。本文設計了一種基于0.18umCMOS工藝的鎖相環頻率綜合器電路,并完成了對該電路進行了仿真分析。

1 電路設計

1.1 鎖相環頻率綜合器的基本結構設計

鎖相環電路是一個相位同步的自動控制電路,其基本組成模塊包括鑒相鑒頻器( PhaseFrequencyDetector,PFD)、 電荷泵(ChargePump,CP)、環路濾波器(Loop Filter,LPF)、 壓控振蕩器(Voltage ConrrolledOscillator,VCO) 和分頻器(Divider,DIV)。其工作原理如下:首先PFD將參考信號REF與反饋信號FB的頻率和相位進行比較,控制CP對LPF進行充放電;LPF可將CP的電流信號轉換成電壓信號,并產生一個比較穩定的直流電壓VC控制VCO的輸出頻率Fo;Fo經過DIV后參數FB并輸入PFD完成循環過程。當FB與REF的相位差不為0時,鎖相環由負反饋機制自動調節,直至FB與REF的相位差為0,Ve保持恒定,vco的輸出頻率穩定。

1.2 PFD、CP與LPF電路設計

鑒相鑒頻器通常由兩個D觸發器和一個與門構成。兩觸發器的D端接高電平,CLK端分別接參考信號REF端和反饋信號FB端;兩個觸發器的輸出端UP與DOWN均與與門的輸入端相連,與門的輸出端同時接兩觸發器的RST端。UP端與DOWN端分別控制CP的充電開關和放電開關,兩開關分別用PMOS管和NMOS管實現。充電開關和放電開關的開合可對后級電容充電和放電。LPF使用二階低通濾波器,其作用是將電荷泵后級電容輸出電壓中的高頻成分濾除,使得輸入VCO的控制電壓VC更加平穩。

1.3 VCO電路設計

VCO是整個鎖相環頻率綜合器的核心模塊,其工作頻率范圍直接決定了鎖相環頻率綜合器的工作頻率。常見的VCO分為環形VCO和LC型VCO兩大類,其中,環形VCO多為三個以上延時單元級聯而成,優點是占用面積較小、功耗較低,缺點是震蕩頻率較低、相位噪聲較大。LC型VCO主要由高0值電感和可變電容陣列組成,并利用MOS交叉耦合負阻管提供震蕩所需的能量,交叉耦合負阻管的結構包括雙NMOS管、雙PMOS管和NMOS/PMOS互補管三種。本文采用NMOS/PMOS交叉耦合負阻電路。

1.4 分頻器電路設計

分頻器根據結構類型可分為模擬分頻器和數字分頻器,根據分頻比可分為整數分頻器和小數分頻器。本文使用固定分頻比為20的整數分頻器。該分頻器由6級D觸發器構成。D觸發器的電路結構使用文獻中的新型半靜態低功耗D觸發器電路,該電路具有功耗低、面積小、速度快等優點。

2 電路仿真

由Cadence Virtuoso仿真本鎖相環頻率綜合器,仿真結果如下:

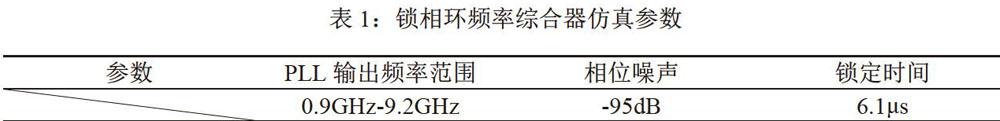

2.1 FPD與CP聯合仿真

t=0時,在PFD的REF端和FB端加兩個頻率不同的方波激勵源,在F4um時倒換兩激勵源,仿真結果如圖1所示。由圖1可以明顯地看出CP的充電與放電過程。

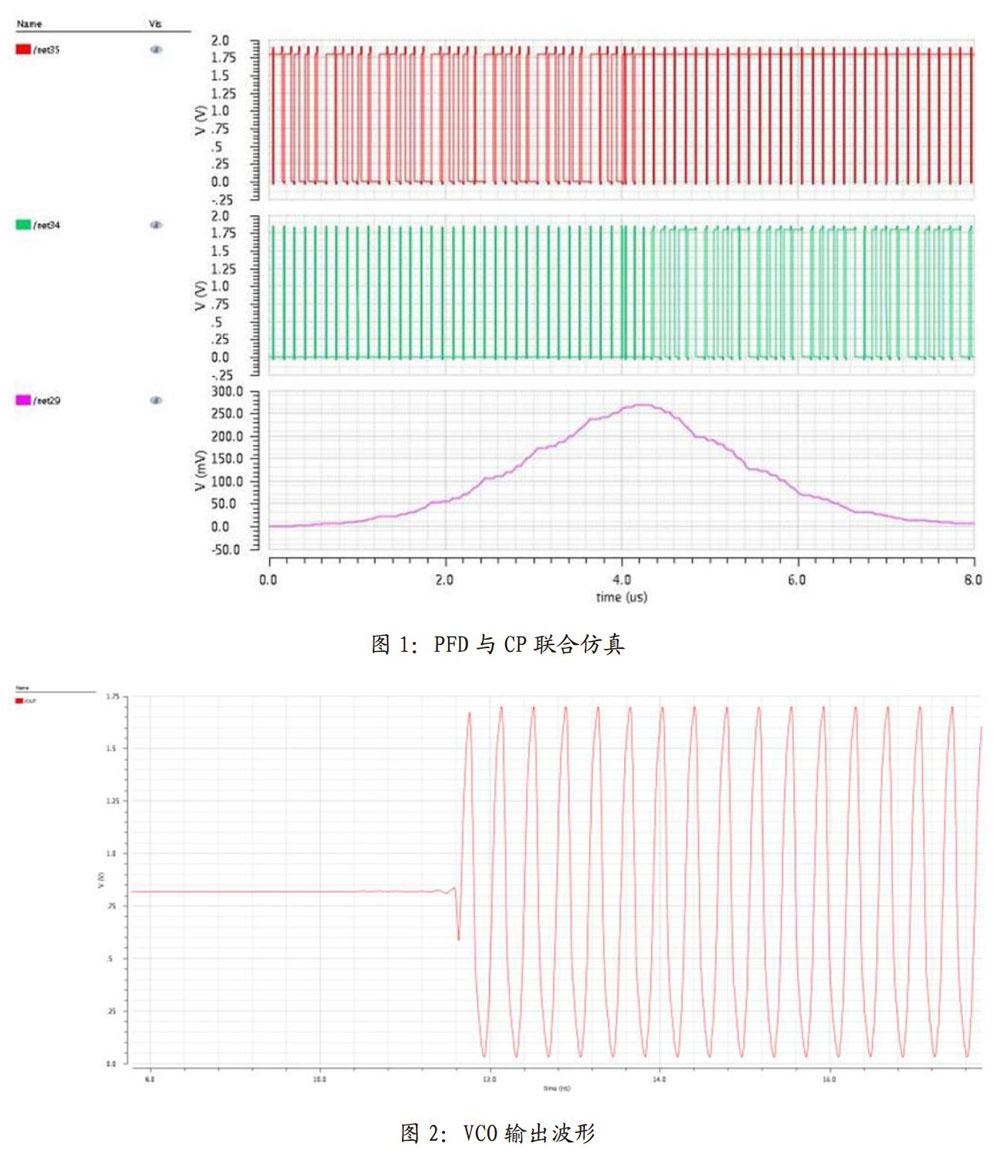

2.2 VCO仿真

使VCO的VC端電壓為0.2V,其輸出波形如圖2所示。由圖2可以看出,在Vc=0.2V時,vco輸出1GHz正弦波,且輸出的波形沒有明顯失真。

2.3 鎖相環頻率綜合器仿真

聯合仿真結果見表l。

由表1可以看出,鎖相環頻率綜合器的輸出頻率在0.9GHz-9.2GHz之間,帶寬較寬;相位噪聲為-95 dB,噪聲性能較好;鎖定時間為6.lμs,鎖定速度快。

3 結論

本文設計了一種基于0.18umCMOS工藝的鎖相環頻率綜合器電路,輸出頻率在0.9GHz-9.2GHz之間,相位噪聲為-95dB,鎖定時間為6.lμs,適用于時鐘頻率在1.2GHz-9GHz之間的應用場合。

參考文獻

[1]李劍宏.13GHz VCO及鎖相環設計[D].東南大學,2016.

[2]鮑進華,呂蔭學,李博等.一種基于標準CMOS工藝實現的鎖相環電路[J].電子設計工程,2016,24 (02): 90-92.

[3]曲明,翟越,王楠,基于射頻收發應用的低噪聲頻率綜合器設計[J].無線電通信技術,20 7,43 (03): 76-80.

[4]鄧賢進,李家胤,張健,鎖相頻率合成器相位噪聲的精確估計與仿真[J].西南科技大學學報(自然科學版),2006,21(01):128-131.

[5]張淑娥,王丹,基于LTC15 62的諧振器設計與實現[J].無線電工程,2011,41 (11):40-42.

[6]劉欣,歐陽萍.基于YIG振蕩器的寬帶頻率綜合器設計[J].無線電工程,2012,42 (02):58-61.

[7]王倫耀,吳訓威,葉錫恩,新型半靜態低功耗D觸發器設計[J].電路與系統學報,2004,9 (06): 26-28.