基于FPGA的DDS實(shí)驗(yàn)裝置設(shè)計(jì)

劉文樂(lè) 尚明健

摘 要:本文論述的一種基于FPGA的DDS實(shí)驗(yàn)裝置設(shè)計(jì)思路,裝置硬件結(jié)構(gòu)設(shè)計(jì)和FPGA片內(nèi)數(shù)字電路設(shè)計(jì),該裝置由電源板、DAC信號(hào)發(fā)生器、FPGA最小系統(tǒng)組成,波形數(shù)據(jù)則由CORDIC算法模塊的數(shù)據(jù)經(jīng)過(guò)變換后得到,在使用時(shí)通過(guò)設(shè)置所需波形的頻率,相位的信息即可得到相應(yīng)的方波或正弦波。

關(guān)鍵詞:FPGA;DDS;CORDIC算法

直接數(shù)字式頻率合成器DDS(Direct Digital Synthesizer)與采用模擬技術(shù)的頻率合成器相比,DDS具有成本低、分辨率高、功耗低、轉(zhuǎn)換快速等優(yōu)點(diǎn),可以產(chǎn)生方波或正弦波或任意波形應(yīng)用廣泛[1,2]。目前DDS信號(hào)發(fā)生器多采用MCU或FPGA外加DAC的方式進(jìn)行設(shè)計(jì),近年來(lái)由于FPGA的發(fā)展,采用FPGA設(shè)計(jì)DDS的案例也逐漸增多[3,4]。本實(shí)驗(yàn)裝置在設(shè)計(jì)時(shí)參考了國(guó)內(nèi)一些成功的設(shè)計(jì),采用FPGA加8位高速DAC的方式實(shí)現(xiàn),具備兩個(gè)通道,主要由FPGA最小系統(tǒng)板、DAC信號(hào)發(fā)生器、電源板組成,組合方便。

1 系統(tǒng)整體結(jié)構(gòu)和工作原理

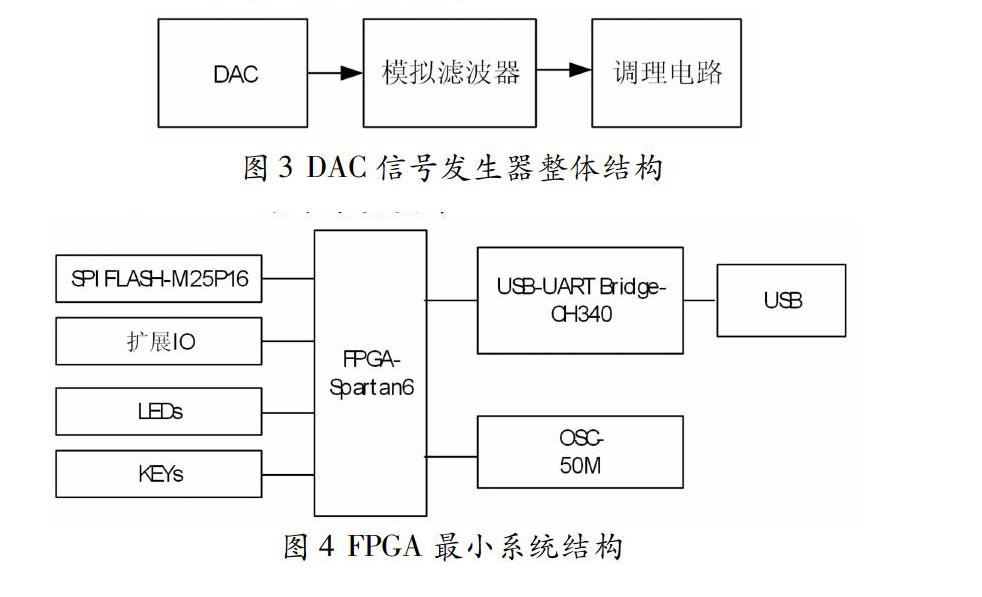

如圖1所示系統(tǒng)整體結(jié)構(gòu)由電源板,DAC信號(hào)發(fā)生器,F(xiàn)PGA最小系統(tǒng)構(gòu)成。電源板用于給FPGA最小系統(tǒng)和DAC信號(hào)發(fā)生器供電,為簡(jiǎn)化實(shí)驗(yàn)流程,保證實(shí)驗(yàn)的安全性,電源板采用單路5V輸入,這樣使用普通的5V電源適配器或USB電源即可給系統(tǒng)供電;DAC信號(hào)發(fā)生器采用8位高速DAC完成數(shù)模轉(zhuǎn)換,經(jīng)過(guò)模擬重構(gòu)濾波器濾除信號(hào)中的高頻成分,再經(jīng)過(guò)運(yùn)放調(diào)理電路,得到所需幅值的信號(hào);FPGA最小系統(tǒng)用于接收并解析用戶(hù)的指令,經(jīng)過(guò)FPGA內(nèi)部的算法運(yùn)算得到需要發(fā)送至DAC的值。

1.1裝置硬件結(jié)構(gòu)設(shè)計(jì)

1.1.1電源板設(shè)計(jì)

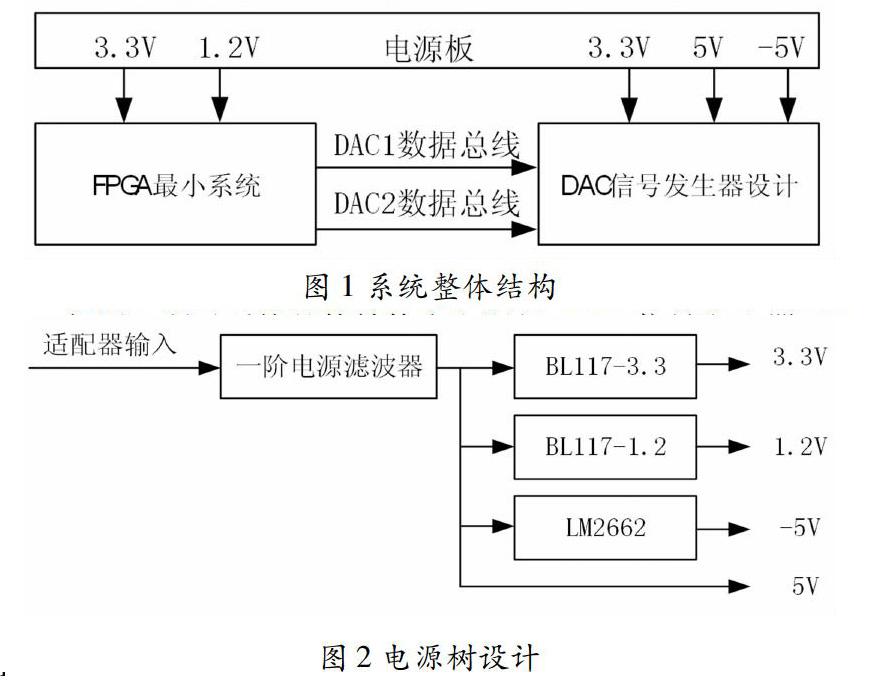

電源板用于為整套實(shí)驗(yàn)裝置供電,其中FPGA需要3.3V的BANK電壓與1.2V的CORE電壓,DAC信號(hào)發(fā)生器中使用的DAC芯片需要3.3V供電,但是運(yùn)放在工作時(shí)需要+/-5V供電,所以電源板在進(jìn)行設(shè)計(jì)時(shí),需要同時(shí)提供3.3V、1.2V、-5V以及+5V這4種電平,為保證實(shí)驗(yàn)裝置使用的便利性使用單路5V供電,采用的如圖2所示的電源樹(shù)設(shè)計(jì)。其中一階電源濾波器對(duì)5V適配器的

輸入進(jìn)行濾波,一階電源濾波器的輸出即可直接使用,3.3V和1.2V分別由BL1117-3.3和BL1117-1.2提供,BL1117是一款雙極型低壓差的線(xiàn)性穩(wěn)壓器,具有過(guò)流保護(hù)和過(guò)熱保護(hù)功能,在系統(tǒng)中使用LDO供電是因?yàn)長(zhǎng)DO的電源紋波小,外圍電路簡(jiǎn)單,易于減小裝置體積,但是由于要找到一款可以將+5V 電源輸入轉(zhuǎn)換為-5V 輸出的LDO非常困難,所以采用LM2662提供-5V,LM2662為電荷泵,工作頻率可調(diào),在電路板布局恰當(dāng)?shù)那闆r下輸出即為穩(wěn)定的-5V。

1.1.2 DAC信號(hào)發(fā)生器設(shè)計(jì)

如圖3所示,DAC信號(hào)發(fā)生器由高速DAC,模擬濾波器,調(diào)理電路組成,其中模擬濾波器采用低通設(shè)計(jì),并不可省去否則由于高速ADC內(nèi)部的零階保持器的作用,輸出信號(hào)會(huì)呈現(xiàn)階梯狀,調(diào)理電路中運(yùn)放的選擇為AD8047高速電壓反饋運(yùn)算放大器,DAC為AD9708高速DAC,AD9708 為ADI公司生產(chǎn)的高性能電流輸出DAC,依照ADI公司的介紹該DAC芯片采用分段電流源架構(gòu)與專(zhuān)有開(kāi)關(guān)技術(shù)相結(jié)合,可減小雜散分量,其阻抗大于100 kΩ,支持最高125 MSPS的更新速率。

在實(shí)際使用中以一定的采樣率使用DAC芯片會(huì)得到重構(gòu)的模擬信號(hào),但是此時(shí)直接使用示波器進(jìn)行測(cè)量,會(huì)發(fā)現(xiàn)輸出波形有一些小的臺(tái)階,這是DAC芯片的零階保持造成的,要解決這一問(wèn)題一般采用的方法是在DAC的輸出增加一個(gè)模擬重構(gòu)濾波器或一階保持電路,在本裝置中使用的是模擬重構(gòu)濾波器的方式,但是由于系統(tǒng)配置DAC芯片的更新速率為102.778MSPS(為了使分頻準(zhǔn)確,理想的更新速率應(yīng)該為102.4MSPS,但是由于FPGA內(nèi)部的PLL只能以特定的整數(shù)值對(duì)輸入時(shí)鐘進(jìn)行倍頻或分頻,所以只可得到102.778MSPS的時(shí)鐘),而輸出信號(hào)則在50Hz-8MHz可調(diào),此時(shí)使用有源濾波器有較大的設(shè)計(jì)難度,所以裝置采用無(wú)源巴特沃斯濾波器作為模擬重構(gòu)濾波器使用。

1.2.3 FPGA最小系統(tǒng)設(shè)計(jì)

FPGA最小系統(tǒng)的主要作用是產(chǎn)生波形數(shù)據(jù),所以其設(shè)計(jì)應(yīng)當(dāng)小巧,方便與DAC信號(hào)發(fā)生器連接,但是又要具備完整的功能,能夠與用戶(hù)交互,且便于讀取系統(tǒng)的工作狀態(tài)。FPGA最小系統(tǒng)結(jié)構(gòu)如圖4所示,M25P16用于固化FPGA 的程序,擴(kuò)展IO用于連接高速DAC,USB轉(zhuǎn)串口用于連接PC機(jī),接收控制指令,F(xiàn)PGA在接收到控制指令后依據(jù)相應(yīng)的指令設(shè)定輸出波形的種類(lèi),頻率,此時(shí)系統(tǒng)的工作狀態(tài)由LED顯示,F(xiàn)PGA 的外部時(shí)鐘由50M有源晶振提供。FPGA采用Xilinx公司設(shè)計(jì)的Spartan-6低功耗FPGA,該型號(hào)的FPGA采用45nm技術(shù),成本較低,適合用于設(shè)計(jì)中小規(guī)模的數(shù)字邏輯系統(tǒng)。

1.2 FPGA片內(nèi)數(shù)字電路設(shè)計(jì)

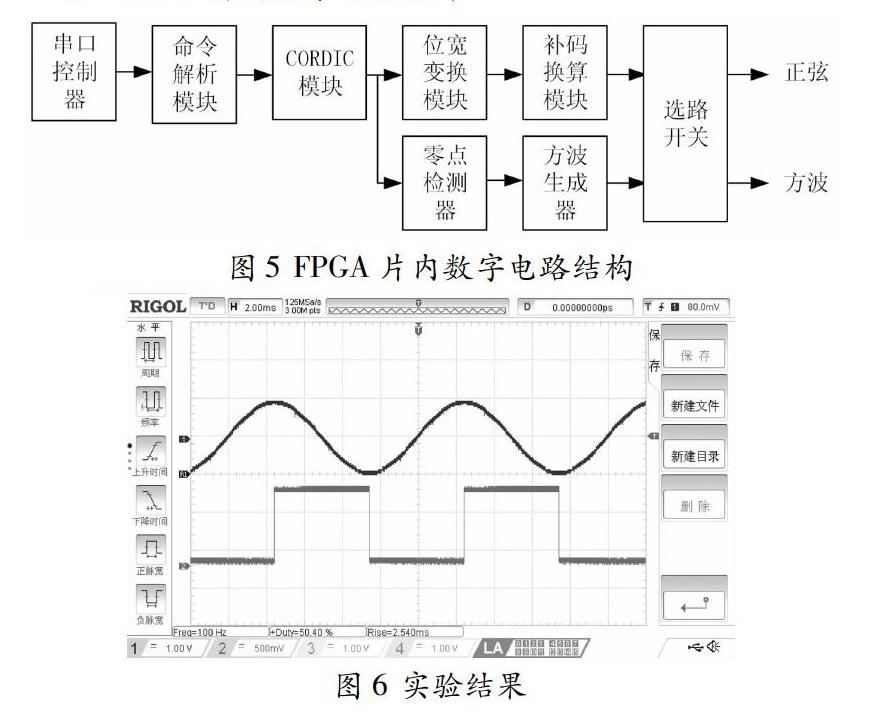

FPGA片內(nèi)數(shù)字電路結(jié)構(gòu)如圖5所示,為了讓參與者在實(shí)驗(yàn)過(guò)程中能夠更好地理解數(shù)字信號(hào)處理方面的知識(shí),實(shí)驗(yàn)裝置沒(méi)有采用常見(jiàn)的查表法產(chǎn)生波形數(shù)據(jù),而是采用了如下方法:首先通過(guò)CORDIC模塊產(chǎn)生頻率與初始相位一定的正弦信號(hào),通過(guò)位寬變換使得到的數(shù)據(jù)滿(mǎn)足DAC的8位數(shù)據(jù)位寬,由于此時(shí)的數(shù)據(jù)還是采用補(bǔ)碼方式表示,所以在輸出前要進(jìn)行換算,經(jīng)過(guò)變換得到的數(shù)據(jù)即為所需的正弦波數(shù)據(jù);方波的產(chǎn)生則是先利用零點(diǎn)檢測(cè)器對(duì)CORDIC模塊輸出的正弦波進(jìn)行過(guò)零點(diǎn)檢測(cè),如此便可確定輸出信號(hào)的頻率,進(jìn)一步變換得到所需的方波。

2 實(shí)驗(yàn)結(jié)果分析

利用設(shè)計(jì)的DDS實(shí)驗(yàn)裝置,通過(guò)串口向FPGA發(fā)送參數(shù)設(shè)置的控制指令,以實(shí)現(xiàn)波形的輸出功能,其中,波形頻率范圍為50Hz-8MHz。以100Hz為例的實(shí)驗(yàn)結(jié)果如圖6所示,從圖中可以看出:經(jīng)過(guò)配置后通道一輸出正弦波,通道二輸出方波,且輸出波形穩(wěn)定。該實(shí)驗(yàn)說(shuō)明了該實(shí)驗(yàn)裝置的各個(gè)硬件模塊工作正常,且FPGA產(chǎn)生了正確的波形數(shù)據(jù)。

3 結(jié)論

從實(shí)驗(yàn)效果上看,所設(shè)計(jì)的DDS實(shí)驗(yàn)裝置工作良好,兩個(gè)通道經(jīng)過(guò)配置,便可以自由輸出一定頻率的正弦波和方波。由于CORDIC算法在產(chǎn)生正弦波形數(shù)據(jù)過(guò)程中不過(guò)多消耗FPGA片內(nèi)存儲(chǔ)資源,只需要進(jìn)行移位和加減運(yùn)算,降低了FPGA的片上資源消耗;使用比較法產(chǎn)生方波,也不需要額外存儲(chǔ)方波的數(shù)據(jù),簡(jiǎn)化了系統(tǒng)結(jié)構(gòu)。本實(shí)驗(yàn)裝置在減小裝置體積的前提下,保證了功能的完整,可作為低成本的信號(hào)源使用。

參考文獻(xiàn):

[1]胡力堅(jiān).基于DDS的任意波形發(fā)生器設(shè)計(jì)與實(shí)現(xiàn)[D].西安電子科技大學(xué),2009.

[2]陳科,葉建芳,馬三涵,等.基于DDS+PLL技術(shù)頻率合成器的設(shè)計(jì)與實(shí)現(xiàn)[J].國(guó)外電子測(cè)量技術(shù),2010,29(4):43-47.

[3]黃燕.基于FPGA的DDS信號(hào)發(fā)生器的研究[D].南京林業(yè)大學(xué),2012.

[4]鄧耀華,吳黎明,張力鍇,等.基于FPGA的雙DDS任意波發(fā)生器設(shè)計(jì)與雜散噪聲抑制方法[J].儀器儀表學(xué)報(bào),2009,30(11):2255-2261.

作者簡(jiǎn)介:劉文樂(lè)(1963-),本科,高級(jí)工程師,研究方向?yàn)樗喙に囋O(shè)備電氣自動(dòng)化設(shè)計(jì)與控制。

*通訊作者:尚明健。