一種低功耗數據路徑綜合的迭代改進算法?

潘 鋒

(四川信息職業技術學院 廣元 628040)

1 引言

低功耗是超大規模集成電路(VLSI)設計的重要指標[1]。在電力消耗中最節省的往往是在更高層次的設計中[2]。本文將重點放在行為合成過程中,將其作為一個設計的行為描述,并生成一個實現指定行為的寄存器傳輸級(RTL)電路[3]。行為綜合可以細分為幾個任務,包括模塊選擇、時鐘選擇、調度和分配。其中,這些任務相互作用,單獨解決每個任務可能會影響設計的質量。文獻[4]中給出了動力優化方面的開拓性工作,它使用數據路徑復制和流水線來支持電源電壓伸縮。文獻[5]中提出了使用多種變換來降低功耗的方法。同時,正確的模塊選擇[6]、調度和分配[7~8]也被利用在電力消耗減少中。雖然上述所有方法都執行了一些行為合成任務的子集,通過減少供電電壓或減少開關電容來降低功耗,但很少有人考慮各種任務的相互作用所涉及的權衡。

本文提出了一種用于低功耗數據路徑合成的迭代改進算法,該算法執行調度、時鐘選擇、模塊選擇和資源分配,目標是減少功耗。并且它可以同時執行這些任務,從而探索這些任務相互依存性。

2 理論基礎

行為描述可以編譯成一個控制數據流圖(CD?FG),它是一個有向圖,由算術、邏輯、比較操作、延遲操作符、特殊的分支、合并、循環入口和出口組成頂點,它們代表控制流結構[9]。CDFG包含數據控制,它表示數據控制操作之間的關系[10]。圖1中所示的CDFG為兩個向量點積的計算。

圖1 CDFG時間表與任務的點積計算

在本研究中數據控制的行為描述在數字信號和圖像處理應用中是很常見的。這些描述的兩個重要特征是:1)它們主要包括算術運算,如加法、乘法和延遲運算符等[11];2)輸入采樣周期的約束在下一次輸入樣例到達之前處理輸入的速度是固定的,但是處理輸入樣本的速度并不比要求的速度快[12]。

平均開關電源在CMOS技術的中占主導地位的功耗為

其中,CL為門電路輸出電容,Vdd是電源電壓,N是周期T操作期間門輸出的過渡數,電力消耗方程表明,由于其二次貢獻[13],供電電壓Vdd對功耗有很強的影響,與此同時,電路的延遲會增加。CMOS的門延遲可以表示為

其中,Vth為設備的閾值電壓,k是依賴于柵極技術和晶體管尺寸的常數。因此,只有當延遲降級不會導致延遲超過指定的約束,或者使用其他方法來防止延遲降級時,才執行Vdd擴展。物理電容CL和過渡活動N的乘積稱為交換電容,開關電容項的影響雖然不像供應電壓那樣劇烈,但也可以用于降低功耗。

2.1 調度操作

調度過程決定了CDFG的循環周期行為,它將CDFG中的每個操作分配給一個或多個周期進行控制步驟。圖1顯示了示例CDFG的進度信息。標記為數字的水平虛線表示時鐘的邊緣,即控制步驟之間的邊界。其中,+4將與+1、+2相同的控制步驟中執行,且時鐘周期為55ns。這種鏈鎖技術[14]使得“多環”進行一種互補的模式,即單個操作需要多個控制步驟來執行。結構流水線指的是在數據路徑中使用流水線執行單元。顯然,時鐘周期的選擇影響到操作的控制步驟分配,而在CDFG中每個操作的延遲也是如此。這些值分別由時鐘選擇和模塊選擇任務決定,在調度、模塊選擇和時鐘選擇之間建立相互依賴關系。在同一控制步驟中活動操作(變量)必須分配給不同的功能單元(寄存器)。例如,操作*1到*6必須由獨立的功能單元來執行。由于調度影響了處理輸入樣本的速率,且也影響了減少Vdd的可能性。另一方面,調度影響交換電容,因為它限制了資源共享的可能性。

2.2 模塊選擇

模塊選擇指的是在CDFG中選擇每一項操作的過程,即執行它的功能單元類型。為了充分探索設計空間,需要有不同的功能單元模塊庫存在多個模塊能夠執行每個操作(例如脈沖進位加法器、超前進位加法器,選擇加法器和陣列乘法器等[15])。

通過使用模塊選擇來執行區域、延遲和功率三者間的關系。模塊選擇與時鐘選擇、調度和資源共享交互。在圖2中,由于模塊選擇被改變,時鐘周期也改為30ns。在模塊選擇期間被分配給不同功能單元的操作不能共享相同資源。本研究的算法將考慮交互作用的影響,并且綜合數據路徑。

圖2 備用調度分配模式

2.3 時鐘選擇

時鐘選擇是指控制器/數據路徑電路選擇合適的時鐘周期過程。時鐘周期Tclk,本文將CDFG的執行時間等同于輸入采樣周期Ts,時鐘周期為Tclk時,控制步驟的數量為

其中,表示小于或等于x的最大整數。選擇時鐘周期后,根據控制步驟計算各功能單元模塊的延遲。

由于時鐘粒度在松弛因子的作用下可能會小于功能單元而被完全利用[16],這將導致CDFG執行所需的時間增加。在最大限度地減少功耗的情況下,松弛的時鐘粒度可以引起兩種不良影響:1)樣本周期不能滿足CDFG對Vdd的約束;2)導致具有更高開關容量的數據路徑。因此,從能源消耗的角度來看,在降低功耗時,單一目標松弛最小化的方法不能直接適用。為了降低功耗,在選擇時鐘周期的情況時,要盡量減少時鐘粒度的松弛性

2.4 資源共享

資源共享是指使用相同的硬件資源(功能單元或寄存器)執行不同的操作或多個變量存儲。資源共享嚴重影響功耗數據路徑中的電容和開關活動。其中,資源共享傾向于減少物理電容,但增加了數據路徑上的平均切換活動。稀疏共享架構的平均開關活動較低,但物理電容較高。本研究使用資源共享對開關電容信號統計的影響。

假設庫中的函數單元具有切換電容的一些模型,因此,給定一對輸入向量可以計算出功能單元中交換的電容。這個過程可以使用隨機功率分析模型來實現。由用戶提供或者根據已知的輸入特性生成輸入序列對CDFG進行功能模擬。在執行功能模擬時,使用CDFG中變量所取的值更新交換電容矩陣的數據結構。其中,交換電容矩陣將交換電容成本與可映射到同一資源的每一對操作相關聯,并為其在庫中的每個功能單元模塊創建一個單獨的切換電容矩陣。同時,還要考慮功能單元模塊、波紋進位加法器和加法運算的綜合作用。

3 改進算法

利用調度、時鐘選擇、模塊選擇和資源共享進行一種復雜的方式交互,以確定數據路徑的功耗。由于功耗最小化問題的計算復雜且不易得到最優解或精確解,因此,本研究開發一種有效的啟發式方法用于執行上述任務,以最大限度地減少功耗,目的使得Vdd擴展和交換電容減少。利用程序估計最小電壓Vmin,并由用戶設置Vmin和Vmax(5V)之間的電壓間隔△V。對于Vdd和電子密度圖CSTEPS的組合生成一個滿足樣本周期約束的初始值,通過調用迭代改進算法對數據路徑進行合成,目的是在當前Vdd和時鐘周期內合成滿足采樣周期約束的數據通路,并且具有最小的開關電容。在所有候選電源電壓和時鐘周期被修正后,最優方案Best_DP包含最終的解決方案。低功率合成方法記作SCALP。

3.1 電源電壓修正

電源電壓Vdd修正的目的是識別出候選供應電壓,這不會導致數據路徑的最低功率。本文所使用的Vdd修正方法是基于對當前Vdd的交換電容約束。通過將CDFG中的每一個操作映射到具有最低開關電容的功能單元模塊,并執行模塊選擇完成并行架構來實現數據路徑。由于并行架構通常接近最低的開關電容結構,因此計算過程中通常乘以一個修正系數λ(0≤λ≤1)來降低當前Vdd中數據路徑所消耗的能量,在本文中使用了λ取0.8。如果這樣計算的界限大于最好的解決方案,那么可以對當前的Vdd進行修正。

3.2 時鐘周期修正

給定一個理想的采樣周期Ts,對于時鐘周期Tclk滿足如下條件:

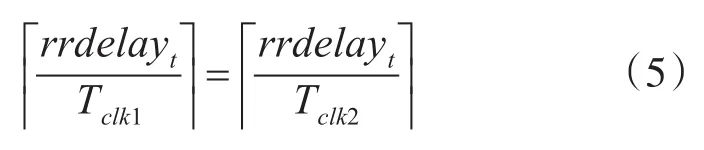

將候選時鐘周期的集合限制在有限的集合中,考慮兩個候選時鐘周期Tclk1和Tclk2,使得Tclk1<Tclk2。對于數據路徑庫中的每個功能單元模塊t,令rrdelayt表示寄存器之間的傳輸延遲,則

如果操作鏈接采用最大鏈接系數k,則式(5)計算的條件不僅對所有功能部件模塊適用,也可用于所有鏈接到k功能單元的組合模塊。

4 實驗分析

本文使用C++編程語言實現研究中所描述的SCALP方法。利用該方法從數字信號處理方面對SCALP進行綜合評價。SCALP輸入初始化CDFG和樣本周期,輸出數據路徑和控制器以共同實現CDFG所指定的行為。用于組合控制器和數據路徑的網表使用邏輯合成工具SIS將其映射到MSU標準單元庫中。最后使用OCT軟件中的標準單元格布局和路由工具來獲得組合控制器和數據路徑的布局。Switch模擬器在模擬運行過程中記錄交換電容,并用來執行布局中提取的交換機模擬。

將每個基準對應從1.0~3.5的松弛因子各種可能值。對于每個基準和松弛因子,由SCALP生成的能量優化體系結構,通過Vdd擴展的優化架構,使用與SCALP相似的方法進行區域優化。每個供應電壓的優化體系結構按樣本周期約束程度進行伸縮。由SCALP計算的控制器和電路數據路徑產生消耗的功率,見曲線S-POWER。Vdd放縮區域優化架構,見曲線A-POWER。由SCALP生成的控制器和數據路徑合成布局區域,見曲線S-AREA。三者的對比如圖3和圖4所示。

圖3 利用WDF濾波器進行實驗

圖4 利用Elliptic濾波器進行實驗

在圖3和圖4中,WDF是一種數字FIR濾波器。Elliptic是一種五階橢圓濾波器。面積曲線用虛線繪制,功率曲線用實線繪制。曲線表明:由SCALP合成的電路比優化電路的功率低7倍,電路消耗的功率比優化后的功率低2.3倍,且合成電路的開銷小于41%。從數值的平均角度觀察,在松弛因子分別為 1.0、1.5、2.0、2.5、3.0和 3.5條件下,SCALP計算出的數據路徑占區域面積分別為16%、24%、27%、24%、27%和27%。在128MB內存的SPARC上,CPU運行SCALP的時間小于20分鐘。

5 結語

本文從調度操作、模塊選擇、時鐘選擇和資源分配四個任務對數據控制行為進行了描述,并以減少電力消耗為目的,提出了一種高效的迭代改進算法。與之前的研究不同,本文還考慮了這些任務之間的交互作用,通過修正電源電壓和時鐘周期兩個因素,改進了交換電容產生功耗的數據路徑計算,實驗結果證明了算法的有效性。

參考文獻

[1]龐志勇,譚洪舟,陳弟虎.一種改進的低成本自適應雙三次插值算法及VLSI實現[J].自動化學報,2013,39(04):407-417.

[2]朱文興,程泓.VLSI電路劃分問題的分散搜索算法[J].電子學報,2012,40(06):1207-1212.

[3]李艷,張東曉,于芳.RTL綜合中FPGA片上RAM工藝映射[J].電子學報,2016,44(11):2660-2667.

[4]張露予,王博文,翁玲,等.螺旋磁場作用下磁致伸縮位移傳感器的輸出電壓模型及實驗[J].電工技術學報,2015,30(12):21-26.

[5]林志堂,郭昌堅,張朋濤.無線通信技術的低功耗處理技術研究[J].機電工程技術.2017(02):209-212.

[6]杜世民,夏銀水,黃誠,等.一種有效的面向軟模塊的VLSI布圖規劃算法[J].計算機工程與應用,2014,50(04):50-56,68.

[7]陶鈞,仇悅,沈海斌.傳感器網絡中圖像小波處理的低存儲硬件實現[J].傳感器與微系統,2013,32(09):16-20.

[8]路偉,余寧梅,南江涵,等.并行可配置的HEVC熵編碼的 VLSI結構[J].計算機工程與應用,2014,50(03):121-124,144.

[9]朱小茹,王興偉,張爽,等.基于SDN和接觸圖的空間信息網絡路由機制[J].計算機科學與探索,2017(08):1-8.

[10]張駿,陳實,郭岳東.基于Honeypot主動防御系統的數據控制設計[J].電腦與信息技術,2014,22(04):25-28.

[11]Sengupta A.Soft IP Core Design Resiliency Against Ter?restrial Transient Faults for CE Products[J].IEEE Con?sumer Electronics Magazine,2016,5(4):129-131.

[12]張珠庭.云計算數據控制層數據庫模型與節點構建研究[J].數字技術與應用,2013(12):39-40.

[13]趙軒.基于二叉樹算法數據控制層數據庫模型構建[J].計算機光盤軟件與應用,2013,16(19):157-158.

[14]McIVER W R,CARTER H R,HARVEY A L,et al.Use of social attraction to restore Ashy Storm-Petrels Oceanodroma homochroa at Orizaba Rock,Santa Cruz Is?land,California[J].Marine Ornithology,2016,44:99-112.

[15]姚茂群,張立彬,耿亮.電流型CMOS脈沖D觸發器設計[J].電子與信息學報,2014,36(09):2278-2282.

[16]陳銳,楊海鋼,王飛,等.基于粗粒度可重構陣列結構的多標準離散余弦變換設計[J].電子與信息學報,2015,37(01):206-213.