基于FPGA的LFSR結構偽隨機數發生器的實現*

彭雅嵐 肖順文

(西華師范大學 電子信息工程學院,四川南充 637009)

在計算機、通信系統中采用的隨機數均為偽隨機數[1],由線性反饋移位寄存器[2]所構成的偽隨機數發生器是擴頻通信系統中的核心。線性反饋移位寄存器是一種十分有用的時序邏輯結構,其結構簡單、速度快,它被廣泛應用于可編程分頻器、信道編碼、CRC(Cyclic Redundancy Check)校驗碼生成、密碼算法實現等多個方面[3-4]。本文基于FPGA(Field Programmable Gate Array)實現用N級線性反饋移位寄存器(Linear Feedback Shift Register, LFSR)產生偽隨機數組。

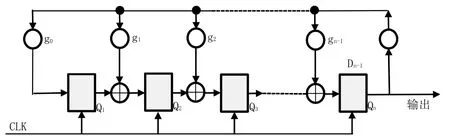

圖1 N級線性反饋移位寄存器結構圖

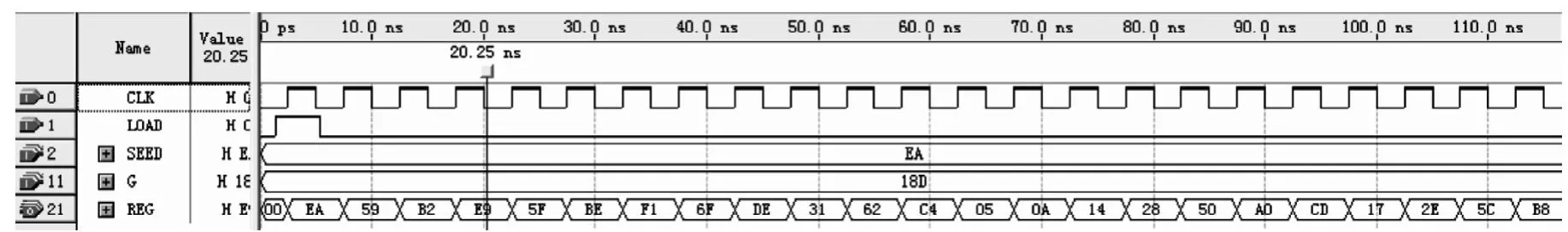

圖2 n=8,G=18DH,SEED=FFH時的仿真圖

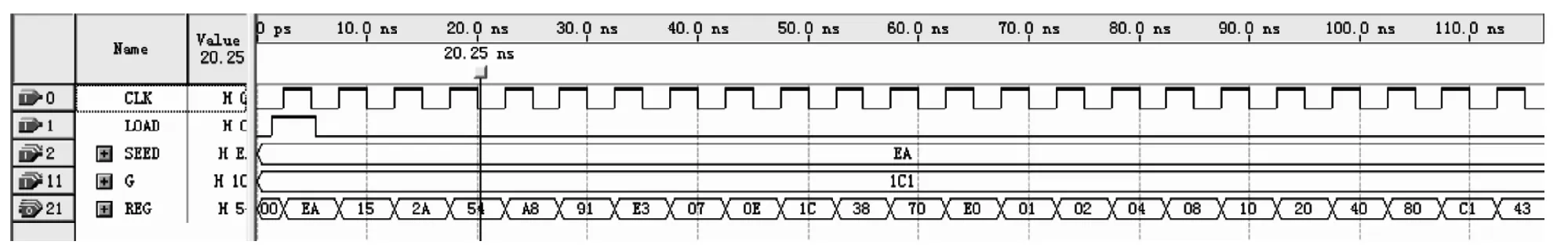

圖3 n=8,G=18DH,SEED=EAH時的仿真圖

1 設計原理

線性反饋移位寄存器是給定前一狀態的輸出,將該輸出的線性函數再用作輸入的移位寄存器。異或運算是最常見的單比特線性函數:對寄存器的某些位進行異或操作后作為輸入,再對寄存器中的各比特進行整體移位。圖1是由n個D觸發器和若干個異或門組成的線性反饋移位寄存器結構圖,其特性由移位寄存器級數(周期長度)、初始狀態(各寄存器的初始值)、反饋邏輯(異或邏輯)和時鐘周期共同決定[5]。

圖1中,Qi+1表示各級寄存器Di的輸出,gi為反饋系數,gi的取值決定了Qi是否參與反饋。gi只能取0或1,當gi=0時,表示Qi被斷開不參與反饋;當gi=1時,表示Qi將參與反饋。由于反饋的需要,其中gn與g0必須取1,使線性反饋移位寄存器的輸出端Qn參與反饋。移位寄存器的初始狀態由使用者設定,初值裝載完成后,每當時鐘周期CLK到來,移位寄存器移位一次,即若gi+1=1,則寄存器Di將其輸出值Qi+1(0或1)與Qn進行反饋邏輯(異或)運算后,傳遞給下一級寄存器Di+1;若gi+1=0,則寄存器Di直接將其內容傳遞給下一級寄存器Di+1。

2 設計方案

本文基于VHDL硬件描述語言設計了一個級數與反饋系數均可控的,由線性反饋移位寄存器所構成的偽隨機數發生器。參考文獻[6]介紹了多種VHDL的語法,這里采用了GENERIC參數定義語句,對級數N進行有效設定,并利用FOR_LOOP循環語句對反饋系數的值進行判斷后,再帶入反饋邏輯運算得到下一級寄存器的值。最后由用戶設定隨機種子的值,從而得到一系列偽隨機數。

部分VHDL源程序如下:

IF CLK'EVENT AND CLK = '1' THEN

IF LOAD = '1' THEN REGN <= SEED;ELSE

REGN(0) <= REGN(n-1);

FOR i IN n-2 DOWNTO 0 LOOP

IF G(i+1)='1' then

REGN(i+1) <=REGN(i) XOR REGN(n-1);ELSE

REGN(i+1) <=REGN(i);

END IF;END LOOP;END IF;END IF;

3 仿真與驗證

使用ALTERA公司的QUARTUS II 9.0軟件對所設計的線性反饋移位寄存器進行編譯和仿真。CLK為仿真時鐘信號,時鐘周期為5ns;LOAD是裝載數據的控制端,高電平有效;SEED為用戶選定的隨機種子;G為反饋系數的取值。

圖2為級數取8,隨機種子取11111111,反饋系數取110001101時產生的偽隨機數。

圖3為級數取8,隨機種子取11101010,反饋系數取110001101時產生的偽隨機數。

圖4為級數取8,隨機種子取11101010,反饋系數取111000001時產生的偽隨機數。

圖5為級數取16,隨機種子取FFFFH,反饋系數取18003H時產生的偽隨機數。

運用控制變量法,從上述四種不同條件下的仿真圖中可以看出,當將線性反饋移位寄存器的級數、反饋系數和隨機種子中任一項取不同值的時候均可以得到不同的偽隨機數組。

圖4 n=8,G=1C1H,SEED=EAH時的仿真圖

圖5 n=16,G=18003H,SEED=FFFFH時的仿真圖

4 結語

本文用VHDL語言設計了一種能有效產生偽隨機數的N級線性反饋移位寄存器,通過改變級數N、反饋系數G和隨機種子SEED的值可以得到多種多樣的偽隨機數。較其他線性反饋移位寄存器的設計來說,本設計的級數和反饋系數均可調,且設計過程簡單易懂,具有靈活性好,使用便捷的優點。

[1]劉沛華,魯華祥,龔國良,劉文鵬,陳天翔.基于FPGA的高速任意分布偽隨機數發生器[J].應用科學學報,2012,30(03):306-310.

[2]崔嵬,李承恕.線性反饋移位寄存器的改進算法及其電路實現[J].北方交通大學學報,2004(05):69-72.

[3]管超,周潤德,葛元慶.高速線性反饋移位寄存器的實現[J].微電子學,2000(04):241-243.

[4]鄭誠瑋,戴紫彬,李偉.面向可重構并行化處理的線性反饋移位寄存器統一架構研究[J].微電子學與計算機,2015,32(11):111-115.

[5]陳澄,張茂青,崔秀美.基于FPGA的可編程M序列發生器的設計[J].工業控制計算機,2013,26(06):15-16.

[6]潘松,黃繼業.EDA技術實用教程[M].科學出版社.2013.