一種寬帶高斯白噪聲的設(shè)計與實現(xiàn)

石遠東,盧雪怡,李 霄

(1.中國船舶重工集團公司第七二三研究所,江蘇 揚州 225101;2.江蘇科技大學(xué),江蘇 鎮(zhèn)江 212003)

0 引 言

干擾目前主要分為遮蓋性干擾和欺騙性干擾。遮蓋性干擾就是利用高干信比的噪聲信號遮蓋住目標回波,從而使雷達無法正常檢測目標。雷達接收機處理的信號是含有加性噪聲的,噪聲的隨機性越強,檢測結(jié)果的不確定性越高。在相同功率條件下,當噪聲信號服從高斯分布時,其不確定性最高,為最佳遮蓋干擾波形[1]。

高斯白噪聲可以通過模擬或數(shù)字的方法產(chǎn)生,目前的研究主要是基于數(shù)字合成方法開展的。數(shù)字合成的一般方法是先產(chǎn)生均勻分布的白噪聲,然后通過轉(zhuǎn)換將均勻分布變?yōu)楦咚狗植紡亩玫礁咚拱自肼暋N墨I[2]首先采用Tausworthe算法生成均勻分布的白噪聲,然后通過查表法實現(xiàn)均勻分布白噪聲到高斯白噪聲的轉(zhuǎn)化。文獻[3]則先采用lagged-Fibonacci算法生成均勻分布的隨機序列,然后通過公式法產(chǎn)生高斯白噪聲。而文獻[4]利用M序列發(fā)生器產(chǎn)生均勻分布隨機數(shù),通過15段折線逼近法實現(xiàn)了高斯白噪聲序列。

本文主要介紹了一種基于高性能現(xiàn)場可編程門陣列(FPGA)和高速數(shù)模變換器(DAC)的寬帶高斯白噪聲的快速產(chǎn)生方案。首先通過M序列發(fā)生器產(chǎn)生偽隨機序列,利用并行取樣的方法降低隨機數(shù)的相關(guān)性,再將數(shù)據(jù)送入系數(shù)可重新配置的多相濾波器,最后將多相濾波器輸出數(shù)據(jù)進行并串轉(zhuǎn)換后送高速DAC。設(shè)計方案首先使用 Matlab進行仿真驗證,然后采用VerilogHDL進行軟件編程和Modelsim仿真驗證,最終在印制板上進行了測試,驗證了方案的可行性。

1 基本理論

1.1 噪聲最佳干擾波形

衡量隨機變量不確定性的量是熵,對于連續(xù)型隨機變量:

(1)

式中:p(x)為隨機變量的概率分布密度函數(shù)。

當a取一確定值時,熵值越大,則說明隨機信號的不確定性越強;同時熵值還與隨機信號的方差(平均功率)有關(guān),方差越大,熵值也越大。因此噪聲的最佳干擾波形就是在噪聲功率限定的條件下,具有最大熵值的概率分布的噪聲信號。

根據(jù)Lagrange常數(shù)變易法,已知函數(shù)方程:

(2)

以及對應(yīng)的n個函數(shù)方程的約束條件:

(3)

式中:φ1,φ2,…,φn為約束條件中給定的函數(shù),則式(2)的最值可以由式(3)的n個方程和下式?jīng)Q定:

(4)

式中:λ1,λ2,…,λn為拉格朗日常數(shù)。

代入最大熵函數(shù)求解,取a=e,則已知:

(5)

從而有:

(6)

p(x)=eλ1-1+λ2x2

(7)

利用限制條件,可以得到:

(8)

(9)

因此,在噪聲功率限定的條件下,當噪聲服從高斯分布時,其熵值最大,是噪聲最佳干擾波形。

1.2 M序列發(fā)生器

偽隨機序列是具有某種隨機特性的確定的序列,它既具有隨機統(tǒng)計特性,又可以重復(fù)產(chǎn)生,因此獲得了廣泛的應(yīng)用。M序列就是一種常用的偽隨機序列,它是最長線性反饋移位寄存器的簡稱。M序列自Shannon信息論誕生后得到了廣泛研究,目前理論比較成熟,已得到廣泛應(yīng)用。線性反饋移位寄存器是產(chǎn)生M序列的主要功能模塊,如果線性反饋移位寄存器選擇的級數(shù)是n,則M序列的重復(fù)周期為2n-1。將M序列產(chǎn)生的數(shù)據(jù)看成無符號整數(shù),則數(shù)據(jù)的取值范圍為1~2n-1,并且在一個重復(fù)周期內(nèi),每一個無符號整數(shù)出現(xiàn)且只出現(xiàn)一次。因此利用M序列產(chǎn)生的數(shù)據(jù)是服從均勻分布的隨機數(shù)。

產(chǎn)生M序列的反饋移位寄存器的遞歸方程是:

an=cn-1an-1?cn-2an-2?...?c1a1?c0a0

(10)

式中給出了移位輸入an與移位前各級狀態(tài)a0,a1,…,an-1的關(guān)系。反饋系數(shù)c0,c1,…,cn-1確定了移位寄存器的反饋連接和序列的結(jié)構(gòu),取值為0或1。取值為0表示對應(yīng)的移位寄存器無饋線運算,取值為1表示對應(yīng)的移位寄存器參與反饋運算。反饋系數(shù)的取值可通過查找本原多項式來得到。n的取值決定了M序列的重復(fù)周期,為了使M序列的重復(fù)周期足夠長以滿足噪聲的設(shè)計要求,選取n=31,則序列周期可達2.147×109,F(xiàn)PGA系統(tǒng)時鐘為250 MHz,噪聲重復(fù)周期可達到8.59 s。

1.3 降低相關(guān)性處理

高斯白噪聲信號是一個隨機過程,假設(shè)其雙邊功率譜密度為常數(shù)N0,由于信號的自相關(guān)函數(shù)是功率譜密度的傅里葉反變換,將N0進行傅里葉反變換,得到高斯白噪聲的自相關(guān)函數(shù)為:

R(τ)=N0×δ(τ),-∞<τ<+∞

(11)

由式(11)可見,高斯白噪聲的自相關(guān)函數(shù)是一個δ(τ)的函數(shù),在任意2點不同時刻的采樣值的自相關(guān)值是零,這2個采樣值是完全獨立的。線性反饋移位寄存器每一節(jié)拍只將最高位an-1移出,并將反饋值an送給最低位a0。所以相鄰的采樣值仍然具有一定的相關(guān)性,不是完全獨立的。為了減小相鄰信號的相關(guān)性,需要做去相關(guān)處理。文獻[4]介紹了通過間隔r個時鐘周期(r=2i)進行采樣狀態(tài)值的方法來降低隨機序列的相關(guān)性。

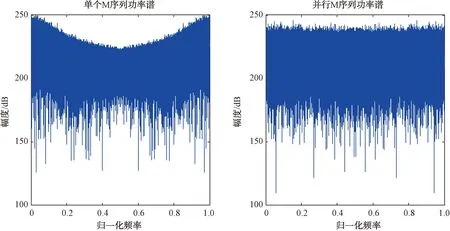

本文采用的是多路M序列并行產(chǎn)生隨機數(shù)的方法。當需要產(chǎn)生10 bit位的隨機數(shù)據(jù)時,使用10路M序列發(fā)生器并行處理,將10路M序列的最高位同時提取出來組成一個10 bit數(shù)據(jù)。這樣的10 bit數(shù)據(jù)只選取了每個M序列的一個狀態(tài)值,因此相鄰的數(shù)據(jù)是完全獨立的,沒有相關(guān)性。這10路M序列發(fā)生器需配置不同的反饋系數(shù),初值可以一樣。圖1分別顯示了單個M序列發(fā)生器產(chǎn)生10 bit隨機數(shù)和10路M序列發(fā)生器并行處理產(chǎn)生10 bit隨機數(shù)的功率譜。由圖1可知,采用M序列發(fā)生器并行處理產(chǎn)生的隨機數(shù)的功率譜基本水平。將功率譜進行傅里葉反變換,得到的信號近似一個δ(τ)的函數(shù),表明M序列發(fā)生器并行處理產(chǎn)生的隨機數(shù)任意2個不同時刻的采樣信號是相互獨立的,證明該方法降低隨機序列的相關(guān)性是有效的。

圖1 M序列功率譜

1.4 多相濾波處理

多路M序列并行產(chǎn)生隨機數(shù)的功率譜是基本水平的,要生成帶寬可調(diào)的數(shù)字噪聲序列需對產(chǎn)生的隨機數(shù)進行數(shù)字濾波,本文采用的是有限沖激響應(yīng)(FIR)數(shù)字濾波器。根據(jù)中心極限定理(CLT),大量獨立同分布的隨機變量之和必定是一個正態(tài)隨機變量。因此均勻隨機分布的隨機數(shù)經(jīng)過FIR數(shù)字濾波器后轉(zhuǎn)換成近似正態(tài)分布的隨機數(shù),而且隨著濾波器階數(shù)的增加,輸出噪聲的分布特性更接近高斯分布。FIR數(shù)字濾波器既實現(xiàn)了噪聲帶寬可調(diào)的功能,又完成了均勻噪聲向高斯白噪聲的轉(zhuǎn)換。

由于本文設(shè)計的噪聲數(shù)據(jù)率是2 Gsps,如此高速的數(shù)據(jù)無法用普通的FIR濾波器進行濾波,因此采用多相濾波器進行濾波。多相濾波的基本原理如下:設(shè)數(shù)字濾波器的沖擊響應(yīng)為h(n),則其z變換H(z)定義為:

(12)

令n=mD+k(m=0,1,2,…,M-1;k=0,1,2,…,D-1;N=MD),則式(12)可重新組織如下[5]:

(13)

(14)

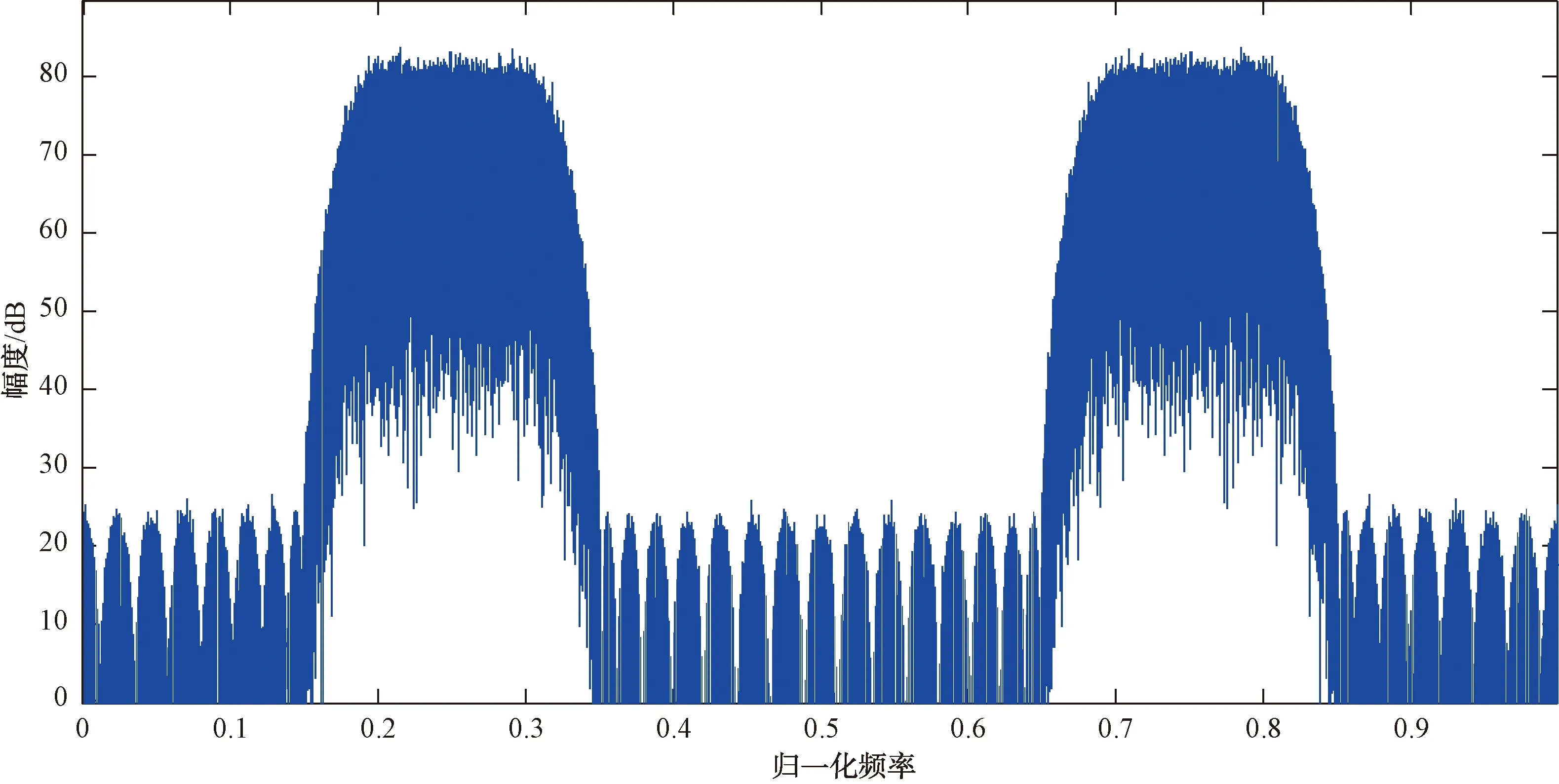

式(14)為數(shù)字濾波器H(z)的多相濾波結(jié)構(gòu)。在本文中N的值為32,D的值為8。圖2為隨機數(shù)經(jīng)過FIR濾波器的輸出頻譜。

圖2 隨機數(shù)濾波后頻譜

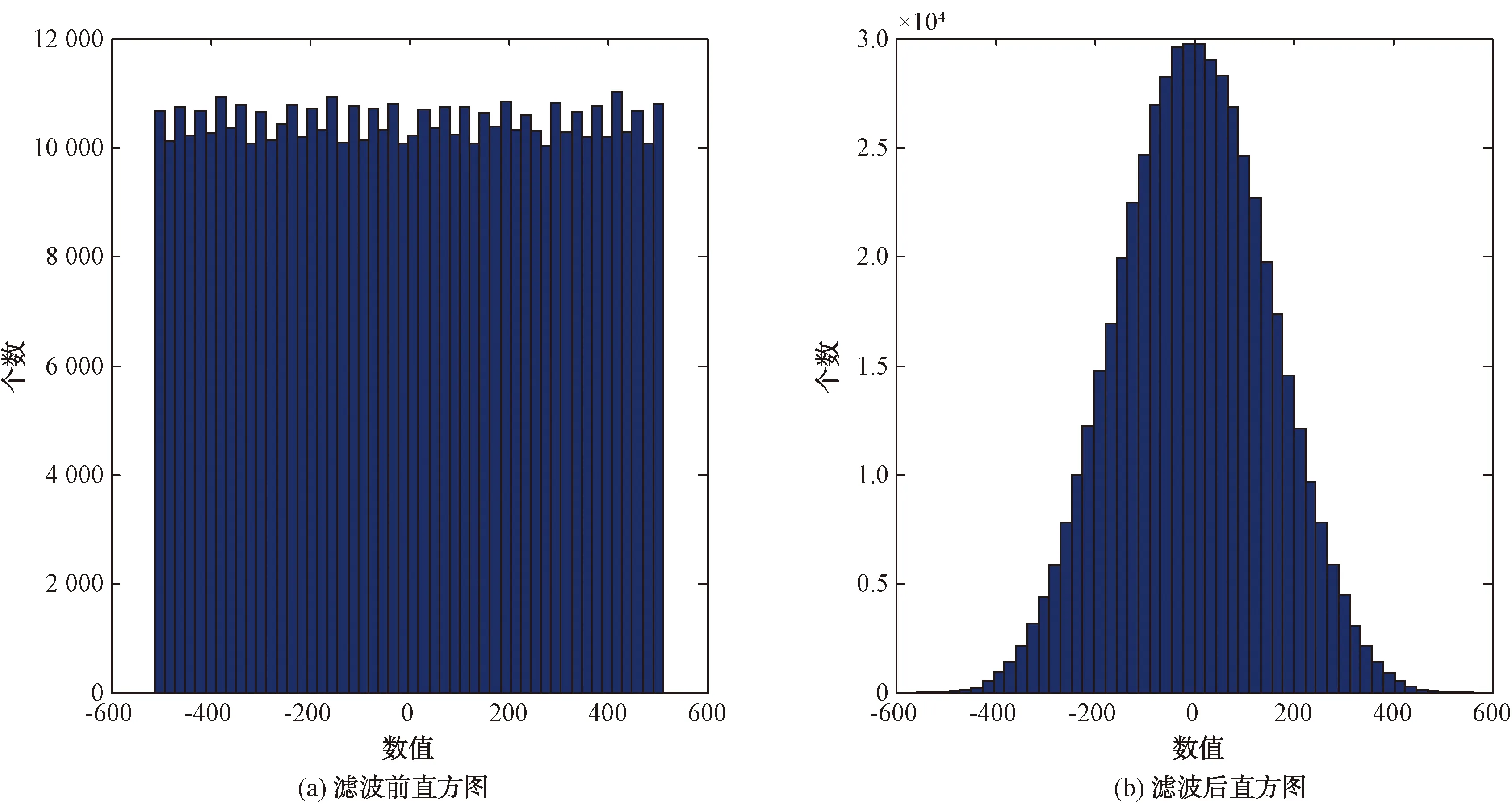

圖3顯示了隨機數(shù)濾波前后的直方圖,濾波前的隨機數(shù)近似均勻分布,經(jīng)過濾波器后隨機數(shù)近似正態(tài)分布,即輸出的信號是高斯白噪聲。

圖3 隨機數(shù)濾波前后直方圖

2 軟件設(shè)計

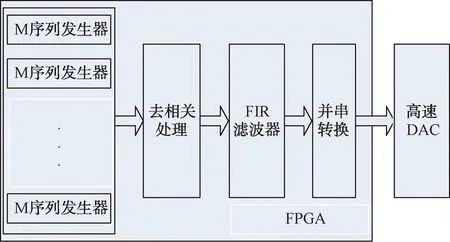

本設(shè)計選用的FPGA是Altera公司StratixIII系列的EP3SL340H1152I3。該芯片是一款高性能FPGA,具有豐富的邏輯資源,共有576個高速數(shù)字處理器(DSP)模塊,擁有8個鎖相環(huán)(PLL),并且內(nèi)嵌了18 Mbits的隨機存取器(RAM)資源。高速DAC是E2V公司的EV10DS130AVZPY,最高數(shù)據(jù)轉(zhuǎn)換速率可達3 Gsps,本設(shè)計中采用的轉(zhuǎn)換率為2 Gsps。軟件開發(fā)工具使用QuartusII和Modelsim進行設(shè)計和仿真驗證。圖4是FPGA設(shè)計原理框圖。

圖4 FPGA設(shè)計原理框圖

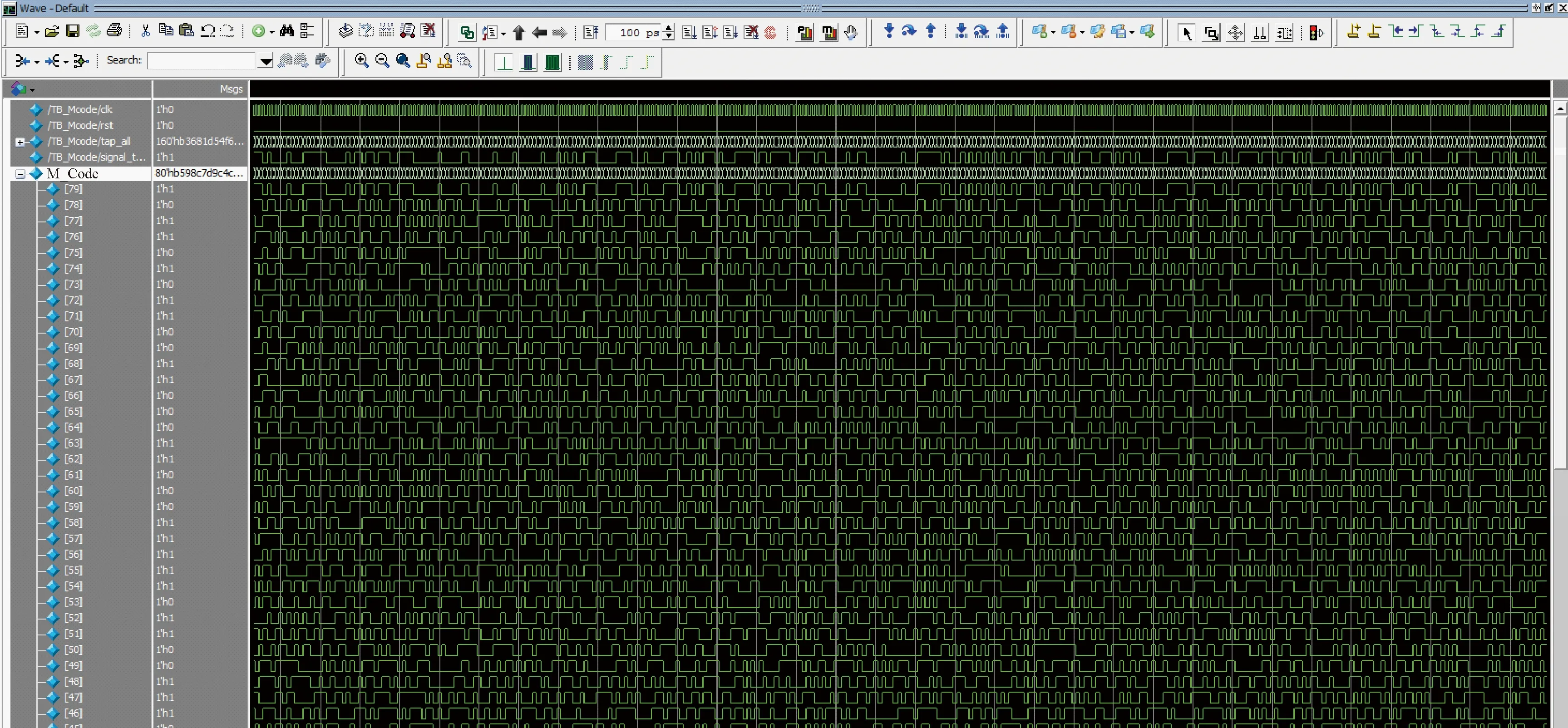

首先進行M序列發(fā)生器和去相關(guān)模塊的設(shè)計。利用Modelsim進行仿真驗證,將仿真數(shù)據(jù)導(dǎo)入Matlab進行頻譜和直方圖分析,分析結(jié)果與圖1及圖3完全一致。然后進行FIR濾波器設(shè)計,將濾波器系數(shù)定義為輸入變量,通過改變?yōu)V波器系數(shù)實現(xiàn)輸出噪聲中心頻率和帶寬的配置。圖5中的M_Code[79..0]是經(jīng)過濾波器后的8路10 bits并行噪聲數(shù)據(jù),將數(shù)據(jù)進行并串轉(zhuǎn)換后送給高速DAC。

圖5 濾波輸出仿真圖

3 實際測試

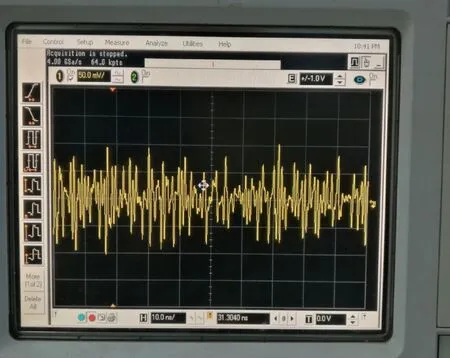

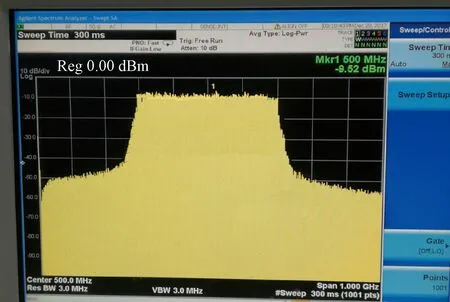

為了驗證設(shè)計的正確性,將設(shè)計好的軟件下載到硬件電路中進行測試。試驗中系統(tǒng)時鐘250 MHz,DAC時鐘2 GHz,F(xiàn)IR濾波器設(shè)定中心頻率500 MHz,帶寬400 MHz。利用SignalTap采集FIR濾波器后的數(shù)據(jù),并導(dǎo)入Matlab進行頻譜和直方圖分析。分析結(jié)果同圖2、圖3完全一致。將DAC輸出信號分別接入示波器和頻譜儀,觀察信號的時域、頻域波形。圖6、圖7分別是示波器和頻譜儀的顯示波形,從圖7可以看出,信號3 dB帶寬為407 MHz,帶內(nèi)平坦度為±1 dB。實測結(jié)果與理論分析一致,驗證了該方案的準確性。

圖6 輸出時域波形

圖7 輸出頻域波形

4 結(jié)束語

本文提出了一種寬帶高斯白噪聲的產(chǎn)生方法,利用M序列發(fā)生器產(chǎn)生偽隨機序列,利用并行取樣的方法降低隨機數(shù)的相關(guān)性,再通過FIR數(shù)字濾波器實現(xiàn)噪聲帶寬及中心頻率的配置,并完成了均勻噪聲向高斯白噪聲的轉(zhuǎn)換。該設(shè)計方法在FPGA和高速DAC的平臺上進行了測試,產(chǎn)生了比較理想的寬帶高斯白噪聲,證明了設(shè)計方法的可行性和正確性。本設(shè)計可以應(yīng)用在有源干擾機的工程實踐中,具有很好的實用價值。

[1] 趙國慶.雷達對抗原理[M].西安:西安電子科技大學(xué)出版社,2003.

[2] 黃本雄,侯潔,胡海.高斯白噪聲發(fā)生器在FPGA中的實現(xiàn)[J].微計算機信息,2007,23(7-2):165-167.

[3] 蔣樂,馮文全.高性能可編程高斯白噪聲的設(shè)計與實現(xiàn)[J].電子技術(shù)應(yīng)用,2006(8):113-114.

[4] 管宇,徐雷,徐建中.用FPGA產(chǎn)生高斯白噪聲序列的一種快速方法[J].電子元器件應(yīng)用,2008,10(11):55-58.

[5] 楊小牛,樓才義,徐建良.軟件無線電技術(shù)與應(yīng)用[M].北京:北京理工大學(xué)出版社,2010.