多通道發射場測試系統設計

蘇淑靖 韓文革

摘 要: 針對目前發射場測試儀測試通道單一,設計并開發一種多通道發射場測試系統。系統采用模塊化思想,由變送模塊、采集模塊、主控模塊組成。變送模塊將傳感器的信號變送為4~20 mA的電流信號,由采集模塊采集,然后通過背板與主控模塊進行通信與數據傳輸。詳細介紹了采集模塊,以FPGA為核心,采用VHDL編寫邏輯控制程序對數據采集、讀取過程進行控制,信號調理電路設計隔離放大電路與濾波電路。實驗結果表明,數據采集正常,各通道數據在測試范圍誤差內,滿足系統設計要求,目前已應用于發射環境測試系統中。

關鍵詞: 測試; 多通道; 數據采集; FPGA; 隔離放大; 濾波

中圖分類號: TN919?34 文獻標識碼: A 文章編號: 1004?373X(2018)19?0100?04

Abstract: Since the test channel of launching site tester is single, a multi?channel test system for launching site was designed and developed. The system adopting the modular concept is composed of transmission module, acquisition module and main control module. The different signals acquired by the sensor are transferred into 4-20 mA current signal through the transmission module, acquired by acquisition module, and communicated and transmitted through the backboard and main control module. The acquisition module is introduced in detail, and takes FPGA as its core. The VHDL is adopted to compile the logic control program to control the data acquisition and reading process. The isolation amplifying circuit and filtering circuit are designed for the signal conditioning circuit. The experimental results show that the data acquisition of the system is normal, and the data of each channel conforms to the error range of the test, which satisfies the system design requirements and is applied in the launching site test system.

Keywords: test; multi?channel; data acquisition; FPGA; isolation amplifying; filtering

0 引 言

隨著當代技術的發展,火箭發射已成為我國國防、經濟的重要組成部分,火箭發射安全的重要性不言而喻。火箭發射環境測試系統對火箭發射過程中發射環境效應引起塔架健康狀況變換及周圍環境參數進行測試,測試參數包括溫度、沖擊、振動和噪聲,為火箭研制總體單位、地面發射設備研制單位及航天器發射場提供發射近場的發射效應參數,為分析發射環境效應對發射環境中所處不同位置的設備產生的危害程度提供依據, 優化和防護火箭本體設計、地面發射設備及發射場發射設施,提高彈、箭發射試驗的可靠性[1]。

但目前國內很多測試系統僅能測試單一參數,不能同時實現溫度、沖擊、振動、噪聲多個參數的測試,而且還存在采集傳輸速率低等問題,針對這些問題設計研發多通道的火箭發射環境測試系統。

1 總體方案設計

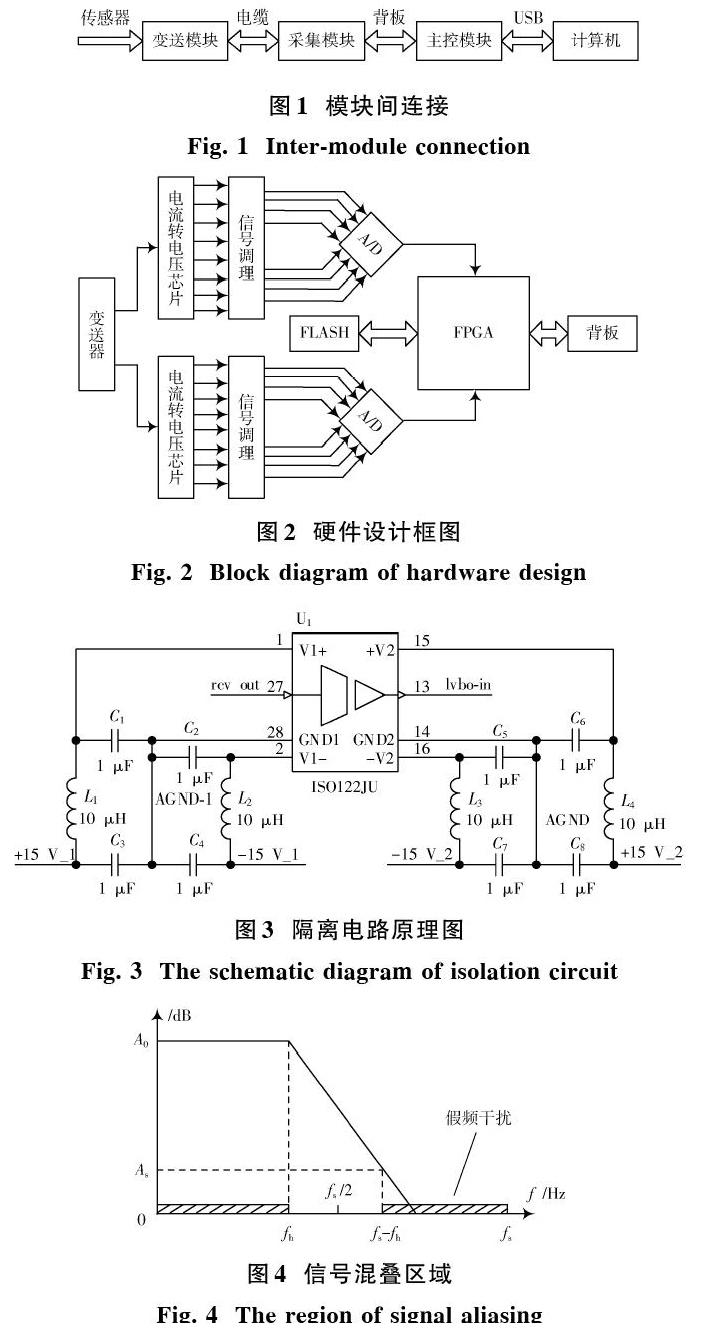

發射場測試系統由3個模塊組成,分別是變送模塊、采集模塊與主控模塊。變送模塊負責將不同傳感器的信號變送為4~20 mA電流信號;采集模塊采集變送器的電流信號,將其轉換成電壓信號并經過隔離濾波等信號處理,然后通過A/D轉換成數字信號并存儲到FLASH中;主控模塊通過背板與采集模塊相連并通過USB接口與上位機進行通信與數據傳輸[2]。

模塊間連接如圖1所示。

2 硬件設計方案

2.1 硬件設計電路框圖

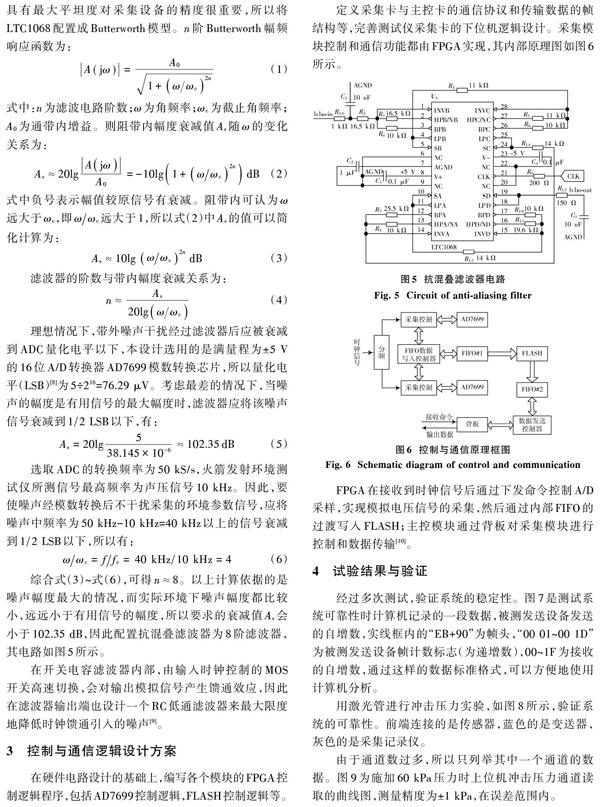

數據輸入共64個通道,共4塊電路板,4塊采集板通過背板與主控板連接。每塊電路板16個通道,其中壓力測試6個通道,溫度測試6個通道,沖擊測試2個通道,噪聲測試2個通道。本文主要對采集模塊進行詳細描述,其硬件設計方案如圖2所示。

本文設計采用Xilinx XC6SLX100的FPGA芯片作為整個模塊的核心控制器,實現對整個模塊的控制與通信功能,該芯片能夠提供各種業界領先的連接特性,具有很高的性價比。其主要性能特點是內部具有976 Kb的分布式RAM和4 824 Kb的塊RAM,最大用戶I/O引腳為480個,同時支持高速的LVDS接口[3]。

采集模塊將變送器輸出的電流信號經電流轉電壓芯片RCV420將輸入的4~20 mA電流信號轉換成電壓信號,然后通過信號隔離電路模塊ISO122將干擾信號隔離,再通過抗混疊濾波器將帶外信號濾除,濾除的信號在FPGA的控制下經模數轉換器AD7699進行轉換,轉換后的信號存儲到FLASH存儲器中,最后通過計算機控制主控模塊讀取FLASH中的數據[4]。

2.2 信號調理電路的設計

調理電路的設計是十分重要的,能夠提高系統的采樣精度。信號調理電路包括信號隔離電路以及抗混疊濾波器電路。

2.2.1 信號隔離電路

為了抑制變送器和采集記錄器之間的相互干擾,設計如圖3所示的信號隔離電路,ISO122是采用滯回調制解調技術設計的隔離放大器,該電路將輸入信號調制為500 kHz的方波信號送至輸出端,輸出端再將該調制信號進行解調復現輸入信號。為了抑制電源噪聲,在兩隔離電源與各自的地之間接1 μF鉭電容去耦。為使內部500 kHz的震蕩頻率與變換隔離電源的DC/DC變換器的差拍頻率噪聲最小,隔離電源通過Π型濾波后為ISO122供電。為了抑制由內部調制/解調信號在輸出端形成500 kHz,200 mV的紋波,隔離電路輸出端也進行濾波[5]。

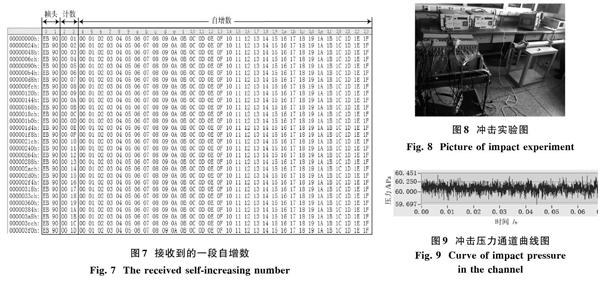

2.2.2 抗混疊濾波器電路

在模數轉換時,被測信號中摻雜的高頻噪聲會等幅度地折疊到低頻有用信號中,這部分噪聲也會被量化。如圖4所示,以頻率[fs]對最大頻率為[fh]的有用信號進行采樣,如果[(fs-fh)~fs]頻段上存在干擾信號,采樣時會將這部分干擾信號以[fs2]為對稱軸等幅度疊加到0~[fh]的有用頻段上,因此要將頻率大于[fs-fh]的噪聲信號濾波,使其至少衰減到ADC的量化電平以下[6]。

火箭發射環境測試儀所測試的溫度、振動、沖擊壓力、聲壓4種信號的采樣率分別為1 kS/s,20 kS/s,10 kS/s和20 kS/s。不同的采樣率,如果采用固定截止頻率的濾波器電路,必須設計不同的外圍電路,增加元器件的種類,降低可靠性。本設計使用Linear Technology公司生產的開關電容型濾波器LTC1068,其典型截止頻率誤差僅為±0.3%,截止頻率與輸入時鐘頻率比為1[∶]100,內部集成4個獨立二階節,可以配置成具有各種響應(包括Butterworth,Bessel,Chebychev、橢圓、最小[Q]值橢圓和定制響應)的低通、高通、帶通、帶阻濾波器,既可以獨立工作又可以兩兩級聯組成一個4階濾波器,還可以全部級聯組成8階濾波器[7]。濾波器通帶內的幅頻響應曲線具有最大平坦度對采集設備的精度很重要,所以將LTC1068配置成Butterworth模型。[n]階Butterworth幅頻響應函數為:

綜合式(3)~式(6),可得[n≈8]。以上計算依據的是噪聲幅度最大的情況,而實際環境下噪聲幅度都比較小,遠遠小于有用信號的幅度,所以要求的衰減值[As]會小于102.35 dB,因此配置抗混疊濾波器為8階濾波器,其電路如圖5所示。

在開關電容濾波器內部,由輸入時鐘控制的MOS開關高速切換,會對輸出模擬信號產生饋通效應,因此在濾波器輸出端也設計一個RC低通濾波器來最大限度地降低時鐘饋通引入的噪聲[9]。

3 控制與通信邏輯設計方案

在硬件電路設計的基礎上,編寫各個模塊的FPGA控制邏輯程序,包括AD7699控制邏輯,FLASH控制邏輯等。

定義采集卡與主控卡的通信協議和傳輸數據的幀結構等,完善測試儀采集卡的下位機邏輯設計。采集模塊控制和通信功能都由FPGA實現,其內部原理圖如圖6所示。

FPGA在接收到時鐘信號后通過下發命令控制A/D采樣,實現模擬電壓信號的采集,然后通過內部FIFO的過渡寫入FLASH;主控模塊通過背板對采集模塊進行控制和數據傳輸[10]。

4 試驗結果與驗證

經過多次測試,驗證系統的穩定性。圖7是測試系統可靠性時計算機記錄的一段數據,被測發送設備發送的自增數,實線框內的“EB+90”為幀頭,“00 01~00 1D”為被測發送設備幀計數標志(為遞增數),00~1F為接收的自增數,通過這樣的數據標準格式,可以方便地使用計算機分析。

用激光管進行沖擊壓力實驗,如圖8所示,驗證系統的可靠性。前端連接的是傳感器,藍色的是變送器,灰色的是采集記錄儀。

由于通道數過多,所以只列舉其中一個通道的數據。圖9為施加60 kPa壓力時上位機沖擊壓力通道讀取的曲線圖,測量精度為±1 kPa,在誤差范圍內。

5 結 語

本文基于MLVDS的64通道數據采集模塊作為火箭發射環境測試系統的組成之一,采用模塊化設計思想,利用FPGA實現數據采集傳輸的控制,并利用MLVDS接口完成主控模塊與4個采集模塊之間的控制通信與數據傳輸。添加CRC校驗碼提高數據傳輸的可靠性,傳輸速率達35 MB/s。本模塊已應用于火箭發射環境測試系統中,數據采集正常,誤碼率低,運行效果良好,滿足設計要求。

參考文獻

[1] 郭錚,劉文怡,馮妮.基于FPGA多通道高速數據采集存儲器設計[J].電視技術,2012,36(17):55?57.

GUO Zheng, LIU Wenyi, FENG Ni. Design of multi?channel high?speed data acquisition and storage memory based on FPGA [J]. Video engineering, 2012, 36(17): 55?57.

[2] 雷超群,蘇淑靖.一種多變量變送器的設計與實現[J].計算機測量與控制,2015,23(9):3248?3250.

LEI Chaoqun, SU Shujing. Design and implementation of a multi variable transmitter [J]. Computer measurement & control, 2015, 23(9): 3248?3250.

[3] 楊毅.MLVDS標準介紹及德州儀器SN65MLVD200系列[J].今日電子,2003(9):53?55.

YANG Yi. Introduction of MLVDS standard and SN65MLVD200 series from TI [J]. Electronic products, 2003(9): 53?55.

[4] 胡漢輝,譚青.自適應抗混疊濾波器在數據采集中的應用[J].電測與儀表,2009,46(9):72?75.

HU Hanhui, TAN Qing. Design of anti?aliasing filter for data acquisition [J]. Electrical measurement & instrumentation, 2009, 46(9): 72?75.

[5] 阿永嘎.多位串行M?LVDS高速網絡式儀器總線的研究[D].杭州:浙江大學,2010.

A Yongga. The study of M?LVDS based multi?bits serial networked instrument bus [D]. Hangzhou: Zhejiang University, 2010.

[6] 曹成成.基于TIA/EIA?899的MLVDS驅動器關鍵技術的研究[D].長沙:湖南大學,2014.

CAO Chengcheng. Research on key points of MLVDS driver based on TIA/EIA?899 [D]. Changsha: Hunan University, 2014.

[7] 李輝景,王淑琴,任勇峰,等.基于CRC校驗的高速長線LVDS傳輸設計[J].電子器件,2015,38(6):1346?1351.

LI Huijing, WANG Shuqin, REN Yongfeng, et al. Design of high?speed and long?term LVDS data transmission system based on CRC check [J]. Chinese journal of electron devices, 2015, 38(6): 1346?1351.

[8] FU Yongjie, ZHANG Xunwen. Software design of multi?parameters data acquisition system based on LabWindows/CVI [C]// 2009 ISTM. Beijing, China: ISTM, 2009: 1?5.

[9] SUNG C H, KIM J H. Biased scan of plasma display panel for data voltage reduction [J]. Displays, 2012, 33(1): 21?27.

[10] ROBERT A. Pease: troubleshooting analog circuits [M]. US: Elsevier, 1991: 95?105.