FPGA實現角膜變形信號峰值時刻檢測的研究

楊成禹,王琦,畢偉權,肖作江

(1.長春理工大學 光電工程學院,長春 130022;2.吉林東光精密機械廠,長春 130013)

青光眼是我國當前重要致盲眼病之一,眼壓升高是其主要致病機理。眼科界倡導以采用空氣脈沖檢測法的非接觸式眼壓檢測取代接觸式眼壓檢測[1],來避免產生眼部感染、減少患者痛苦[2]。在非接觸式眼壓檢測系統中,角膜變形信號峰值時刻檢測在整個系統中起著至關重要的作用,決定系統最終的測量精度以及時間分辨率[3]。目前普遍采用由比較器、DAC以及ARM組成的角膜峰值時刻檢測系統,由DAC與輸入信號經比較器進行比較,主控芯片負責DAC和比較器的電壓輸出控制以及峰值時刻判定,但由于程序順序運行且器件自身具有一定延遲性產生延時,導致獲得的峰值時刻不夠精準。只有獲得兩次精準的峰值時刻,才能準確得到對應時刻下來自壓力傳感器的眼壓壓力信號,最終完成眼壓檢測。可見設計一套高精度的角膜變形信號尋峰系統對非接觸式眼壓檢測技術具有重要意義。FPGA具有并行處理、邏輯資源豐富等優勢[4],可減少延時誤差且不需比較器及DAC電路部分便可完成峰值檢測功能,可減少硬件電路的設計。因此,提出一種基于FPGA的非接觸式角膜變形信號峰值時刻檢測系統,選用Altera公司的Cyclone IV系列的EP4CE15F17C8N作為主控制器,通過FPGA狀態機來實現閾值比較尋峰算法,達到了檢測角膜變形信號峰值以及確定峰值精準發生時刻的效果。

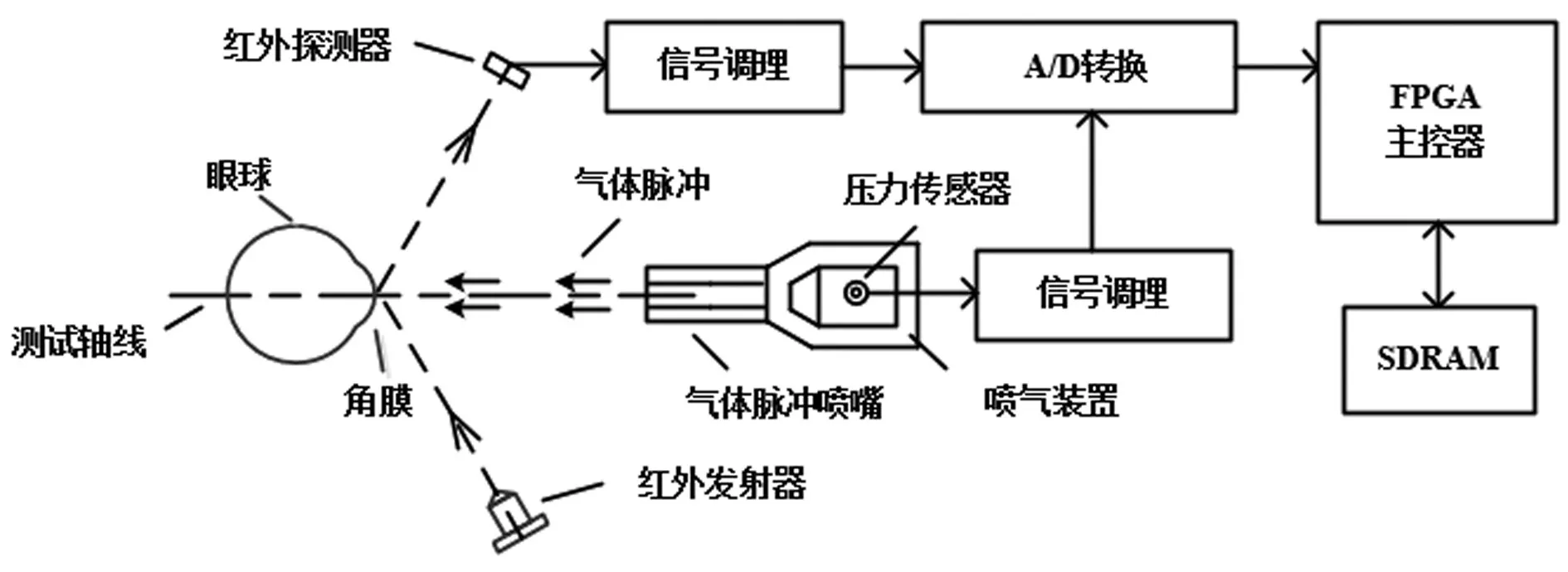

1 檢測系統總體結構

檢測系統主要由FPGA主控器、紅外發射器、紅外探測器、壓力傳感器、A/D轉換器以及SDRAM存儲器構成。檢測系統整體結構如圖1所示,紅外探測器放在紅外發射器相對測試軸線的對稱位置上,由氣體脈沖噴嘴噴出的氣體脈沖作用于角膜表面使角膜產生形變,發射器發出的光經不同形態下的角膜反射后,由探測器接收反射光信號并進行光電轉換,得到角膜變形信號。

圖1 檢測系統整體結構

當角膜被壓至平時,探測器輸出角膜變形峰值信號,此時壓力傳感器測得氣體脈沖將眼膜壓平的眼壓壓力,即為眼內壓值。對角膜變形信號與壓力傳感器輸出的眼壓壓力信號進行信號調理后,經由A/D轉換器,將兩路轉換后的信號送入FPGA主控器,由FPGA進行角膜變形信號的尋峰處理以及精準峰值時刻的確定,并由SDRAM完成相關數據存儲。

對基于FPGA非接觸式角膜變形信號峰值時刻系統進行功能模塊化的系統設計,圖2為峰值時刻檢測原理,如圖2所示,系統主要分為角膜變形信號檢測模塊、A/D轉換模塊、FPGA主控模塊以及SDRAM存儲模塊。

圖2 峰值時刻檢測原理

其中,FPGA主控模塊采用了自頂向下的方法,依據功能劃分為時鐘分頻模塊、FIFO緩存模塊、峰值檢測模塊以及ADC時序控制模塊幾部分。利用Verilog HDL語言對相關模塊進行設計,采用Quartus II開發環境對各個模塊集成的頂層設計文件進行綜合,實現對信號的采集和處理等操作。

2 峰值時刻檢測系統模塊化設計

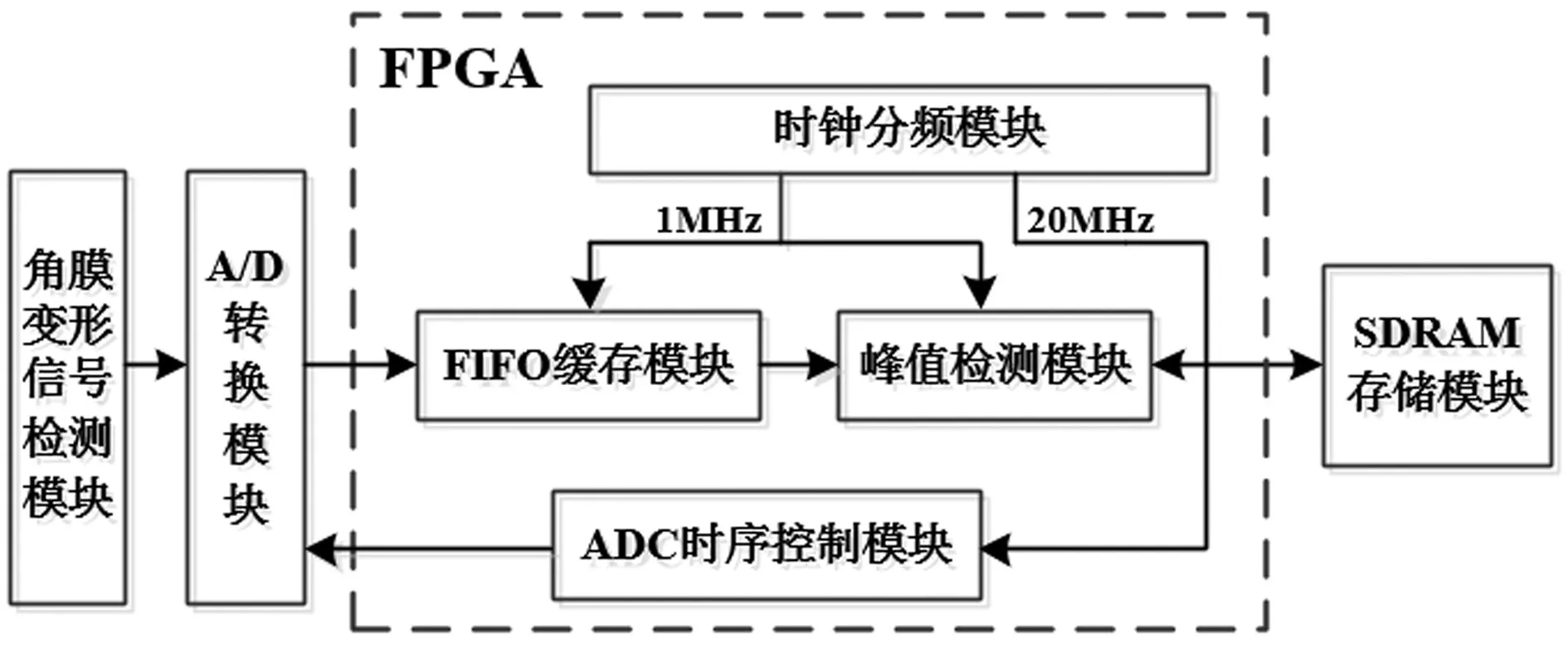

2.1 角膜變形信號檢測模塊

角膜變形信號檢測模塊由紅外發射器、紅外探測器和信號調理電路幾部分組成。由于1550nm波長位于人眼安全激光波段且處于大氣傳輸窗口是作為檢測眼部信息的理想波長,故前端紅外發射器和紅外探測器分別采用SEALAND公司發射波長為1550nm的XL503320IRC以及接收波長范圍在800-1750nm的XL2835PD13。前置運放采用ADI公司20MHZ軌到軌高輸出電流放大器AD8616。角膜變形信號檢測電路如圖3所示,紅外探測器與運放的連接方法屬于電流放大型,兩個輸入端同極性相連,電阻R1作為反饋電阻。XL2835PD13的光電流Isc為22μA,R1=100kΩ,輸出電壓可滿足A/D轉換器模擬量輸入范圍。紅外探測器工作在兩端無偏壓的光電池狀態,此狀態下紅外探測器沒有反向偏置電壓,故暗電流非常小減小了輸出噪聲[5]。

圖3 角膜變形信號檢測電路

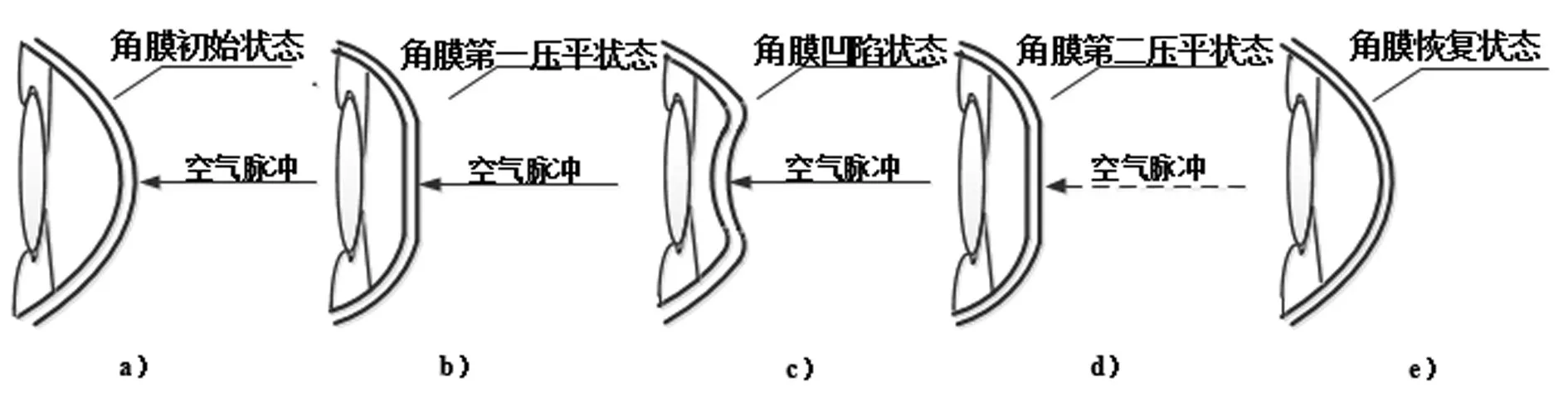

當氣體脈沖噴嘴向角膜噴射氣體時,紅外探測器接收到的光信號強弱隨角膜狀態的改變而發生變化,圖4為角膜變形過程。

圖4 角膜變形過程

其中圖4a)為初始狀態角膜,此時來自發射器的基本準直光束在被彎曲的角膜表面反射后發散,使紅外探測器接收到的信號相對較弱。隨著空氣脈沖的推進,角膜產生圖4b)的第一壓平狀態,光束由曲率半徑無限大的角膜表面反射后,使得更多的光到達紅外探測器形成峰值。空氣脈沖因慣性繼續推進,角膜會向內凹陷形成圖4c)狀態,紅外探測器接收到的光信號減弱。隨著空氣脈沖的消退,角膜恢復至圖4d)的第二壓平狀態產生第二次峰值信號,最終恢復圖4e)的角膜自然狀態。故只有當角膜處于兩次壓平狀態時,探測器輸出電壓值最大的峰值信號。

2.2 A/D轉換模塊

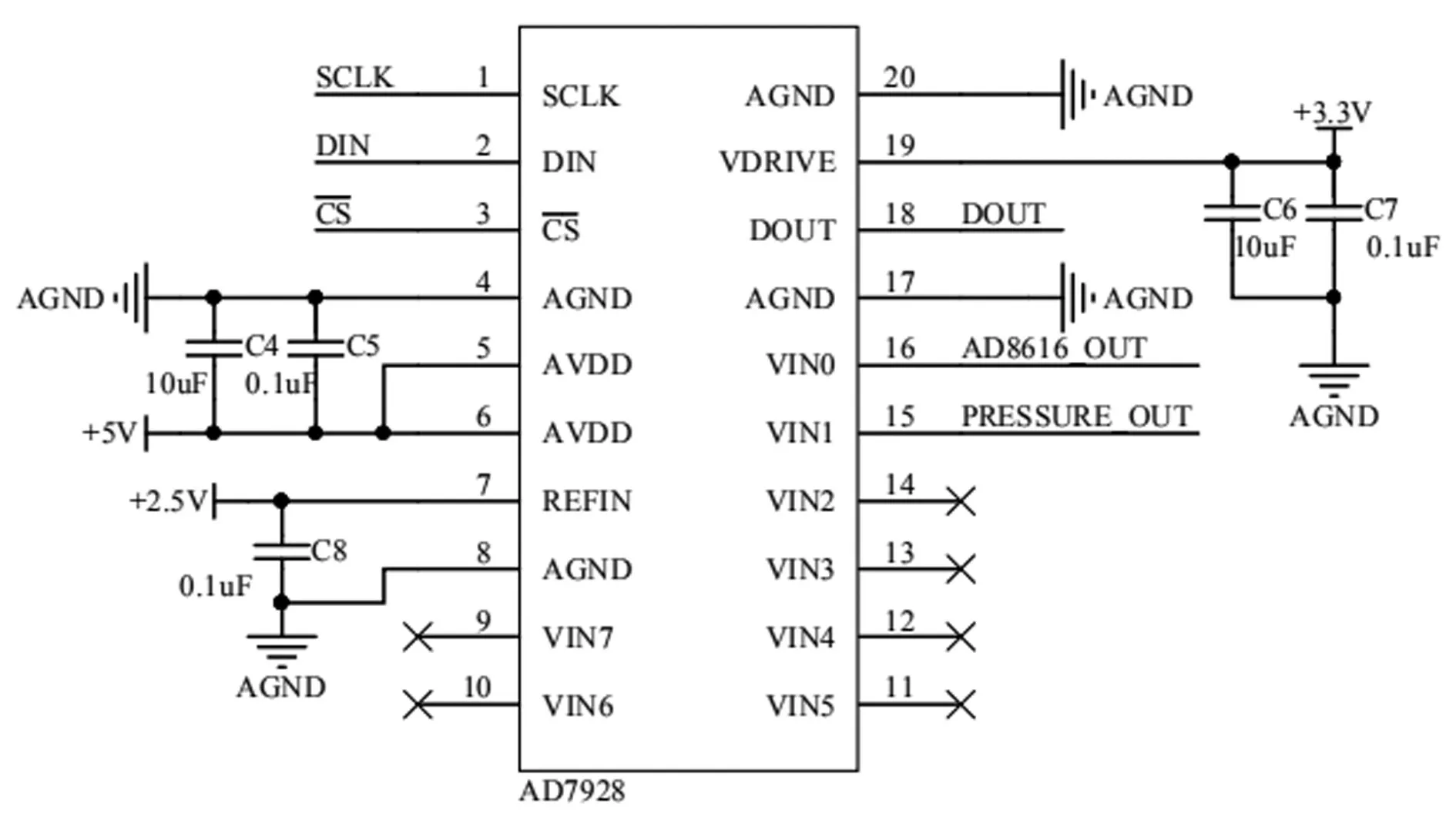

A/D轉換芯片采用ADI公司12位逐次逼近型A/D轉換器AD7928,最高采樣速率為1Msps。AD7928轉換模塊如圖5所示,先選通VIN0通道對角膜變形信號進行采集,再選通VIN1通道采集來自壓力傳感器的眼壓壓力信號。轉換結果通過DOUT串行輸出,采用標準SPI協議。系統采用12位ADC可達到1mv的測量精度,實現高精度角膜變形信號的轉換。

圖5 AD7928轉換模塊

2.3 FPGA主控模塊

2.3.1 時鐘分頻模塊

為確保ADC所采集到的數據能夠被FPGA實時接收并處理,FPGA的各功能模塊時鐘頻率和AD7928 1MHz的采樣率應保持一致[6]。本模塊設計了一個由時鐘脈沖上升沿觸發的50分頻計數器,通過控制計數器循環計數來實現分頻,為FPGA內部模塊提供了1MHz的工作時鐘;其次,由于AD7928需要20MHz的輸入時鐘源SCLK,通過調用FPGA內部IP核PLL對50MHZ時鐘進行2倍頻,再經5分頻處理得到20MHz時鐘為ADC提供訪問器件數據所需的串行時鐘以及轉換過程的時鐘源。

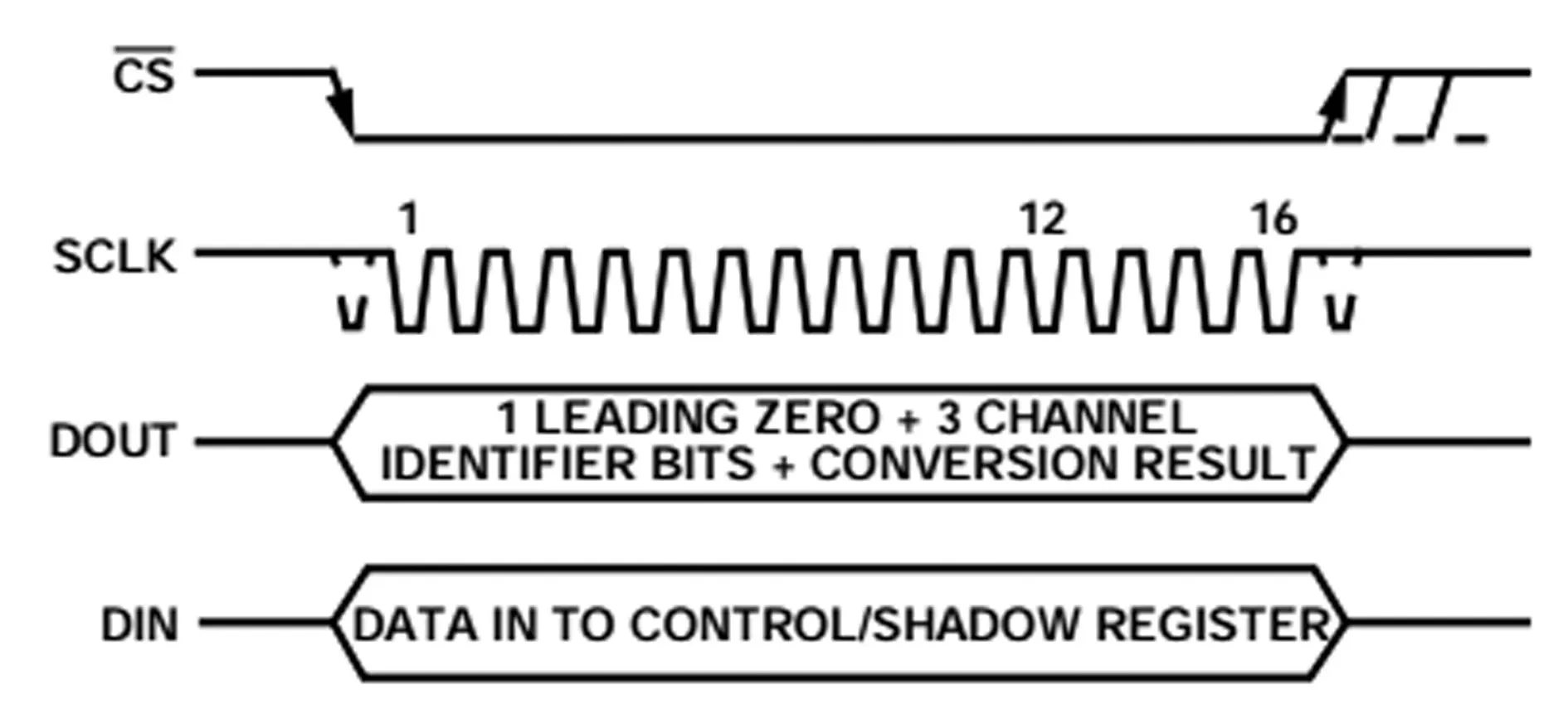

2.3.2 ADC時序控制模塊

由FPGA對AD7928進行時序控制,協調FPGA控制A/D采樣時序[7],AD7928工作時序如圖6所示,A/D在通電后,首先FPGA需對AD7928的控制寄存器進行操作,完成輸入通道選擇、輸入電壓范圍設置以及輸出數據編碼格式設置等,由時鐘分頻模塊提供20MHz輸入時鐘源SCLK,數據在SCLK的下降沿從DIN引腳載入ADC,FPGA在轉換和數據采集過程中對和串行時鐘信號進行控制,輸入信號在的下降沿進行采樣,而轉換同時在此處啟動,無流水線延遲,數據轉換一次需要16個周期,轉換后的數據從DOUT引腳送入FIFO緩存模塊。

圖6 AD7928工作時序

2.3.3 FIFO緩存模塊

AD7928每1μs輸出一個角膜變形信號,空氣脈沖作用下角膜變形信號從產生到結束大概需要25ms,ADC輸出約25000個數據量。為防止數據量大引發數據丟失、提高系統工作效率設計了本模塊。通過配置FPGA內部的IP核FIFO,設置位數為12,深度為32768的同步FIFO,可滿足25ms內連續的角膜變形信號數據流進行緩存,實現對數據先采集后處理的工作模式。圖7為FIFO緩存結構,clock是FIFO的寫/讀時鐘,與AD7928采樣時鐘一致,即為1MHz的工作時鐘,由時鐘分頻模塊提供該時鐘。data為FIFO輸入數據,即AD7928的輸出數據。q為FIFO的輸出數據,wrreq和rdreq分別為寫使能和讀使能,通過full/empty(滿/空標志)控制數據的寫入/讀出。將寫滿的25ms數據送至峰值檢測模塊,由SDRAM存儲模塊完成FIFO輸出數據的存儲。

圖7 FIFO緩存結構

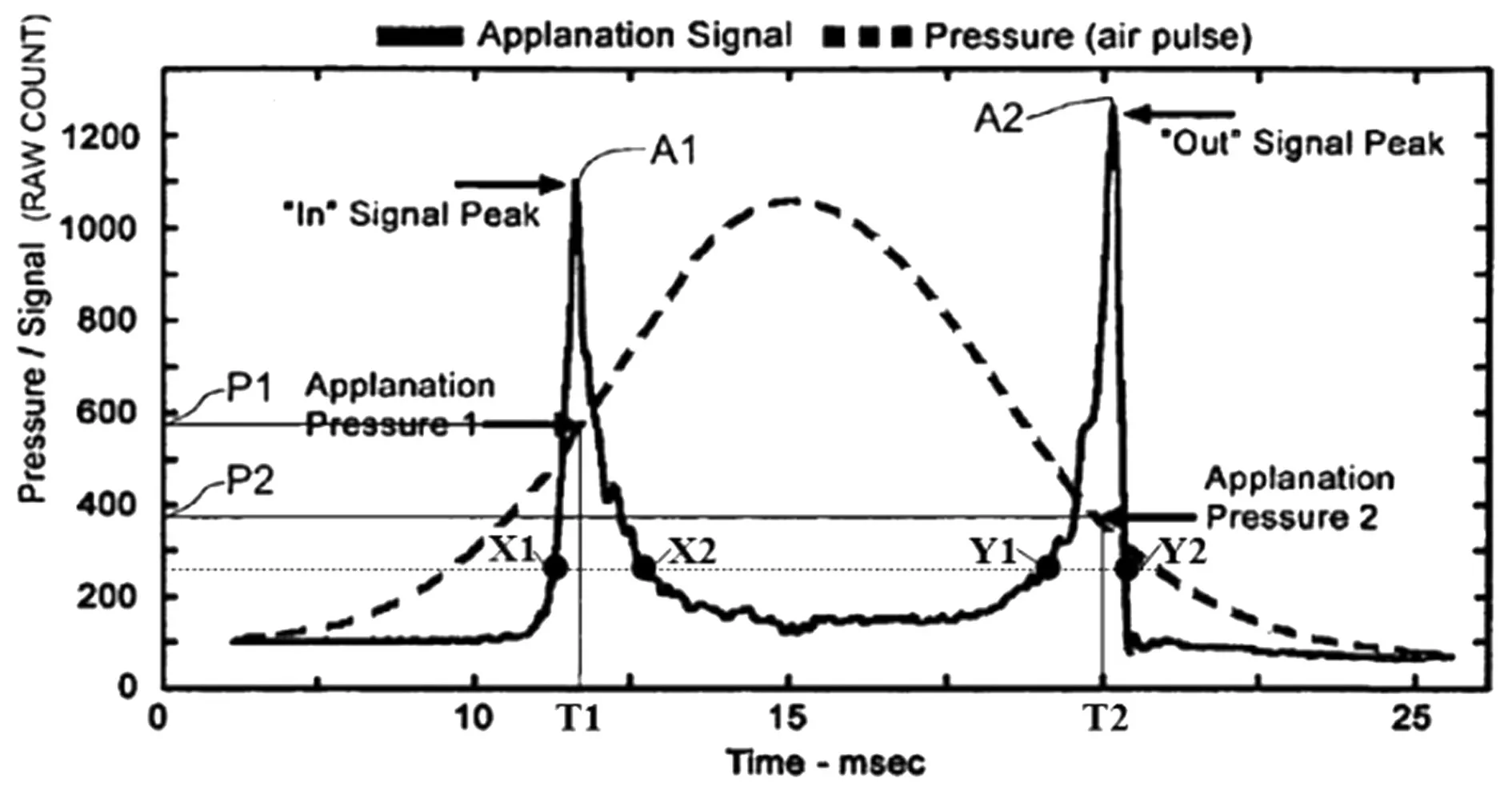

2.3.4 峰值檢測模塊

考慮到角膜變形信號在采集過程中會夾雜一定的信號噪聲,可能產生“毛刺”或“假峰”影響尋峰精度[8],對FIFO緩存送入的數據通過數字濾波進行預處理,采用異常值判斷濾波法,根據相鄰兩點數據無跳變的理論,比較相鄰兩次采樣值如變化超過閾值,則說明為異常值,通過去除最近一個數據消除尖峰噪聲對峰值檢測的影響。圖8為角膜變形信號峰值,將角膜變形信號和眼壓壓力信號擬合在同一坐標軸下,A1、A2為兩次角膜變形信號的峰值,P1、P2為對應于兩次峰值時刻TI、T2的眼壓壓力信號。如果直接進行尋峰檢測數據量較大,而且大部分數據均為冗余數據[9],為減少FPGA處理數據量,提高處理速度,采用閾值比較尋峰算法排除掉離峰值電壓較遠的低電壓浮動。

圖8 角膜變形信號峰值

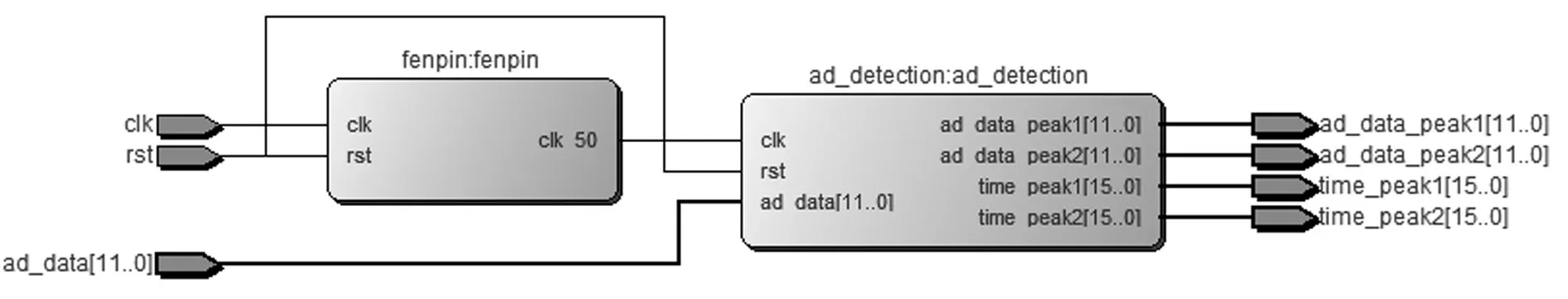

通過Verilog HDL編寫狀態機來實現峰值檢測,圖9為RTL峰值檢測。在FPGA內部設置兩個寄存器,分別存儲兩次角膜峰值信號。FIFO每1μs送入一個ad_adta,通過計數器對輸入信號進行計數。首先對輸入信號進行閾值比較,若大于所定閾值X1點的值時(如圖7所示),則初始化第一峰值寄存器,進入峰值比較狀態并將輸入值存入該寄存器。若下個進入的值大于該寄存器值,則將該值更新為寄存器值,否則該寄存器值不變。

圖9 RTL峰值檢測

依次判斷采集的信號值,直到輸入信號值小于寄存器值時,判斷當前寄存器值是否為有效峰值。如果此后到X2點之前的信號均呈下降狀態,則該寄存器值為有效峰值;反之,由于有效峰值幅度較大,通過去掉幅值達不到要求的無效峰值得到ad_data_peak1,并通過計數器提取出峰值時刻time_peak1[10]。狀態轉移到對第二次峰值的檢測,檢測機制與第一峰值檢測相同,將檢測得到ad_data_peak2存入第二峰值寄存器,并得到峰值時刻time_peak2。將得到的角膜峰值時刻值送入SDRAM存儲模塊內進行存儲。

對所獲得的角膜峰值時刻進行誤差分析,不僅要考慮角膜變形信號測量過程中的高斯噪聲誤差[11],還要考慮A/D量化誤差所帶來的影響。設角膜變形真實信號s1(t)疊加高斯噪聲z1(t)后為:

A/D量化誤差與高斯噪聲不相關,式(1)經A/D量化誤差q1(n)疊加后為:

設AD7928位數為b位,量化寬度即為B=2-b,采用舍入處理,舍入量化噪聲q(n)的均值與方差分別為:

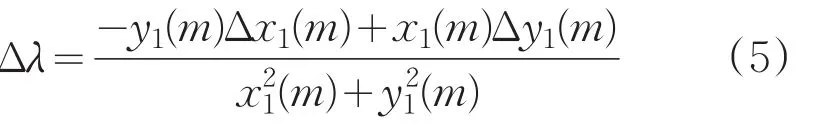

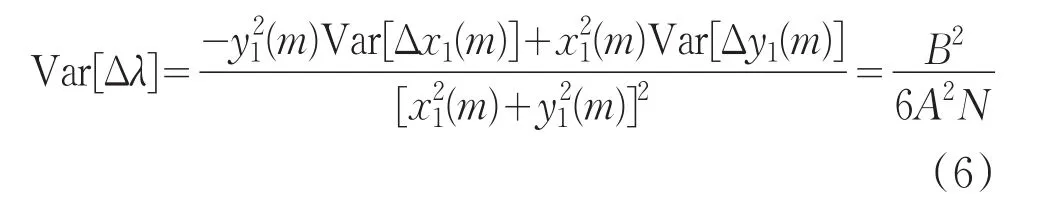

用Δλ表示角膜變形接收信號r1(n)與角膜變形真實信號s1(n)在量化噪聲引起的相位偏移。對s1(t)進行傅里葉變換得S(k)=x(k)+jy(k)。記在最大譜線對應的k為m,Δλ表達式為:

將信號的幅度記為A,由式(5)可以得到相位差的方差為:

記采樣次數為N,高斯白噪聲背景下角膜變形信號FFT相位差法估計誤差的方差的下限為:

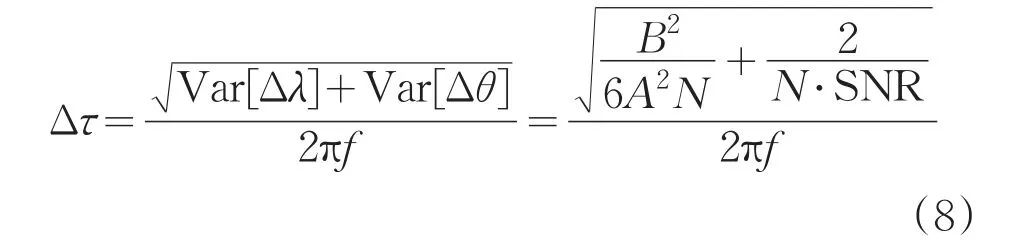

峰值時間誤差Δτ可表示為:

角膜變形信號f為1MHz,AD7928的位數b=12,采樣次數N=3,SNR=15dB時,得到角膜變形信號峰值時刻誤差結果為0.157μs,可知角膜變形信號峰值時刻檢測誤差小于0.2μs。

2.4 SDRAM存儲模塊

采用Micron公司的32Bit MT48LC4M32B2P-6作為SDRAM存儲芯片,SDRAM具有體積小、存儲空間大等優點。通過FPGA對SDRAM狀態控制器進行配置,SDRAM控制器針對SDRAM的指令操作特點,為SDRAM提供同步命令接口和時序邏輯控制,采用讀、寫FIFO和讀寫邏輯控制模塊,優化接口封裝[12]。SDRAM的每次寫操作可將數據存儲在指定位置,讀操作根據需求讀出指定位置的數據,完成角膜變形信號以及角膜峰值時刻的寫入/讀出以及存儲。

3 系統仿真分析

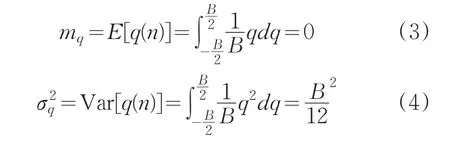

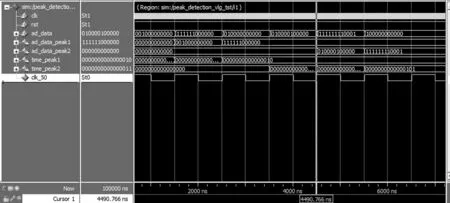

為了驗證本系統能夠完成對兩次峰值信號的提取以及確定兩次峰值時刻,使用Modelsim進行了仿真,峰值檢測仿真結果如圖10所示。其中,clk為外部時鐘信號,rst為復位信號,clk_50為時鐘分頻模塊產生的1MHz時鐘,ad_adta為FIFO輸入信號,ad_data_peak1和ad_data_peak2為兩次峰值信號,time_peak1和time_peak2為兩次峰值信號對應的峰值時刻。可見系統完成了從ad_data輸入信號中提取出兩次峰值信號,ad_data_peak1和ad_data_peak2最終輸出為兩次峰值信號,并由time_peak1和time_peak2輸出了兩次峰值信號對應的時刻。

圖10 峰值檢測仿真結果

4 結束語

通過理論分析與仿真驗證,基于FPGA實現的角膜變形信號峰值時刻檢測系統完成了對兩次峰值時刻的檢測,對產生25ms左右的角膜變形信號可達到1μs的峰值檢測精度,且檢測誤差小于0.2μs,實現了對角膜變形信號峰值時刻精度較高的檢測。與傳統峰值時刻檢測電路相比,本系統通過FPGA作為主控芯片,不需采用比較器及DAC電路部分,便實現了數據采集與峰值檢測,減少了峰值檢測硬件電路的設計,在時間精度和采樣速率上均有提高,系統運行穩定可靠。