一種基于XVC協議的FPGA調試模塊設計

趙 赟

(中國船舶重工集團公司第七二三研究所,江蘇 揚州 225101)

0 引 言

隨著現代艦船電子設備的高度集成化,相關的分機板卡也越來越多。傳統的USB-JTAG調試方式通信有效距離短,在艦船現場調試FPGA時,由于內外部環境復雜,調試人員可能需要攀爬,或者擁擠在狹小空間內,同時多塊板卡對應單獨的調試電纜,調試不同板卡還需要不停插拔,給調試工作帶來極大不便。

針對此現象,本文基于Xilinx公司提出的XVC協議[1],設計了一種PTMP以太網調試模塊,它通過高速背板同各個板卡連接,以Xilinx公司推出的Zynq7000芯片為處理芯片,以Realtek公司的RTL8305NB-CG交換芯片作為網絡橋接,調試人員通過單個以太網口就能調試所有板卡,有效調試距離為100 m,還能支持多人在艦船不同地點同時調試,大大提升了艦船現場調試的便捷性和安全性。

1 模塊原理框圖設計

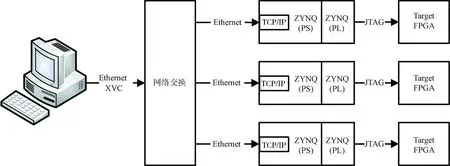

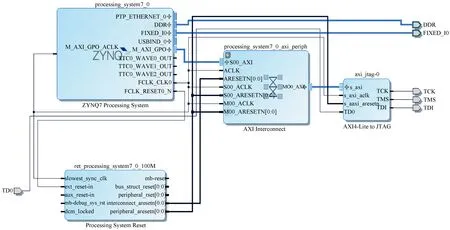

本模塊系統原理框圖如圖1所示,調試電腦(PC)通過以太網和網絡交換芯片相連,網絡交換芯片將數據包分發到各個Zynq7000芯片,Zynq7000的處理系統(PS)部分接收到調試PC的以太網數據包后通過AXI4-Lite總線發送到可編程邏輯(PL)部分,PL部分將其解析并轉化為聯合測試工作組(JTAG)時序信號發送至需要調試的FPGA芯片,完成調試工作。

圖1 系統原理框圖

1.1 處理芯片選用

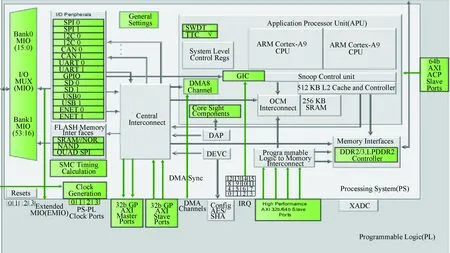

本文選用Zynq7000系列芯片作為模塊的處理芯片,該芯片是Xilinx公司推出的片上系統(Soc)解決方案,該方案將ARM公司Cortex-A9和FPGA集成在一個芯片上,通過內部總線連接,從而讓內部通信速度大大提升。它分為PS和PL兩大部分,PS部分包括2個ARM Cortex-A9處理器、AXI總線、內部存儲器、外部存儲器及外設接口(這些外設包括USB總線、以太網接口、SD卡接口、I2C總線接口、CAN總線接口、串口、GPIO等等);而PL部分則包括Xilinx 7系列的FPGA[2],Zynq7000的具體架構如圖2所示。

圖2 Zynq7000芯片內部結構框圖

1.2 AXI總線選用

Zynq7000作為Xilinx首款將ARM Cortex-A和7系列FPGA集成的Soc,其優勢在于ARM處理器和FPGA之間的高速通信,而AXI(Advanced Extensible Interface)總線就是連接這兩者的高速通道。AXI屬于ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture),是一種高性能的片內總線,AMBA-AXI協議主要用用于高帶寬、低延遲的系統設計,描述主從設備之間的數據傳輸方式[3]。主設備和從設備之間用握手信號建立連接。當從設備準備要接收數據時,會向主設備發送READY信號。而當主設備的數據準備好后,會發出和維持一個VALID信號,表示數據有效,VALID和READY信號都有效的時候,握手完成,主從設備之間開始傳輸數據。

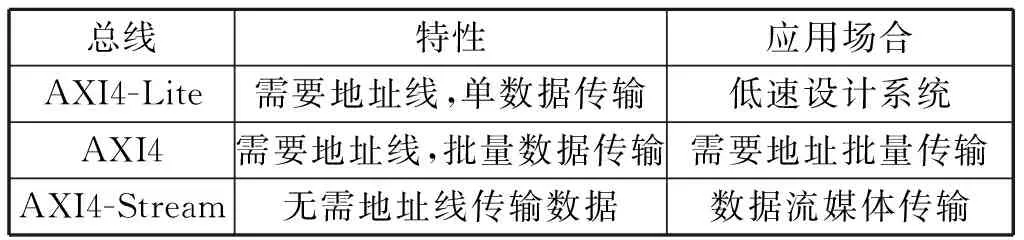

Zynq7 000支持AXI4-Lite、AXI4和AXI4-Stream 3種總線模式,表1列舉了3種AXI總線的特性。

表1 3種AXI總線比較

本模塊的設計需求是將以太網數據包轉化為JTAG命令,用于調試和下載FPGA,屬于低速應用,而 AXI-Lite總線結構簡單,適合這種小批量、簡單控制的場合,所以本模塊使用AXI4-Lite總線來傳輸ARM和FPGA之間的數據。

1.3 網絡交換設計

本模塊為Zynq7000設計的以太網接口,為簡化的千兆比特介質獨立接口(RGMII),該接口由IEEE 802.3-2000定義,支持10/100/1 000 Mbps傳輸速率,同時采用4位數據接口,有效減少了芯片接口管腳數目,通過Zynq7000 PS部分設計了支持AXI4-Lite總線的以太網MAC架構[4]。

為了交換對應不同板卡的以太網數據包,本模塊還在PC機和Zynq7000芯片設計了一個網絡交換模塊,該模塊的核心芯片選用了Realtek公司的RTL8305NB-CG芯片,它有5個端口,每個端口有獨立的媒體訪問控制地址(MAC)和物理層接口(PHY),支持10/100 M以太網交換,從調試PC發送的以太網數據包會通過接入端口向所有端口廣播,而對應的Zynq7000芯片收到廣播信息后,會根據對應信息選擇接收還是丟棄所收到的以太網數據包[5],從而完成本模塊設計的PTMP功能。

2 模塊系統軟件設計

2.1 XVC協議

本模塊軟件是基于Xilinx XVC協議設計,XVC協議是Xilinx公司推出的基于TCP/IP的虛擬線纜協議,允許用戶不使用傳統的USB線纜,而是通過以太網來遠程訪問FPGA的JTAG接口并對其進行調試,支持多種平臺。

2.2 Lwip協議

本模塊的網絡硬件接口為RGMII接口,同時通過Lwip協議實現以太網連接,Lwip協議是一種TCP/IP協議的小型化實現,最初由Adam Dunkels在瑞典計算機科學研究所的計算機和網絡架構(CNA)實驗室編寫。它實現的重點是在保持TCP/IP協議的主要功能情況下同時減少硬件RAM使用。這使得Lwip適用于小容量RAM或者ROM的嵌入式系統。現在Lwip已被移植到多個平臺和操作系統,無需底層操作系統都可以運行[6]。

Zynq7000通過Xilinx Vivado軟件的軟件開發工具(SDK)來實現Lwip協議,在Vivado軟件中通過一個知識產權(IP)核集成工具完成基于Zynq的硬件平臺設計,在搭建好硬件平臺后直接發送到SDK,然后再通過該平臺加載軟件程序。

2.3 系統軟件流程圖

本文基于Zynq7000芯片設計的軟件流程圖如圖3所示。

Processing_system7_0k模塊為Zynq7000的PS部分,首先負責所有外設驅動編寫,包括以太網、串口、DDR等,在設備啟動后首先將外設初始化,然后開始通過RGMII網口接收由調試PC發送的XVC協議以太網數據包,該數據包主要由以下3種命令組成:

l getinfo:

l shift:[number of bits][TMS vector][TDI vector]

l settck:[period in nanoseconds]

其中,getinfo命令檢索XVC服務的版本和TMS及TDI信號位移的最大指針長度,目前Xilinx使用的XVC服務為v1.0,TMS和TDI的最大指針長度和軟件應用定義的緩存深度有關,本模塊定義的最大長度為2 048,所以getinfo命令返回的字符串為xvcServer_v1.0∶2048 。

shift命令是XVC協議的主要命令,它由三部分組成,共6個字節,前4個字節指示TMS和TDI的指針長度,后面2個字節則是發送的TMS和TDI數據,該指令會返回同TMS指針向量同樣長度的TDO指針,代表從JTAG接口返回的全部TDO數據[7]。

圖3 系統軟件流程圖

settck命令主要用來設置TCK信號的時鐘周期,基本單位為ns,具體通過ASCII碼來定義。比如十進制100 對應的ASCII字符為D,將settck命令值設為D(即設置TCK信號的周期為100ns[8])。

另外2個模塊rst_processing_system7_0_100 M負責軟件模塊的復位,而processing_system7_0_axi_periph模塊則在解析PC機通過XVC服務發送的以太網包后,將解析過的命令通過AXI4-Lite總線寫入PL部分的寄存器,然后通過axi_jtag_0模塊轉換為JTAG時序連接到目標FPGA,從而完成調試。

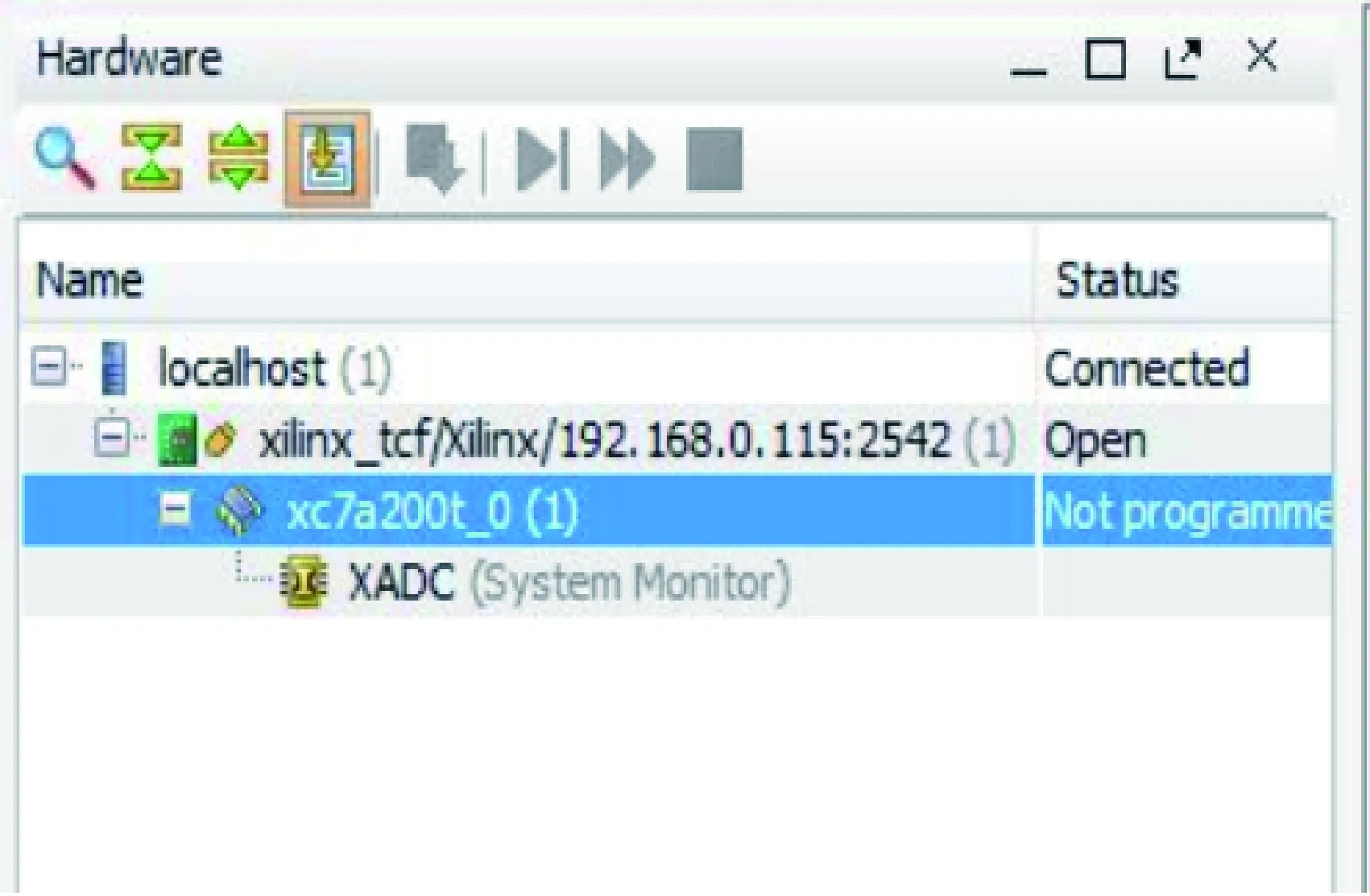

3 調試測試

本文的測試環境軟件為Xilinx Vivado軟件,打開Vivado軟件進入硬件管理界面,在TCL控制臺輸入指令,連接目標FPGA對應的IP地址,連接成功后開始對目標FPGA進行下載調試。如圖4所示,通過Vivado軟件的現場測試,將一個5 M的bit文件在線加載進FPGA所需時間為20 s左右,而通過Bpi模式燒錄mcs文件進入對應Flash時間大約為25 min。和傳統JTAG相比,調試下載速度基本一致,但對于現實設備上的板卡調試而言,該方法更加靈活方便。

圖4 目標FPGA連接成功

4 結束語

在本模塊中,調試PC通過網絡交換芯片,利用單網口可以訪問所有板卡對應的Zynq7000芯片,通過XVC協議將以太網數據包解析為JTAG命令,從而完成調試板載FPGA的目的。在實際設備應用中,僅需要一個交換芯片模塊,而將Zynq7000芯片集成在各塊板卡上,用來代替傳統的上電控制芯片。