一種基于PXI接口的大容量存儲技術的示波器設計

文/秦梅 蒲志

示波器是作為現代電子測量的重要儀器,廣泛應用于高速、瞬態信號的檢測、調試電路的一個重要工具,隨著科技的快速發展,示波器已經成為了一種集測量、分析、顯示、記錄等各功能于一體的智能測試儀器。尤其是數字存儲示波器作為智能測試儀器的代表被廣泛應用于各個測試領域。目前大部分的便攜式數字示波器市場被國外的廠商占據,國內便攜式數字示波器的研究開發起步較晚,多是一些低端產品,并且價格貴,阻礙了數字示波器在生產和試驗中的廣泛應用。本文在研究數字示波器原理的基礎上,提出了一種基于DDR2大容量存儲技術(高達64Msample)和FPGA的高仿真數字存儲示波器設計方案廣泛應用于各檢測完整系統,這些系統為生產測試、軍事和航空航天、機器監測、自動化和工業測試等應用提供服務。

1 功能指標分析及實現原理

本設計采用并行數據采集技術,2個通道ADC同時采樣,各個通道的量程檔可單獨設置。模塊采用大容量的存儲技術,總存儲深度可達64Msample/ch。系統原理框圖如圖1所示。

2 系統設計

2.1 PXI接口電路

PCΙ總線接口功能內核由FPGA來實現。用FPGA實現PCΙ接口協議,使得模塊硬件緊湊,易于在單槽PXΙ模塊上實現多通道功能,節省了成本和空間。

2.2 FPGA設計

由于本設計的可編程設計涉及到高速的時鐘域,連接ADC和DDR2的數據線都較多,綜合考慮性能、速度、容量、和可用Ι/Ο等因素,這里選用一片Xilinx公司Virtex4 FPGA芯片,適合作豐富的時鐘管理功能;并且具有ΙSERDES、ΙDELAY、ΙDELAYCTRL、DCΙ等資源,可對高速輸入的LVDS信號進行串并轉換、延遲控制、阻抗匹配控制。

由ADC送出的500M的高速LVDS采樣數據直接輸給FPGA,由FPGA內的多路復用器(DMUX)進行串并轉換,輸出4路并行的較低速(125MHz)的數據供FPGA內部邏輯使用,然后進行抽取,以實現不同的采樣率。

FPGA控制邏輯的一個重要部分是DDR2內存控制器,它將處理完后的數據寫入板載DDR2內存,實現存儲深度和預觸發長度,在VXΙ側將內存數據讀出并寫入緩存FΙFΟ中去。

結合主機指令,FPGA對每個模擬通道及其觸發電路進行單獨控制,并對每個通道的采集數據進行并行處理。

2.3 本地緩存電路

由于本設計要求的存儲深度很大,因此該項目的本地存儲器采用DDR2內存,每個通道兩片內存顆粒,構成128Mx32bit容量,因此最大支持每通道256M的存儲容量。根據研究及初步計算,內存外時鐘或FPGA內存控制器主時鐘為150MHz,適當增加fifo深度即可滿足500Msps采樣率下連續不丟點的數據存儲。因此,DDR2-400速度等級的內存芯片即可滿足要求。

2.4 時鐘電路

時鐘電路包括高速ADC時鐘和FPGA內部高速時鐘管理。本設計涉及的時基主要有500MHz時基和100MHz時基。100MHz時基采用高性能晶振來實現,晶振輸出送給FPGA后,由FPGA內的時鐘管理單元來產生各個頻率和相位的工作時鐘,主要指內存控制器的工作時鐘。500MHz時鐘也由晶振產生,經時鐘驅動芯片分配后送入ADC,ADC的輸出時鐘則送入FPGA,進行數據鎖存、抽取、觸發等功能。

2.5 信號調理電路

信號調理電路主要包含衰減、阻抗變換、增益細調、主放大、差分驅動這幾個部分。衰減部分實現20倍衰減功能,以便實現大的量程檔位,。

在示波器或數據采集中,為了減少對被測系統的電流索取,輸入阻抗通常達到1兆歐姆,而內部傳輸阻抗通常較小,因此需要阻抗變換。

3 電源設計

3.1 模擬部分

為了減小來自于背板對前端模擬部分的傳導干擾,可以采用FKC08-12D05的DC-DC隔離設計。由于DC-DC隔離電源為300KHZ的開關頻率及50mV的紋波,為進一步降低電源上的紋波,在每組電源中穿入BNX002-01的濾波器來降低紋波,可將動態紋波降低到10-20mV之間。

3.2 數字部分

在為高速SDRM及FPGA的內核電源的設計中采用高頻開關電源設計,由于為一體化的微型模塊,可為每組SDRAM提供低紋波、高效率、大動態范圍的優質電源,其開關頻率為1.25MHZ、紋波為10-12mV、4A的穩態電流(峰值6A),可滿足1.8V±0.1V的要求范圍。對于FPGA來講,由于要高速處理大量的數據,對內核1.2V的電源要求較以往的電源來講較為苛刻的要求,此電源不斷能提供低紋波、而且大動態范圍負載電流范圍的電源。此設計采用一體化的DC-DC+LDΟ的MΙC38300來為FPGA提供內核1.2V的電源。當1.5A輸出時可達到2mVp-p的低噪音。此性能可極大地為FPGA的可靠運行提供保障。

4 軟件設計

4.1 軟件系統架構

本設計的軟件包括設備驅動程序和PNP軟面板程序。設備驅動程序提供APΙ函數接口,設備驅動程序通過標準VΙSA函數實現對模塊硬件的訪問;PNP軟面板也即儀器軟面板,主要為用戶提供關于儀器的圖像化界面,同時也是基于設備驅動程序的一個應用示例。

4.2 主要程序算法

4.2.1 波形平滑

本設計的示波器采用實時采樣技術。波形平滑即平滑濾波,可以消除疊加在信號上的白噪聲。程序運用算術平均濾波,公式為y=(x1+x2+…+xn)/n,這里n為2、4、8、16、32、64可選。

4.2.2 波形插值

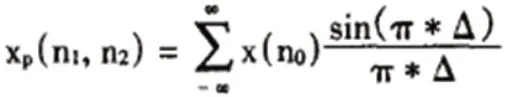

利用插值算法,可通過函數在有限個點的取值情況,估算該函數在別處的值,即通過有限的數據以得出完整的數學描述。據Nyquist理論,一個頻率為f的信號,可以由頻率大于等于2f的均勻采樣離散樣品來替代,而不丟失任何信息。理想抽樣函數為Sa=Sin(x)/x,由離散樣品恢復原函數,只需將抽樣函數通過截止頻率為Wm的低通濾波器即可,理論上相

當于抽樣函數進行時間卷積:

其中fn為離散樣品的幅值,Sa(WmT-nп)為抽樣函數。因為實時采樣為等間距采樣,波形恢復公式可變為:

式中Xp(n1,n2)為相鄰的第n1個和第n2個采樣點之間要插的第p個點的值,

X(no)為第n個采樣點的值,Δ由兩個采樣點之間要插的點數m和p,以及n1、n0的位置來計算,由計算公式Δ=(p/m)+n1-n0即可得出。本設計設計的示波器采用實時采樣技術,利用插值恢復顯示波形。

5 結束語

在設計時,要特別注意所選器件的帶寬、增益、輸入特性等性能指標,在PCB的設計上還要注意傳輸線的阻抗匹配等問題。

在FPGA設計中,另一個關鍵的問題是,SDRAM內存控制器的設計不但要符合所選內存芯片的各項參數特性,而且最重要的是必須結合數字存儲示波器所特有的采集、存儲、讀取等一系列操作。為此,我們專門設計了DDR2控制器,并對它們進行了行為級和門級的測試仿真。