基于FPGA 的弱電網下并網逆變器控制器研究

趙鑫,陳國初,張子騫,朱志權

(1.上海電機學院電氣學院,上海201306;2.格拉茨技術大學電力系統研究所,奧地利格拉茨;3.上海電氣風電集團,上海200241)

0 引言

近年來,由于化石能源等不可再生資源的短缺,風能、太陽能等可再生能源得到了越來越廣泛的應用。但這些可再生能源分布廣泛,無法集中利用發電,因此對分布式發電技術的研究就顯得愈發重要。

目前,由于越來越多的電力電子器件應用于電網當中,較多的非線性負載帶來了電網諧波污染的問題。分布式能源之間距離遠、地址位置偏,因此在電能傳輸的過程中,傳輸線路的距離增長,變壓裝置較多,使得在并網逆變器以及電網之間的阻抗較大。此時,電網呈現弱電網特性[1]。

在并網逆變器控制器中,鎖相環(PLL)是目前使用最普遍的相位同步方法,它能夠捕獲實時的相位信息,在電壓畸變以及三相不平衡條件下,能夠準確、快速地鎖定電壓相位,因此其性能對于整個控制系統至關重要。鎖相環(PLL)的結構可以分為3 種類型:基于過零點檢測的鎖相環,結構簡單,且無法準確跟蹤電壓相位;基于靜止坐標系的鎖相環以及基于同步旋轉坐標系的鎖相環不能在電網不平衡時具備良好的性能。如何在弱電網條件下保證鎖相環的良好性能十分必要。文獻[7]分析了鎖相環在輸出導納矩陣中的影響,表明鎖相環可能帶來低階諧波震蕩,說明了鎖相環在逆變器并網過程中會帶來較大的影響;文獻[8]采用在三相同步鎖相環(SRF-PLL)添加移動平均濾波器實現了獲取精確的相位信息的功能,但是這種方式不適用于弱電網條件下,逆變器控制器在電網故障條件下的控制準確度不高;文獻[13]采用了一種雙二階廣義積分器的鎖相環(Dual Second- Order Generalized Integrator-PLL,DSOGI-PLL)算法,實現在電網不平衡、含有諧波或電壓畸變情況下的準確鎖相,但這種鎖相環建模比較復雜。

本文提出使用采用三相同步鎖相環對逆變器的控制器進行設計,并在FPGA 中進行建模,使得控制器精度較大提高,能夠實現弱電網比較容易受到擾動的情況下,對電網電壓的精準鎖相,提高了并網逆變器控制器的準確性以及快速性,完成CHIL 仿真實驗驗證了設計的正確性及可行性。

1 并網逆變器控制器研究

如圖1 所示為PLL 下的dq 變換向量圖,PLL 影響下的dq 變換使系統產生δ 的相移,電網系統的相角為θg,PLL 的相角為θPLL,而δ=θg-θPLL,可見影響逆變器穩定性的有電網和PLL 兩個因素,而電網相角θg為固定值,所以我們應該對θPLL進行研究。

圖1 PLL下的dq變換向量圖

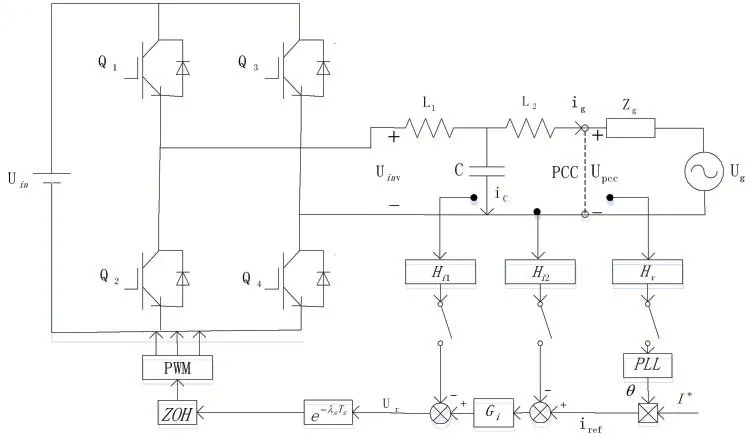

逆變器與無限大母線相連,取三相電流i 與三相電壓U 進行dq 變換,Uq進行鎖相環控制,經PI 控制器、積分取余之后得到電網與逆變器的相角差θ,將相角差θ 反饋給三相電壓電流進行Park 變換與逆Park 變換,Park 變換得到的id、iq經PI 積分器之后進行解耦,得到進行反dq 變換得到新的三相abc 電壓,實現了逆變器控制器對電網電壓的鎖相控制。如圖2 所示為三相同步鎖相環(SRF-PLL)的控制原理框圖。

圖2 并網逆變器及控制拓撲結構圖

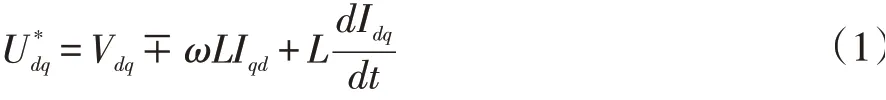

其中,派克變換部分的數學表達式為:

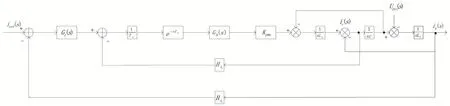

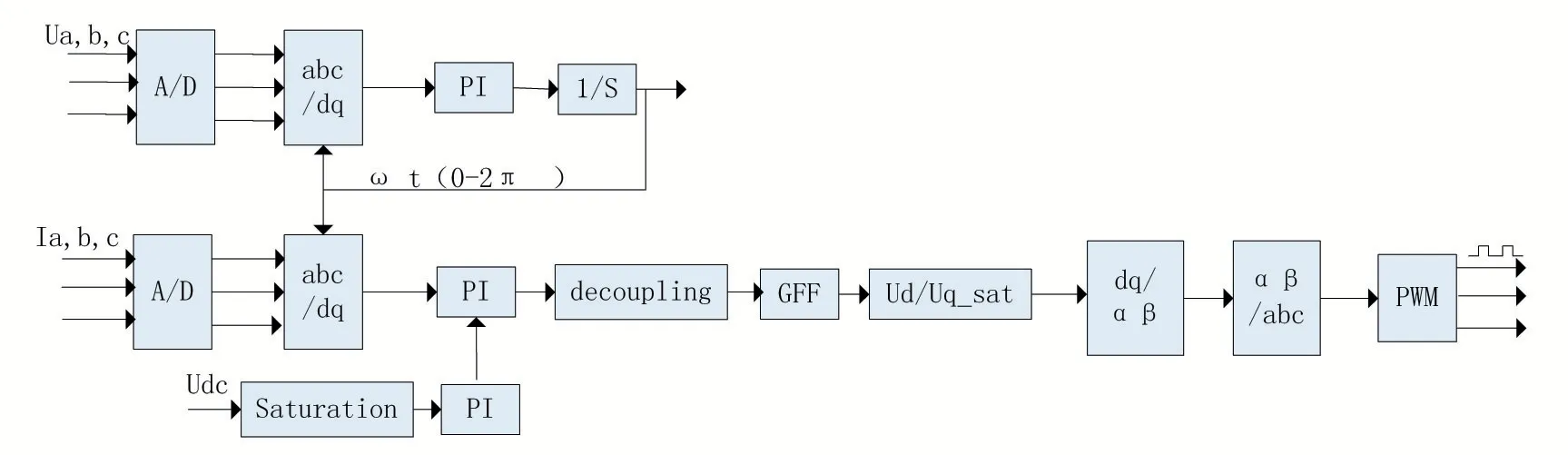

SRF-PLL 是最常見的一種鎖相環,其原理為三相電壓(電流)經過Park 變換之后,將q 軸變量經PI 之后經積分環節產生相角Δθ,將其反饋給dq 變換,形成閉環結構。圖3 為并網逆變器控制原理框圖。

2 基于FPGA的逆變器控制器實現

如圖4 所示為FPGA 中逆變器控制器設計框圖,Uabc、Iabc為從dSPACE 接收的三相電網電壓以及由逆變器產生的電流,經ADC 數據采集卡接收電壓電流數據,由于dSPACE 發送的數據為0-5V,在ADC 采集數據之后需要進行數值的變換,經數值上浮之后變換為電壓為-400-400V,電流變換為-25-25V。數值變換后的電壓電流經dq 變換,三相電壓變換后得到Uq=0,將Uq經PI 控制器之后積分得到電網電壓相角,與2 π 進行比較之后得到相角差ωt(0-2 π)并反饋給三相電壓與三相電流進行dq 變換,實現鎖相控制。

將三相電流dq 變換之后得到的Id、Iq經PI 控制器,Udc為直流母線電壓,對Udc進行數值變換,進行限幅,經PI 控制器得到直軸電流給定值Idref,實現了直流母線與控制器之間的雙向控制。將三相電流經dq 變換之后的Id、Iq與Id、Iq經PI 控制器得到的UPI-d-out、UPI-q-out進行解耦控制。

GFF 為電壓前饋模塊,將解耦后的Ud、Uq與三相電壓進行dq 變換之后得到的Ud、Uq進行電壓前饋,實現電壓前饋控制,并對電壓環控制所得到的新的Ud、Uq進行限幅。將得到的新的Ud、Uq進行逆dq 變換,得到新的Uabc與Udc生成帶死區的PWM 波,并反饋給dSPACE。

圖3 并網逆變器控制原理框圖

圖4 FPGA中逆變器控制器設計框圖

3 基于CHIL的并網逆變器控制的實現

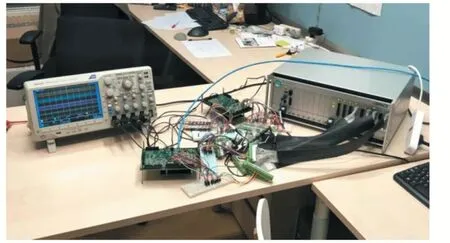

如圖5 所示為控制器硬件在環(CHIL)的整體實驗框架,FPGA 中主要完成逆變器控制器的模型搭建,設置整個模型運行在10KHz 下。dSPACE 中主要完成逆變器模型的搭建,其中逆變器模型是基于Simulink 搭建的,設置此模型運行在20KHz 下。

dSPACE 經D/A 傳輸三相電壓以及三相電流給FPGA 的A/D,FPGA 接收到dSPACE 的電壓電流信號之后,進行dq、PLL、PI、逆dq 等,經FPGA 的輸出引腳輸出三相PWM 至dSPACE 的I/O 接口,經過FPGA 的輸出引腳時需要進行數值轉換、數字大小變換等,使得三相PWM 信號能夠完整地傳遞到dSPACE。

圖5 CHIL實驗整體框架圖

dSPACE 接收FPGA9607 發出的PWM 波,然后轉換成占空比對逆變器模型進行控制,然后采集電網電壓U 及電流I 通過D/A 轉換傳送給FPGA9607,由于dSPACE 的D/A 輸出接口具有輸出范圍限制,因此在采集電網電壓U 及電流I 之后需要對其波形進行抬高及縮小幅值處理,使其幅值在D/A 口輸出范圍內。

通過Simulink 搭建了逆變器模型、電網模型、逆變器控制器模型,由于dSPACE 可以與Simulink 實現互通,因此將Simulink 直接導入dSPACE controldesk 中即可,其中逆變器模型通過由FPGA9607 輸入的PWM 波進行控制。設置電網中的電阻阻抗較小,可以模擬弱電網情況下的逆變器并網環境。

4 實驗結果

如圖6 為CHIL 實驗搭建平臺,包括dSPACE 構建的仿真器,NI9607 構建的控制器。在現實情況中電網一直處于運行狀態,而逆變器處于準備并網狀態,因此在實驗時dSPACE 空跑,FPGA 中逆變器控制器模型處于RESET 狀態。之后逆變器并網,逆變器控制器開始工作,控制器接收到dSPACE 傳遞的三相電壓、電流,打開PLL 的RESET,使dq 變換抓住電壓相位,打開PI的RESET,對PI 進行軟啟動,進行三相電流的dq、反dq 變換,逆變器控制器對逆變器的橋臂開關進行控制得到pwm 波形,反饋給dSPACE,對逆變器進行控制。

圖6 CHIL實驗實物圖

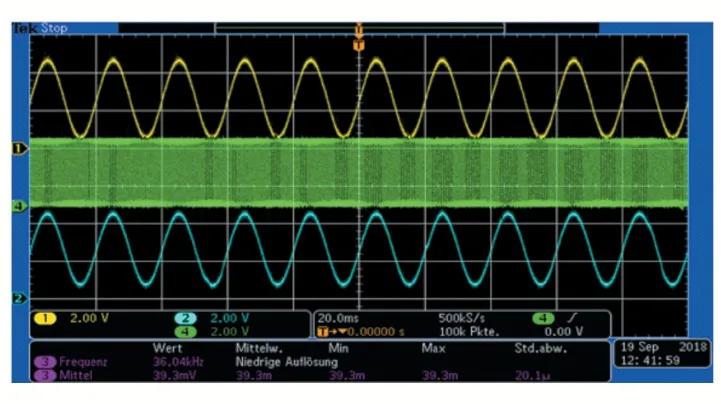

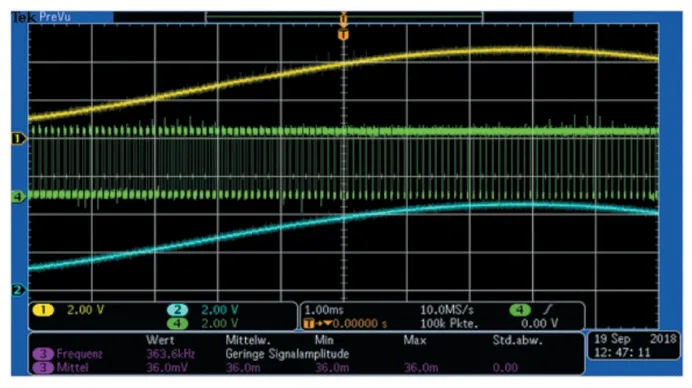

如圖7、圖8、圖9 所示為CHIL 實驗模擬電網平衡與電網不平衡條件下的實驗結果圖,黃色為dSPACE發送的Ua 波形,綠色為輸出一相SPWM 波形,藍色為dSPACE 經FPGA 給定之后輸出的Ia 波形,可見兩個正弦波形的相移幾乎為零,達到了利用FPGA 快速精確控制的目的。

圖7 模擬電網正常情況下實驗結果圖(1)

圖8 模擬電網正常情況下實驗結果圖(2)

圖9 模擬電網不平衡條件下的實驗結果圖

5 結語

從實驗結果可以看出,本文設計的基于NI9607 的FPGA 核心板設計的逆變器控制器能夠很好地對弱電網情況下并網逆變器進行控制,在電網正常條件下,可以實現較好的鎖相控制;在電網發生低電壓穿越時,設計的逆變器控制器能夠實現穩定的控制,并能夠較快速地恢復運行。因此設計的逆變器控制器能夠在弱電網條件下,在電網的正常以及故障條件下實現快速、穩定、精確地控制。