基于線性混頻技術的注入鎖定四分頻器

王琳 吳偉斌

摘 要: 基于TSMC 0.13 μm CMOS工藝,提出并設計了一款新穎的注入鎖定四分頻器。傳統的諧波混頻注入鎖定四分頻器限制了鎖定范圍,新方法采用線性混頻技術、基于交叉耦合振蕩器結構設計了一款寬帶鎖定范圍的注入鎖定四分頻器。仿真結果表明,在1 V的電壓偏置下,分頻器取得了8.2~13 GHz的工作頻率,鎖定范圍為4.8 GHz (45.3%),消耗的功耗為5.2 mW,相位噪聲取得了-135.7 dBc/Hz@1 MHz的良好性能,版圖大小為0.93 mm×0.62 mm。

關鍵詞: 四分頻; 注入鎖定分頻器; LC諧振器; 線性混頻; 鎖定范圍

中圖分類號: TN432

文獻標志碼: A

文章編號:1007-757X(2019)06-0011-03

Abstract: A novel injection-locked 4-frequency divider (IL4FD) was proposed and implemented in the TSMC 0.13 μm CMOS process. The conventional harmonic mixer IL4FD has limited locking range, but the new one shows a wide locking range IL4FD by using linear mixer technique and cross-coupled voltage-controlled oscillator structure. The post-layout simulation results show that, at the voltage bias of 1 V, the locking range is 4.8 GHz (45.3%) from 8.2 to 13 GHz with the power consumption of 5.2 mW. The phase noise of the circuit achieves a good result of -135.7 dBc/Hz@1 MHz, and the size of layout is 0.93 mm×0.62 mm.

Key words: Divided by 4-frequency; Injection-locked frequency divider; LC resonator; Linear mixer; Locking range

0?引言

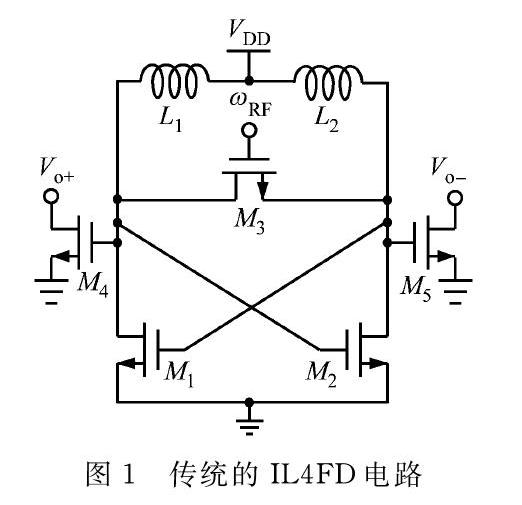

LC諧振注入鎖定頻率分頻器(LC ILFD)在超高速鎖相環電路以及其他的頻率信號處理電路中應用廣泛,雖然LC ILFD相比較于基于環形振蕩器結構的ILFD而言,鎖定范圍有限,但是功耗較低。LC ILFD通常作為鎖相環分頻器模塊的第一級,以在較高工作頻率下取得更低的功耗,注入鎖定四分頻器(IL4FD)屬于ILFD的更高次分頻模塊,由于其在電路物理上與注入鎖定二分頻器(IL2FD)不同,而得到了更多的關注,單級IL4FD可以取代兩級IL2FD,從而降低頻率對不準的概率,改善信號的性能。傳統的IL4FD直接采用交叉耦合振蕩器結構[1-3],鎖定范圍不夠大,例如圖1所示即展示了一款傳統的IL4FD電路,在混頻單元M3處存在著輸入輸出的頻率關系,即:ωRF-3ωo=ωo,ωo為輸出信號頻率,ωRF為注入的射頻信號頻率,3ωo則為由M3的非線性引起的輸出頻率的3次諧波分量,該結構可以通過提高電壓的方式提高三次諧波分量的幅值,進而增加鎖定范圍,但是這是以功耗的增加為代價的。

本文提出了一種采用線性混頻技術以及電容交叉耦合結構[4-6]的寬鎖定范圍IL4FD。由于采用線性混頻技術的緣故,IL2FD相比其他高次分頻器模塊而言,具有更大的鎖定范圍,因而,為了實現較寬的鎖定范圍,IL4FD采用線性混頻技術應該是一個較好的方法,以往文獻報道的采用線性混頻技術的IL4FD通常使用兩個或兩個以上的注入MOS晶體管[7-10],而本文所提出的寬帶IL4FD只需要采用一個注入MOS晶體管,該分頻器取得了8.2~13 GHz的工作頻率,鎖定范圍為4.8 GHz (45.3%),消耗的功耗為5.2 mW。

1?電路設計

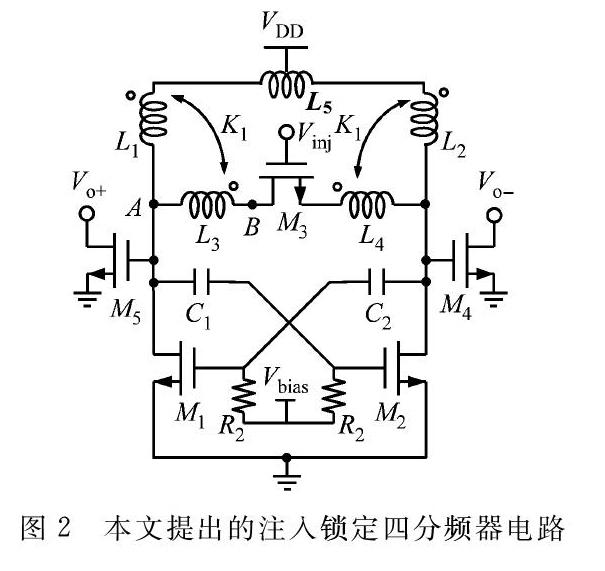

本文所提出的IL4FD電路圖,如圖2所示。

其中,由晶體管M1和M2組成的電容交叉耦合對用于產生負電阻,電阻R1和R2為偏置電阻,C1和C2為直流隔直電容,當偏置電壓Vbias增大時,功耗增加,電路中主要的諧振器由電感L1、L2、L5以及跨接開關晶體管對漏極的寄生有源電容2Cp組成,帶有直流柵極偏壓Vinj的晶體管M3為注入晶體管,電感L3和L4與晶體管M3串聯,晶體管M4和M5組成輸出緩沖器,當Vinj較低時,晶體管M3關斷,當Vinj較高時,晶體管M3開啟,電路的空載振蕩頻率隨著Vinj的增加而增加,由于電感L3、L4與晶體管M3串聯,因而即使M3處于完全開啟狀態,IL4FD電路仍然能夠振蕩。

用于說明IL4FD電路功能的框圖,如圖3所示。

在空載模式下,晶體管M3漏極-源級之間的頻率為ω0,在注入鎖定狀態下時,首先分頻器采用輸入信號ωRF與ω0產生輸出信號ωRF±ω0(=3ω0,5ω0),輸出信號又被作為混頻器的輸入信號,最終,混頻器產生輸出信號為ωRF-3ω0=ω0,5ω0-ωRF=ω0,該方法稱為線性混頻技術。仿真表明電感L3的引入增加了節點A處的高頻阻抗,電感L1和L3之間的互感系數K1進一步增加了節點A處的高頻阻抗,進而增加了在節點A處3ω0信號產生的概率,加寬了鎖定范圍。

2?電路仿真以及討論

基于TSMC 0.13 μm CMOS工藝對本文所提出的IL4FD電路進行設計,采用Cadence軟件進行仿真,該電路的版圖,如圖4所示。

版圖大小為0.93 mm×0.62 mm,當固定VDD=1 V,Vbias=0.6 V時,變化Vinj,對電路進行仿真,工作頻率和鎖定范圍隨著Vinj變化的版圖后仿真結果如圖5所示。

圖5?當固定VDD=1 V,Vbias=0.6 V時,變化Vinj時,IL4FD電路的靈敏度仿真結果隨著Vinj的增加,電路的鎖定范圍逐漸上移,并且在Vinj=6 V時,得到最大的鎖定范圍,此時取得了8.2~13 GHz的工作頻率,鎖定范圍為4.8 GHz (45.3%),此刻電路所消耗的功耗為5.2 mW。隨著Vinj的增加,電路的空載振蕩頻率增加,鎖定范圍中間值也逐步向著更高的頻率移動。該電路的相位噪聲仿真結果,如圖6所示。

由圖可見,相位噪聲取得了-135.7 dBc/Hz@1 MHz的較優性能,電路的整體性能優于以往文獻所報道的結果[11-13]。

3?總結

傳統的IL4FD電路大多采用非線性混頻技術,增益較低,鎖定范圍受限,近來線性混頻技術逐漸應用于IL4FD電路中,雖然鎖定范圍可以得到有效的展寬,但是卻采用了兩步混頻技術,而本文只需采用一步混頻技術,即可實現更寬的鎖定范圍,降低了電路規模以及功耗。基于所提出的技術,本文設計的IL4FD電路采用一個注入MOS晶體管與兩個耦合電感串聯,版圖后仿真結果表明,該電路取得了8.2~13 GHz的工作頻率,鎖定范圍為4.8 GHz (45.3%),電路所消耗的功耗為5.2 mW。

參考文獻

[1]?Jang S L, Liu C H, Chang C W, et al. A low-voltage, low power divide-by-4 LC-tank injection-locked frequency divider [J]. International Journal of Electronics, 2011, 98(4): 521-527.

[2]?Jang S L, Chang Y T, Hsue C W, et al. Wide-locking range divide-by-4 injection-locked frequency divider using injection MOSFET DC-biased above threshold region [J]. International Journal of Circuit Theory and Applications, 2016, 44(5): 968-976.

[3]?Wu L, Luong H C. A 0.6 V 2.2 mW 58-to-73GHz divide-by-4 injection-locked frequency divider [C]// Processing IEEE Custom Integrated Circuits Conference (CICC), Sep. 2012: 1-4

[4]?Jang S L, Lin C Y. Wide-locking range class-C injection-locked frequency divider [J]. Electronics Letters, 2014, 50(23): 1710-1712.

[5]?Jang S L, Chen Y J, Fang C H, et al. Enhanced locking range technique for frequency divider using dual-resonance RLC resonator [J]. Electronics Letters, 2015, 51(23): 1888-1889.

[6]?Jang S L, Fang C H. Divide-by-4 capacitive cross-coupled injection-locked frequency dividers [J]. Analog Integrated Circuits and Signal Processing, 2016, 86(1): 59-63.

[7]?Jang S L, Fu C C et al. Wide locking range divide-by-4 LC-tank injection-locked frequency divider using series-mixers [J]. ?Analog Integrated Circuits and Signal Processing, 2014, 78(2): 523-528.

[8]?Jang S L, Liu W C. Injection-locked frequency divider using single-injected dual-injection MOSFETs [J]. Microelectronics Journal, 2015, 46(12): 1409-1412.

[9]?Jang S L, Huang J F, Lin F B. Wide-locking range LC-tank divide-by-4 injection-locked frequency divider using transformer feedback [J]. International Journal of RF and Microwave Computer-Aided Engineering, 2015, 25(7): 557-562.

[10]?Chang C W, Jang S L. LC-tank divide-by-4 injection-locked frequency divider using the second-order harmonic feedback [J]. International Journal of Electronics, 2014, 101(2): 204-211.

[11]?Li S M, Yeh H N, Chang H Y. A V -band 90-nm CMOS divide-by-10 injection-locked frequency divider using current-reused topology [J]. IEEE Microwave and Wireless Components Letters, 2018, 28(1): 76-78.

[12]?Wu L, Luong H C. Analysis and design of a 0.6 V 2.2 mW 58.5-to-72.9 GHz divide-by-4 injection-locked frequency divider with harmonic boosting [J]. IEEE Transactions on Circuits and Systems I, 2013, 60(8): 2001-2008.

[13]?Dyskin A, Kallfass I. Analytical approach for SiGe HBT static frequency divider design for millimeter-wave frequency operation [J]. IEEE Transactions on Microwave Theory and Techniques, 2018, 66(3): 1411-1417.

(收稿日期: 2018.06.08)