基于FPGA的電路板多功能測試設備

葛 亮

(西安烽火電子科技有限責任公司,陜西 西安 710000)

0 引 言

隨著硬件電路設計的復雜程度不斷提升,電路規模越來越大,對硬件電路的檢測提出了更高的要求。電路測試效果對保證產品質量具有重要影響。通過反饋測試結果,可在產品研發初期發現存在的問題,從而有助于更好地完成產品設計。大規模電路設計過程中,電路測試對產品設計成本同樣具有重大影響。優良的電路測試方案是復雜電路設備良好運行的重要保障之一。

1 多功能測試儀原理

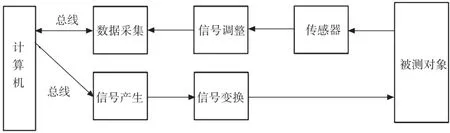

PCB電路板在設計和生產過程中對其性能和功能測試是重要環節。測試方案流程如圖1所示。PCB測試儀的整體框架可以劃分為信號產生電路和信號檢測電路兩大部分[1]。首先由測試儀產生用于測試的激勵信號,將激勵信號輸入被測對象,然后通過傳感器檢測被測對象反饋的響應信號,并對檢測信號進行相應的處理,轉換為處理器能夠識別的數字信號,再通過信號分析處理將輸出的檢測結果上傳至上位機。

多功能測試儀相比于單功能測試儀功能多樣,能夠實現數據互通、時鐘同步以及數據共享等多個功能,具備測試多個單項功能的能力,實現了對PCB測試功能的高度集成,降低了設備的體積、復雜度以及成本。需要說明的是,多功能測試儀的硬件和軟件設計并非是多個單功能測試儀的簡單累加。

圖1 測試方案流程圖

2 多功能測試儀方案設計

多功能測試儀主要涉及的內容包括輸入激勵和測試結果分析。輸入激勵一般是簡單的電壓信號或者是復雜的信息通信協議。多功能測試儀包含的主要測試功能包括AD數據采集、頻率測試、通信協議以及可編程接口等。其中,AD采集能夠將模擬信號轉換為數字信號,用來測試DC直流電源的輸出電壓值,檢測其輸出電壓是否滿足設計要求。頻率測試用于測試系統中周期性信號的頻率是否與設計要求一致,可以檢測信號頻率的精度。常見的通信協議測試包括標準RS232、標準I/O口、SPI串口通信以及IIC串口通信等。可編程接口主要指根據一些特殊功能要求對接口進行二次開發,如信號時序分析等[2]。

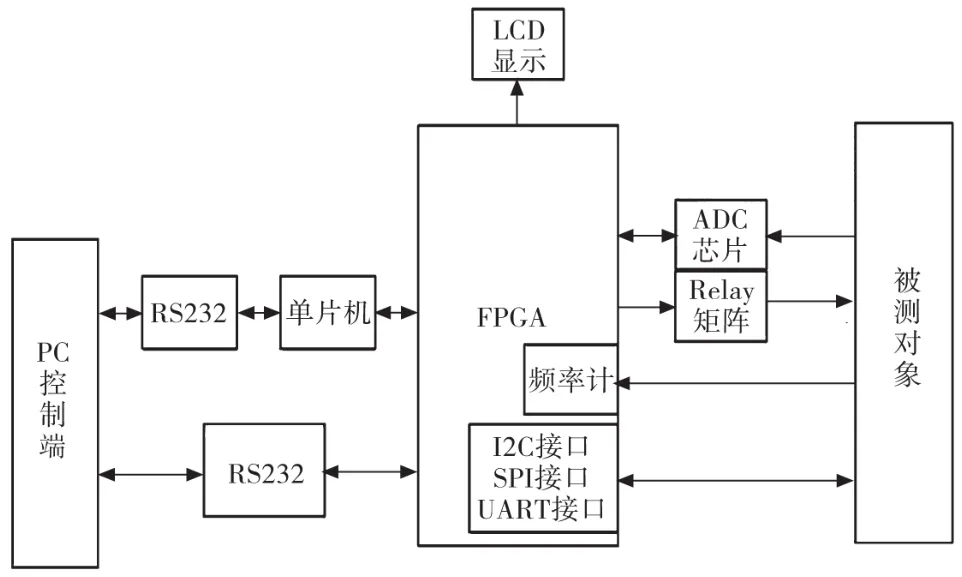

為實現以上測試功能,多功能測試儀的硬件設計結構如圖2所示。系統主要包括AD采集模塊、頻率計模塊、FPGA、Relay模塊以及通信接口等。其中,AD轉換芯片選用AD7490,為12位轉換芯片,具備16路AD轉換通道,最大數據輸出速度達1 MSPS。頻率計模塊主要實現對數字信號的頻率值運算。FPGA處理芯片是整個系統的核心處理器,負責系統的整體控制。Relay模塊能夠控制被測對象的供電,同時對特殊信號進行環回。通信模塊主要用于上位機的通信,接收上位機指令并將指令轉換為對應的電平信號,將電平信號輸入FPGA,同時可讀取FPGA存儲的檢測結果數據將其傳輸至上位機。

圖2 多功能測試儀硬件設計結構

2.1 FPGA模塊設計

FPGA處理器是該多功能測試儀的核心處理單元,選用Altera公司生產的EP2C8Q208型號芯片。該型號芯片屬于Cyclone II系列芯片,是低成本芯片,采用K絕緣材料工藝,可大幅度降低芯片造價,降低系統的設計成本。FPGA芯片提供了40個IP核,包含了較常用的嵌入式處理器、存儲器、傅里葉變換模塊以及數字濾波模塊等功能模塊,在電子通信、自動化控制以及嵌入式計算機等硬件開發中得到了廣泛應用。它集成了8 000多個邏輯資源和36個存儲模塊,同時提供NIOS和PLL開發資源。將FPGA作為主控芯片,外圍連接AD、Relay模塊、頻率計模塊、LCD指示燈以及通信接口等外圍設備,且規定了各外圍設備的接口定義[3]。FPGA的I/O接口電壓選用3.3 V電壓,內核選用1.2 V電壓,PLL核心電壓選用1.2 V電壓。為抑制高頻雜波干擾,在供電電壓上并聯0.1 μF電容。

2.2 單片機模塊設計

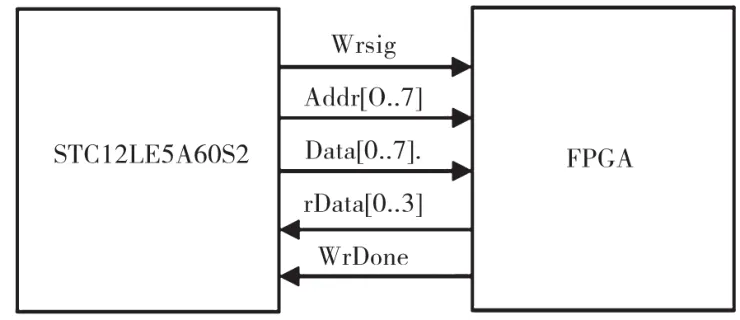

系統選用的單片機型號為STC12LE5A60S,其I/O端口電壓為3.3 V。端口電壓可以與FPGA端口兼容,直接連接FPGA端口,簡化了端口連接電路。單片機主要負責與上位機的信息通信,同時與FPGA進行數據交互。單片機晶振選用11 MHz晶振,與上位機串口通信的波特率選用115 200 b/s。單片機與FPGA直接的并行通信端口選用8位地址線、8位寫入數據線以及4位讀出數據線,同時設置了讀寫控制端口。當讀出控制端口為低電平時,地址線表示的地址為需要進行讀出的地址位置,按照地址線表示的地址讀取數據;當寫入控制端口為低電平時,地址線表示的地址表示數據的寫入,按照地址線表示的地址寫入數據。單片機與FPGA通信連接示意圖如圖3所示[4]。

圖3 單片機與FPGA通信連接示意圖

2.3 頻率計模塊設計

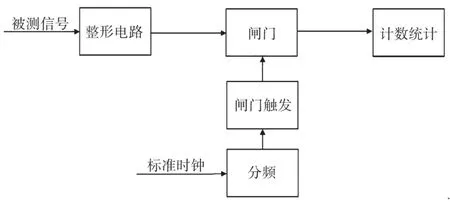

工程上常用的頻率測試具有多種方案,共同點均是針對被測對象的工作頻率范圍和特點進行設計。測量方法的選擇與頻率的測量精度有直接關系,應根據不同的應用場合選擇相適應的測試方案。其中,直接頻率測量法是最簡單且應用最廣的測試方法。直接頻率測試法原理如圖4所示。該方案的主要原理是在規定的時間內,利用FPGA統計被測對象的周期個數。一般檢測時間設定為500~1 000 ms。在檢測時間內,系統計數并統計被測對象觸發的脈沖數據,在計時結束時通過讀取脈沖計數數目計算出被測對象的頻率數值。

圖4 直接頻率測試法原理

被測對象的工作頻率范圍一般較大,為1 Hz~50 MHz。為了適應頻率檢測范圍,采用不同的觸發方式檢測低頻和高頻。當待測頻率較高時,設定時間寬度較短的檢測時間;當待測頻率較低時,可采用較長的檢測時間。頻率大于10 MHz的信號定義為高頻信號,低于10 MHz的信號定義為低頻信號。分頻晶振輸出的標準信號將分頻信號作為觸發器的參考信號,然后在參考信號內對脈沖進行采集判斷,從而實現脈沖個數的計數統計。

3 軟件設計

系統FPGA軟件開發工具采用Quartus Ⅱ軟件。它是第四代FPGA開發工具,支持多種開發方式,集成了多種開發語言。Quartus Ⅱ軟件集成了綜合器,可對輸入的編程語言或原理圖進行編譯和綜合,同時通過代碼檢測和仿真排查程序中的錯誤或警告,實現在線仿真驗證。軟件開發流程可以概況為需求分析、模塊分類、模塊輸入、程序仿真以及程序下載等過程。系統軟件開發過程如圖5所示。

圖5 系統軟件開發過程

4 結 論

傳統電路測試需要根據測試功能需要采用多臺測試儀器實現多種功能的測試,測試成本較高且測試結果不穩定。與測試儀相比,提出的多功能測試儀設計方案將多種功能測試進行集中設計,集成了電壓AD檢測、頻率檢測以及通信接口檢測等多種功能,降低了硬件設計復雜度,簡化了系統結構,在實現多功能測試的基礎上降低了設備成本。