基于FPGA的AMI編解碼設計

左磊 程煜洋 趙曉東 方圓

摘? 要:在基于FPGA的基帶傳輸系統研究中,通過對AMI碼型的研究,提出了一種通過Altera公司Cyclone Ⅱ系列EP2C35F672C6芯片實現AMI編解碼設計的方法。使用Quartus Ⅱ和ModelSim仿真平臺對設計方法進行仿真,結果符合AMI編解碼原理,解碼輸出與基帶信號一致,最終結果符合預期。AMI編解碼能夠實現在電路相對簡單的情況下,即使碼元極性與發端相反,接收端也能正確接收,為信號傳輸帶來了一種可靠的方法。

關鍵詞:FPGA;AMI;編解碼

中圖分類號:TN912.3? ? ? 文獻標識碼:A 文章編號:2096-4706(2020)20-0085-03

AMI CODEC Design Based on FPGA

ZUO Lei,CHENG Yuyang,ZHAO Xiaodong,FANG Yuan

(North China University of Technology,Beijing? 100144,China)

Abstract:In the research of FPGA-based baseband transmission system,through the study of AMI code pattern,a method to realize AMI CODEC function through Alteras Cyclone Ⅱ series EP2C35F672C6 chip is proposed. Using Quartus Ⅱ and ModelSim simulation platform to simulate the design method,the result conforms to the AMI CODEC principle,the decoding output is consistent with the baseband signal,and the final result is in line with expectations. AMI CODEC can realize that under the condition that the circuit is relatively simple and the polarity of the code is opposite to that of the originator,the receiver can receive it correctly,which brings a reliable method for signal transmission.

Keywords:FPGA;CMI;CODEC

0? 引? 言

AMI碼全稱是傳號交替反轉碼,其對應的波形正負脈沖交替,無直流成分,且具有很小的低頻成分,在不允許直流、低頻成分通過的信道傳輸中大量使用。常見的數字基帶傳輸碼有:AMI碼、NRZ碼、RZ碼、CMI碼和曼切斯特碼。AMI是一個比較有代表性的碼型,高、低電頻分量少,能量集中在頻率為1/2碼速處;編解碼電路簡單,且可以利用傳號極性交替這一規律來觀察誤碼情況。隨著科技的快速發展,電子計算機、大規模集成電路、超大規模集成電路以及微處理器技術得以更新換代,FPGA器件作為超大規模、超高速的可編程邏輯器件,也得以迅猛發展。由于其具有高集成度、高速、可編程、硬件描述語言的可修改性、低功耗、開發周期短、硬件與軟件并行性等優點而被廣泛應用。筆者所在實驗室在2020北京市的大學生科學研究與創業計劃項目中,研究的對象是基于FPGA的程序設計,在相關專業知識的的啟發下,對基于FPGA的AMI編解碼的設計展開了研究。對AMI的編碼規則、解碼方法進行詳細分析,利用Quartus Ⅱ軟件設計程序,再通過ModelSim平臺進行仿真。本論文闡述了對基于FPGA的AMI編解碼的設計實現,設計原理和結果分析。

1? AMI編解碼規則

AMI碼是傳號交替反轉碼,編碼規則是將消息碼中的“1”(傳號)交替變換為“+1”和“-1”,而“0”(空號)保持不變。例如:

消息碼:1? 0? 1? 1? 0? 0? 0? 1? 1? 0

AMI碼:-1? 0? 1? -1? 0? 0? 0? 1? -1? 0

AMI碼是具有正、負、零三種電平的脈沖序列。可以看成單極性波形的變形,“0”仍然為低電平,“1”時正負電平交替變換。

由AMI碼的編碼規則,就有了解碼的設計思路:當AMI碼為“+1”或“-1”時,輸出“1”;AMI碼為低電平時,輸出為“0”。

2? AMI編解碼系統設計

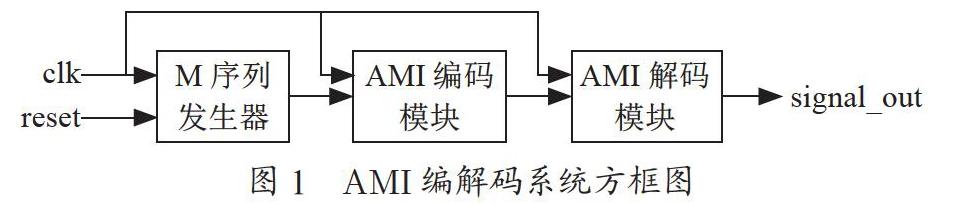

AMI編解碼系統方框圖如圖1所示,該系統由輸入信號clk、reset、M序列發生器模塊、AMI編碼模塊和AMI譯碼模塊組成。

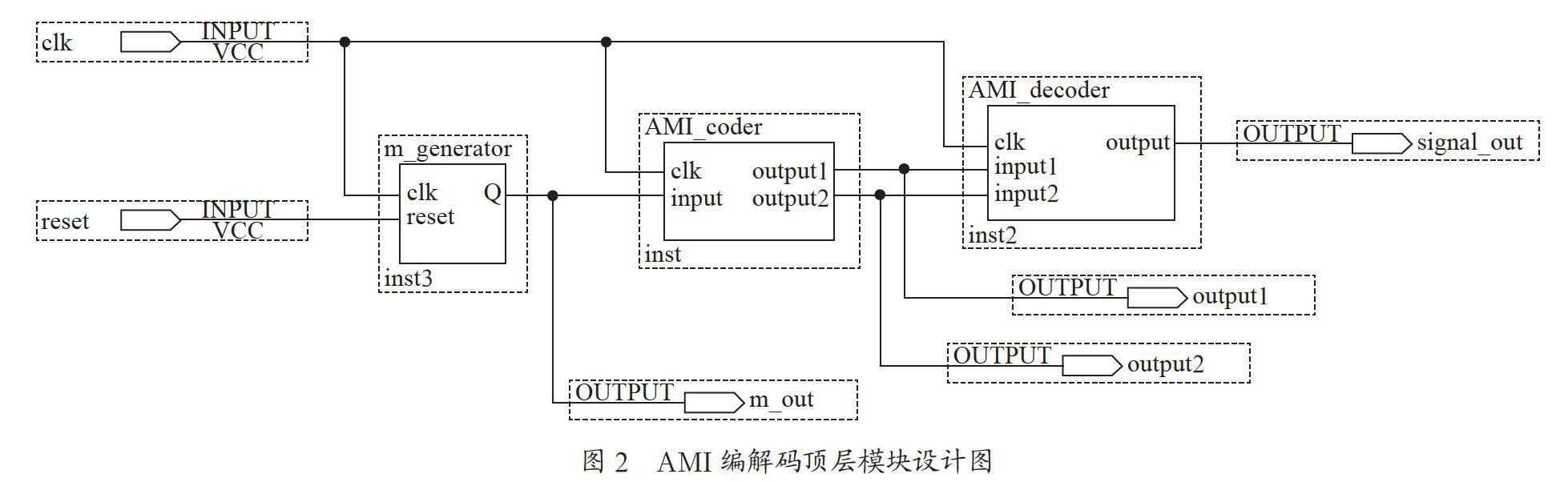

頂層模塊設計圖如圖2所示,頂層設計模塊以Altera公司旗下的Quartus Ⅱ軟件作為開發平臺;采用的FPGA芯片為Cyclone Ⅱ:EP2C35F672C6,該芯片工作電壓低,適應溫度范圍大,邏輯數組塊數量多,可實現高集成度,高速的邏輯運算;各個模塊的設計語言為VHDL語言,將各模塊設計完成后生成bsf文件,將各模塊的bsf文件搭建構成了AMI編解碼的頂層模塊。頂層模塊輸入為時鐘信號clk和復位信號reset;輸出為M序列發生器輸出m_out、編碼模塊兩路輸出output1,output2、譯碼模塊輸出signal_out。

M序列發生器模塊:偽隨機序列用的是M序列作為基波信號,特征多項式為1+X3+X4,產生了周期為15的偽隨機序列;M序列發生器產生偽隨機序列在受復位信號reset控制,當復位信號為低電平時,開始產生偽隨機序列。

AMI編碼器模塊:輸入信號為M序列信號m_out和時鐘信號clk,輸出為兩路輸出信號output1和output2,規定輸出“1”“0”為AMI碼中的“+1”,輸出“0”“1”為AMI碼中的“-1”。當“1”進入AMI編碼器時,兩路輸出信號“0”“1”交替變換輸出;當信號為“0”時,輸出信號都為“0”;兩路輸出信號都在時鐘上升沿處發生變化。

AMI譯碼器模塊:輸入信號為AMI編碼器輸出的兩路信號,由編碼器的設計思路,將兩路信號相或的值輸出,如果輸入的兩路信號是“0”“1”或者“1”“0”時,相或的結果為“1”;如果兩路信號都為“0”時,相或結果為也“0”。由此就能得到編碼前的原M序列信號signal_out。

2.1? 偽隨機序列發生器設計

產生M序列的原理圖如圖3所示,產生的M序列碼滿足特征關系式1+X3+X4。每個時鐘上升沿到達,在復位信號為高電平時復位,輸出為高電平;在復位信號為低電平,每個時鐘上升沿到達時,各個寄存器依次移位,每次將a0與a1的值相或賦給a4,并輸出a0。

2.2? AMI編碼模塊

如圖4所示,是AMI編碼模塊的流程圖,初始狀態下c為“0”。AMI編碼方式是先判斷輸入的M碼為“1”還是“0”;如果是“1”且c=“0”則兩路輸出信號交替“0”,“1”輸出;如果M碼是“0”且c=“1”,則兩路信號均輸出“0”。c為標志位,當每次輸出為1時,無論輸出是‘1‘0,還是‘0‘1,標志位c都取反。

代碼實現如下:

if input='1' then

if c='0' then ? ? ? ? ? ? ? ? ? ? ? ? ?--初始標志位c為0

output1 <='1';

output2<='0'; ? ? ? ? ? ? ? ? ? ? ? ? ?--“10”為“+1電平”

c:=not c; ? ? ? ? ? ? ? ? ? ? ? ? ?--交替變換信號

else

output1<='0';

output2<='1'; ? ? ? ? ?--“01”為“-1”電平

c:=not c; ? ? ? ? ? ? ? ? ? ? ? ? ?--交替變換信號

end if;

else

output1<='0';

output2<='0'; ? ? ? ? ? ? ? ? ?--“00”時為“0”電平

end if;

end if;

2.3? 譯碼模塊

AMI譯碼模塊較簡單,這里不再給出流程圖,將兩路輸入input1和input2相或輸出,當輸入是“01”或者是“10”時,相或的結果為“1”,當輸入是“00”時,相或結果為“0”。代碼實現為:

begin

if clk'event and clk='0' then? ? ? ? ?----時鐘上升沿到達

output<=input1 or input2;? ? ? ?----將兩路輸入相或輸出

end if;

3? 仿真結果與分析

利用Quartus Ⅱ作為編譯設計軟件,設計結果在ModelSim上進行仿真。對AMI編解碼頂層模塊進行仿真,仿真結果如圖5所示。在測試文件testbench中,設置時鐘周期為20 ns,且時鐘初始時刻為0;設置復位信號reset初始為高電平,持續100 ns后變為低電平。

由頂層模塊仿真波形圖可以看出,復位信號reset=1時,產生的M序列信號為1;在100 ns時,復位信號reset=0,M序列輸出為1,此時剛好是時鐘上升沿,電路開始編碼,輸出的引腳output1和output2信號依次“0”,“1”變換,符合編碼規則;在下一個時鐘上升沿到來時,開始譯碼,此時輸出的波形是signal_out,等于output1和output2信號的相或,輸出為高電平,符合譯碼規則。輸出的m_out在第一個時鐘上升沿開始編碼,然后再經過一個時鐘上升沿開始譯碼輸出,所以m_out信號與signal_out信號相差兩個時鐘上升沿。之后的output1和output2也符合AMI編碼規則,譯碼后的signal_out信號也與m_out信號一致,符合預期設計。

4? 結? 論

本次設計基于Altera公司的Quartus Ⅱ軟件開發平臺和ModelSim仿真實驗平臺,使用FPGA器件EP2C35F672C6芯片,利用VHDL硬件描述語言完成了AMI編解碼電路的設計與仿真。AMI編碼確定的基帶信號無直流分量,且低頻分量很小,使得調制與解調的誤碼率大大減小;AMI碼還具有檢錯能力,如果因為極性交替使得傳輸過程中出現了誤碼情況,很容易檢查出這種錯誤,如果若碼元極性與發端相反,收端也能正確接收,AMI碼為信號傳輸過程提供了可靠的方式。運用FPGA來實現AMI碼,與采用專用集成電路相比較,前者不僅給調試帶來方便,而且可以把編解碼電路以及其他輔助電路集成在同一塊FPGA芯片中,減少了外界元件,提高了集成度,具有很大的編程靈活性。

參考文獻:

[1] 顧涵.基于FPGA的類曼徹斯特編碼發送模塊設計 [J].科技傳播,2014,6(4):209-210.

[2] 李永軍,田亞芳,徐曉蓉,等.基帶傳輸系統中AMI碼性能分析與仿真 [J].河南大學學報(自然科學版),2012,42(2):203-207.

[3] 謝維華,庹新宇,楊瑞娟.一種用VHDL語言實現的幀同步算法 [J].空軍雷達學院學報,2003(2):17-19.

[4] 綦曉華.基于FPGA的數字視頻監控系統的研究與設計 [D].武漢:武漢理工大學,2009.

[5] 吳成靜.模擬信號在光纖中的傳輸方案研究 [D].西安:西安工業大學,2015.

[6] 孔利東.基于FPGA的數據采集與處理技術的研究 [D].武漢:武漢理工大學,2007.

[7] 包晗.FPGA器件的應用研究 [D].大連:大連海事大學,2006.

[8] 李雨璇,任峻.數字基帶系統(AMI碼)的仿真設計與分析 [J].福建電腦,2018,34(4):137-138+5.

[9] 沈媛媛,梁浩.基于FPGA的HDB3編碼器設計與仿真 [J].儀器儀表與分析監測,2012(4):17-19.

作者簡介:左磊(2000—),男,穿青人,貴州畢節人,本科在讀,研究方向:通信工程;程煜洋(2000—),女,漢族,湖北武漢人,本科在讀,研究方向:通信工程;趙曉東(2000—),男,漢族,寧夏石嘴山人,本科在讀,研究方向:通信工程;方圓(1999—),女,漢族,福建福州人,本科在讀,研究方向:通信工程。