GGNMOS ESD器件的建模與仿真

趙 莉

(南京德睿智芯電子科技有限公司,江蘇 南京 210000)

0 引 言

常見的ESD保護結(jié)構(gòu)有二極管、GGNMOS、SCR等結(jié)構(gòu)。其中GGNMOS是ESD保護電路中比較常見的結(jié)構(gòu),它的結(jié)構(gòu)特點是柵極接地的NMOS管,易于實現(xiàn)而且它在ESD大脈沖發(fā)生時能夠泄放掉大部分ESD脈沖電流,保護內(nèi)部電路不受損傷;在沒有ESD大脈沖時,不會影響正常電路的工作[1]。

本文的設(shè)計目標(biāo)是人體模型HBM4 kV,考慮到ESD器件的電壓高、放電時間短、上升時間快等特點,導(dǎo)致很難通過電路模擬出具體的ESD放電情況。通常業(yè)內(nèi)直接的做法是設(shè)計者根據(jù)電路設(shè)計要求和設(shè)計經(jīng)驗進行多次流片測試驗證,但是大量的流片測試與驗證既耗時又費力而且成功率不高,因此急需一種方法可簡化設(shè)計時間與流程,而通過對器件進行模型建立,進而通過軟件進行相應(yīng)的仿真得到器件的性能參數(shù),是一種簡單而有效的方法[2]。

1 GGNMOS器件建模與仿真

1.1 GGNMOS保護器件理論模型

圖1模型建立的目標(biāo)是為了準(zhǔn)確描述GGNMOS ESD器件正常工作時的I-V特性曲線,反映器件的漏端在經(jīng)歷ESD大脈沖時,漏端電流Ids以及襯底電流Isub的變化情況。該物理模型主要由四部分組成,分別為理想NMOS管、寄生LNPN管、襯底電阻Rsub和漏端電阻Rd;另外,圖1中,Ids是NMOS管的漏端電流,Ic是LNPN的集電極電流,Igen是LNPN發(fā)生雪崩擊穿時產(chǎn)生的碰撞電離電流,Ib是LNPN的基極電流,Isub是保護器件的襯底電流。

圖1 GGNMOS保護器件物理模型

1.2 電路仿真等效模型

圖2為仿真用GGNMOS等效電路模型及Spectre仿真結(jié)果。

圖2(a)仿真模型中idbn_model=Igen,rsub_model=Rsub,根據(jù)圖1原理利用PDK中理想器件組合實現(xiàn);理想的NMOS管n33_iso_io_4t調(diào)用的是PDK中理想的元器件,通過探針的調(diào)用方法,實現(xiàn)了id、vd、ids、ic、Igen、Rsub等參數(shù)間互聯(lián)的關(guān)系,模擬出了GGNMOS ESD保護器件寄生LNPN開啟的狀態(tài)。圖2(b)是考慮寄生參數(shù)建模后GGNMOS ESD保護器件I-V特性曲線,其中橫坐標(biāo)Vd是GGNMOS管的漏極電壓,縱坐標(biāo)I是GGNMOS管的取對數(shù)后的漏極電流,V1是GGNMOS管的觸發(fā)電壓Vt,V2是GGNMOS管的維持電壓Vp;該I-V特性曲線清楚地顯示了不同階段的工作區(qū)間即線性區(qū)、飽和區(qū)、雪崩擊穿區(qū)和回滯區(qū)四個區(qū)域。

本文設(shè)計的ESD保護器件使用的是0.18 μm CMOS工藝,電源電壓為3.3 V,設(shè)計窗口為3.63 V<Vp<Vt<Vmax=23.1×90%=20 V;由圖2(b)可知,仿真模型中的ESD保護器件滿足設(shè)計窗口的要求。

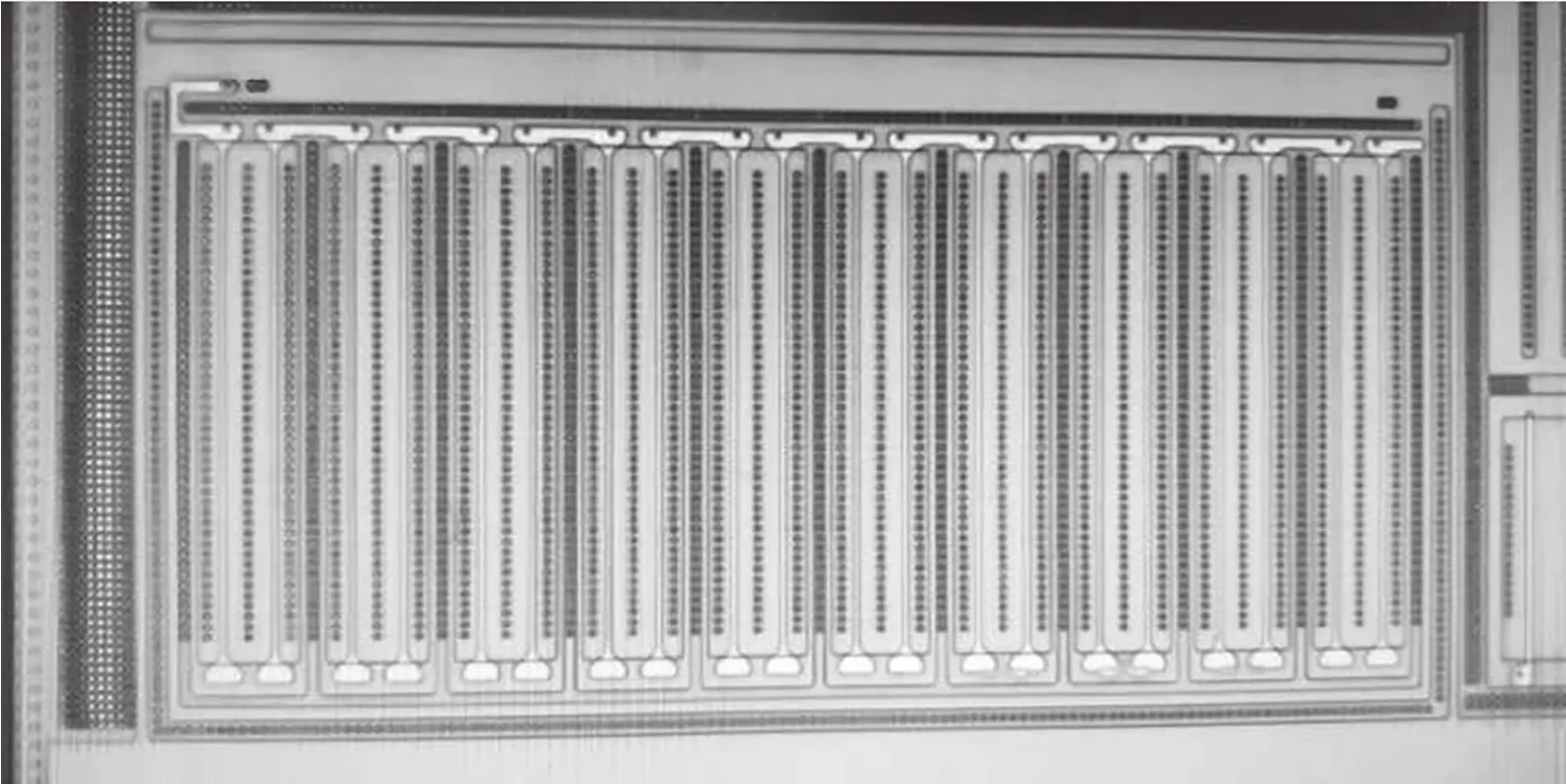

將設(shè)計好的GGNMOS ESD保護器件加到正常電路中,進行電路功能驗證,在正常工作模式下需要驗證GGNMOS ESD保護器件對功能電路是否會有影響;在ESD瞬時大電流脈沖下,驗證GGNMOS ESD保護器件是否起作用。最后,在考慮工藝、電壓及溫度等條件下進行仿真驗證,能夠達到設(shè)計要求時,進行流片驗證!圖3為本文設(shè)計的GGNMOS保護器件的照片。

本文共設(shè)計了10個GGNMOS單體,通過TLP測試發(fā)現(xiàn),有一半GGNMOS單體能夠滿足設(shè)計窗口和防護等級達到4 kV的要求;針對不滿足設(shè)計要求的單體繼續(xù)進行仿真研究,找到具體失效的原因,揚長補短,爭取設(shè)計出性價比最高的GGNMOS保護器件。

圖3 GGNMOS防護器件照片

2 結(jié) 論

本文主要進行了GGNMOS ESD保護器件的模型建立和電路仿真,該方法能夠在流片前對ESD器件的特性進行設(shè)計保證,同時進行電路級等效模型的仿真比利用其他的建模方法如Verilog-A的建模與仿真、TCAD器件仿真等更簡單、更便捷、更實用。