更新六大技術支柱英特爾賦予10nm新含義

張心怡

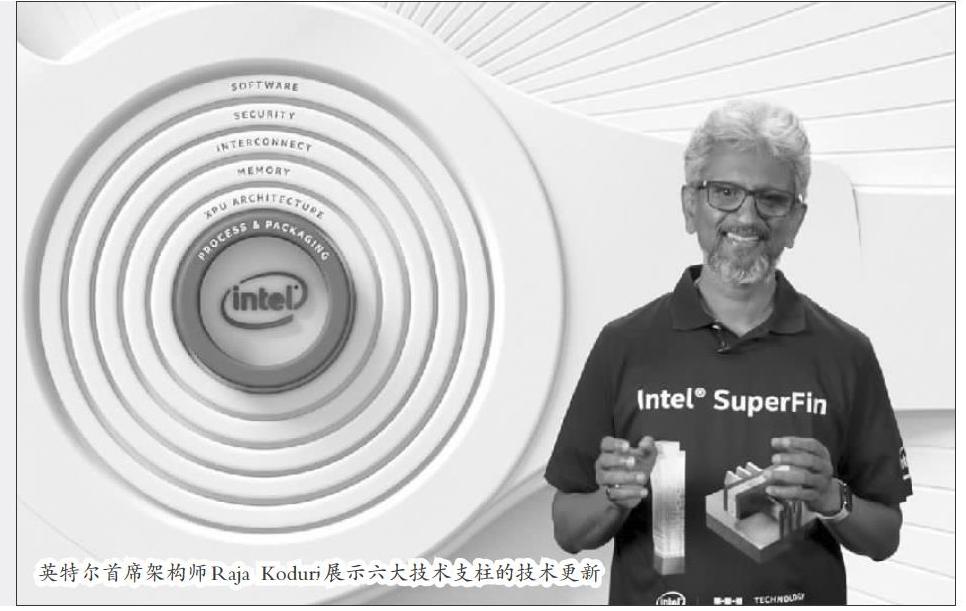

在8月13日舉辦的2020架構日上,,英特爾發布了長達233頁的技術更新,覆蓋制程、封裝、架構、軟件等“六大技術支柱”的方方面面。作為摩爾定律的提出者,英特爾一方面圍繞晶體管密度和性能,推動摩爾定律在10nm以下的發展;另一方面,英特爾正在從晶體管"Reliance(依賴)'走向晶體管"Resilient(彈性)”,通過“六大技術支柱”,推動計算性能在“后摩爾時代”持續增長,并形成了面向異構計算時代的整體交付能力,以更有效地應對智能時代的計算挑戰。

制程工藝并未止步

英特爾提出了“PAO”發展模式,即通過制程、微架構、優化三種方式輪流推動處理器性能的升級。

2007年,英特爾提出了“TickTock”(滴答)發展模式,通過制程演進與微架構更新,輪換推動處理器性能提升。在2016年,英特爾將“TickTock”調整為“PAO",即通過制程、微架構、優化三種方式輪流推動處理器性能的升級。

在架構日上,英特爾發布了Superfin技術。作為FinFet(鰭式場效應晶體管)的增強版本,Superfin屬于“O”的范疇,是針對10nm的晶體管強化工藝。雖然沒有用“10nm+”來命名,但Superfin對于10nm工藝的提升超過15%,包括更高的驅動電流、通道遷移率,以及更好的芯片互聯性等。

英特爾院士RuthBrain表示,Super-fin實現了英特爾史上最強大的單節點內性能增強,其提升程度可媲美全節點轉換。

在10nmSuperfin之后,英特爾還將推出10nm增強型Superfin技術,進一步提升芯片性能和互聯能力,并針對數據中心場景進行進一步的優化。

1OnmSuperfin的性能將達到何種程度,也引起了業內的廣泛討論。隨著制程進入14nm以內,摩爾定律的實現越來越難,逐漸逼近物理極限。即便晶體管密度提升幅度不足一倍,也冠以新的制程節點,已經成為許多代工廠商的選擇,這也讓節點命名越來越具備市場營銷的色彩。

但是,在10nm及以下,英特爾仍在遵循摩爾定律的硬性指標。其10nm節點的晶體管密度達到每平方毫米內包含超過1億個晶體管,是14nm節點的2.7倍。在晶體管密度、鰭片間距、柵極間距等指標上,英特爾10nm已經超過了臺積電、三星的7nm制程。

如果Superfin的性能,能堪比全節點的轉換,那么在10nm指標能夠對標友商7nm的基礎上,Superfin能否對標友商7nm工藝的增強版甚至更先進的工藝節點,不免令人浮想聯翩。當然,制程工藝的先進性必須在產品中得到驗證。英特爾的下一代處理器TigerLake(“虎湖”),將成為首個采用10nmSuperfin的處理器。目前該處理器已經投產,預計OEM采用Ti一gerLake設計的產品將在今年之內上市。而10nm增強型技術,也將在下一代至強可擴展處理器中得到驗證。

從晶體管“依賴”走向晶體管“彈性”

隨著制程微縮逼近極限,如何在“后摩爾時代”延續計算能力指數級增長,成為半導體產業的重要課題。

無論是增加晶體管數量還是提升晶體管性能,都屬于制程工藝的范疇,代表著英特爾繼續追隨摩爾定律的決心。與此同時,隨著制程微縮逼近極限,如何在“后摩爾時代”延續計算能力的指數級增長,成為半導體產業的重要課題。

在架構日上,英特爾首席架構師Raja Koduri提到了“Transistor?Resilient(晶體管彈性)”的概念。簡單來說,這是一一個完全依賴晶體管的產品開發策略,通過架構、封裝、軟件等技術的“組合拳”,實現產品性能的提升。

架構是硬件設計的基礎,對處理器的性能和功耗表現起到決定性作用。本次架構日,英特爾發布了下一代微架構“Wil-low Cove”。為滿足下游客戶的多樣化需求,Willow?Cove提供了更大的動態范圍。相比上一代架構SunnyCove,Wil-low Cove可以用更低的電壓達到同樣的主頻,在提高電壓的情況下,可以達到5GHz左右的最高主頻,滿足創意工作者、游戲愛好者對生產力的不同需求。

同樣在架構日亮相的,還有英特爾的GPU架構Xe,這也是繼1998年推出的i740之后,英特爾再度進軍獨顯市場。Xe提供LP、HP、HPG、HPC四種微架構。LP針對PC和移動計算平臺等功耗敏感場景,擁有96組EU單元,與WillowCove類似,IP可以通過加高電壓獲得1.8GHz甚至更高的主頻,提供更強的輸出功率。

目前,基于LP架構的獨顯產品“DG1”已經實現量產。HP版本面向數據中心級、機架級場景所需的媒體性能,基于英特爾EMIB技術,HP能夠在單封裝中提供千萬億浮點運算規模的AI性能和機架級的媒體性能,首款產品已經向數據中心客戶出樣。HPG面向游戲領域,基于GDDR6的新內存子系統提高性價比,并具備當前熱門的光線跟蹤能力。HPC架構則針對高性能計算領域,滿足大規模的集成部署需要。

硬件能力的釋放,必須基于軟件的通信和調度。在Xe的設計理念中,英特爾強調了“軟件優先”的原則,提升了GPU的編譯和驅動效率,實現了GPU根據用戶配置進行性能優化以及可變頻率著色、即時游戲調整、感知自適應游戲銳化等功能,讓GPU能夠更好地滿足3D、媒體、顯示、計算等不同工作負載的計算需求。

先進封裝向來被視為摩爾定律的“救星”,在不依賴工藝縮小的前提下,先進封裝可以繼續提升芯片的系統集成度。芯片的連接觸電密度、單比特功耗、擴展性,是英特爾發展先進制程的主要指標。目前,英特爾已經形成了2.5D封裝EMIB、3D封裝Foveros,以及混合2D和3D封裝的Co-EMIB等先進封裝方案。在架構日,英特爾發布了“混合結合”技術,能夠加速實現10微米及以下的凸點間距,較Fovreros25-50微米的凸點間距有明顯提升,并優化了互連密度、帶寬和功率表現,進一步提升芯片系統的計算效能。